## IntechOpen

# Integrated Circuits/Microchips

Edited by Kim Ho Yeap and Jonathan Javier Sayago Hoyos

# Integrated Circuits/Microchips

Edited by Kim Ho Yeap and Jonathan Javier Sayago Hoyos

Published in London, United Kingdom

IntechOpen

Supporting open minds since 2005

Integrated Circuits/Microchips http://dx.doi.org/10.5772/intechopen.83313 Edited by Kim Ho Yeap and Jonathan Javier Sayago Hoyos

#### Contributors

Navid Mohammadian, Leszek A. Majewski, Karim Ali, Hao-Li Zhang, Zhi-Ping Fan, Jonathan Sayago, Irina Valitova, Zhihui Yi, Sung Min Park, Daniel Arbet, Viera Stopjakova, Lukas Nagy, Saeed Mian Qaisar, Jiang Cao, Kim Ho Yeap, Siu Hong Loh, Muammar Mohamad Isa

#### © The Editor(s) and the Author(s) 2020

The rights of the editor(s) and the author(s) have been asserted in accordance with the Copyright, Designs and Patents Act 1988. All rights to the book as a whole are reserved by INTECHOPEN LIMITED. The book as a whole (compilation) cannot be reproduced, distributed or used for commercial or non-commercial purposes without INTECHOPEN LIMITED's written permission. Enquiries concerning the use of the book should be directed to INTECHOPEN LIMITED rights and permissions department (permissions@intechopen.com).

Violations are liable to prosecution under the governing Copyright Law.

Individual chapters of this publication are distributed under the terms of the Creative Commons Attribution 3.0 Unported License which permits commercial use, distribution and reproduction of the individual chapters, provided the original author(s) and source publication are appropriately acknowledged. If so indicated, certain images may not be included under the Creative Commons license. In such cases users will need to obtain permission from the license holder to reproduce the material. More details and guidelines concerning content reuse and adaptation can be found at http://www.intechopen.com/copyright-policy.html.

#### Notice

Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published chapters. The publisher assumes no responsibility for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained in the book.

First published in London, United Kingdom, 2020 by IntechOpen IntechOpen is the global imprint of INTECHOPEN LIMITED, registered in England and Wales, registration number: 11086078, 5 Princes Gate Court, London, SW7 2QJ, United Kingdom Printed in Croatia

British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library

Additional hard and PDF copies can be obtained from orders@intechopen.com

Integrated Circuits/Microchips

Edited by Kim Ho Yeap and Jonathan Javier Sayago Hoyos

p. cm.

Print ISBN 978-1-78985-930-0

Online ISBN 978-1-83968-461-6

eBook (PDF) ISBN 978-1-83968-462-3

# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

5,000+ 125,000+ 140

Open access books available

International authors and editors

Countries delivered to

Our authors are among the

lop 1%

12.2%

Contributors from top 500 universities

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

> Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

### Meet the editors

Kim Ho Yeap is an Associate Professor at Universiti Tunku Abdul Rahman, Malaysia. He is an IEEE senior member, a Professional Engineer registered with the Board of Engineers, Malaysia, and a Chartered Engineer registered with the UK Engineering Council. He received his BEng (Hons) Electrical and Electronics Engineering from Universiti Teknologi Petronas in 2004, his MSc in microelectronics from Universiti Kebangsaan Malaysia in 2005,

and his PhD from Universiti Tunku Abdul Rahman in 2011. In 2008 and 2015, respectively, Dr. Yeap underwent research attachment at the University of Oxford (UK) and Nippon Institute of Technology (Japan). Dr. Yeap is the external examiner and external course assessor of Wawasan Open University. He is also the Editor in Chief of the i-manager's Journal on Digital Signal Processing. He has also been a guest editor for the Journal of Applied Environmental and Biological Sciences and Journal of Fundamental and Applied Sciences. Dr. Yeap has been given the university teaching excellence award, and 20 research grants. He has published more than 100 research articles (including refereed journal papers, conference proceedings, books, and book chapters). When working in Intel corporation, Dr. Yeap was a design engineer in the pre-silicon validation group. He was awarded 4 Kudos awards by Intel for his contributions in the design and verification of the microchip's design for testability (DFT) features.

Jonathan Javier Sayago Hoyos is a research associate at the National Autonomous University of Mexico. During his doctoral studies, Dr. Sayago tackled the problem of achieving low-voltage organic transistors employing electrolytes as the gating medium. His research contributed to shedding light on fundamental physicochemical processes in electrochemical transistors and energy storage devices. After his PhD studies, Dr. Sayago worked

as a consultant for Bowhead Health Inc., a Canadian startup company aiming for the commercialization of bioelectronic devices for preventive medical applications. His team designed and built a biosensor device capable of testing 50  $\mu l$  of blood which led the company to secure a private funding from the world-class Mexican company Grupo Arcoiris. As a Postdoctoral Researcher at the Institute of Renewable Energies, UNAM, Dr. Sayago investigates biocompatible and biodegradable electrodes engineered for energy storage and heat transfer applications. Derived from this work he authored and co-authored over 10 articles in highly recognized international journals, 3 book chapters and participated in numerous international conferences and workshops. Dr. Sayago has taught courses in mathematics, advanced physics laboratory, computer assisted design and 3D printing, and tutoring sessions. He is an active reviewer for the Journal of Power Sources.

## Contents

| Preface                                                                                                                                             | XII |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Section 1 Introduction to Microchips                                                                                                                | 1   |

| <b>Chapter 1</b><br>Introductory Chapter: Integrated Circuit Chip<br>by Kim Ho Yeap, Muammar Mohamad Isa and Siu Hong Loh                           | 3   |

| Section 2 Microchip Design Methods                                                                                                                  | 17  |

| <b>Chapter 2</b><br>Ultra-Low-Voltage IC Design Methods<br>by Daniel Arbet, Lukas Nagy and Viera Stopjakova                                         | 19  |

| Section 3 Tunnel Field Effect Transistors                                                                                                           | 43  |

| <b>Chapter 3</b> Tunnel Field Effect Transistors Based on Two-Dimensional Material Van-der-Waals Heterostructures by Jiang Cao                      | 45  |

| Section 4 Organic Field Effect Transistors                                                                                                          | 63  |

| <b>Chapter 4</b> Crystal Polymorph Control for High-Performance Organic Field-Effect Transistors by Zhi-Ping Fan and Hao-Li Zhang                   | 65  |

| Chapter 5 High Capacitance Dielectrics for Low Voltage Operated OFETs by Navid Mohammadian and Leszek A. Majewski                                   | 87  |

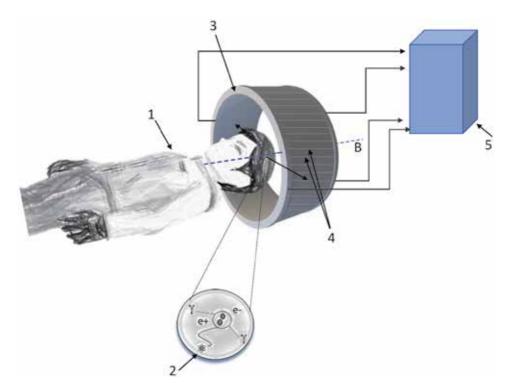

| Chapter 6 Tackling the Problem of Dangerous Radiation Levels with Organic Field-Effect Transistors by Irina Valitova, Zhihui Yi and Jonathan Sayago | 111 |

| Section 5                                                                                                                      |     |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| The Applications of Microchips                                                                                                 | 127 |

| Chapter 7 CMOS Integrated Circuits for Various Optical Applications by Sung Min Park                                           | 129 |

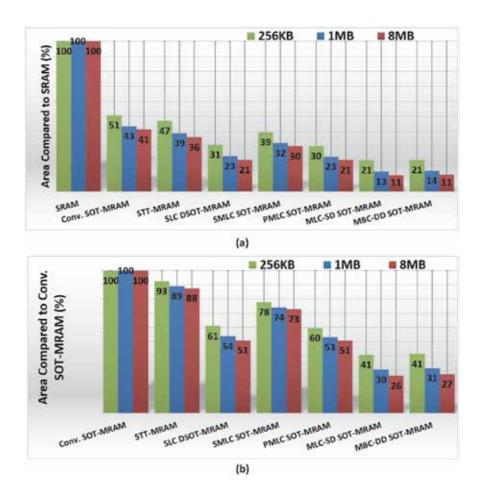

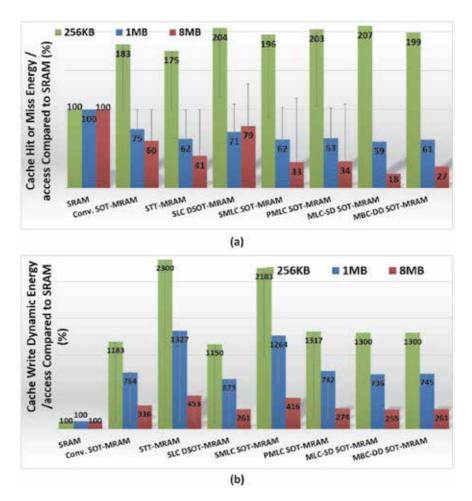

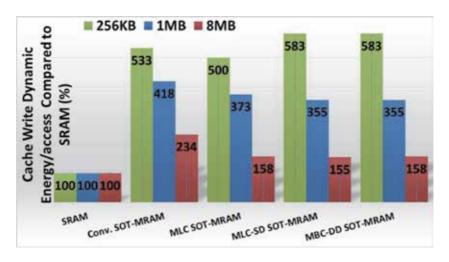

| Chapter 8 Area-Efficient Spin-Orbit Torque Magnetic Random-Access Memory by Karim Ali                                          | 151 |

| Chapter 9 Computationally Efficient Hybrid Interpolation and Baseline Restoration of the Brain-PET Pulses by Saeed Mian Qaisar | 173 |

## **Preface**

With the world marching inexorably towards the fourth industrial revolution (IR 4.0), one is now embracing lives with artificial intelligence (AI), the Internet of Things (IoTs), virtual reality (VR) and 5G technology. Wherever we are, whatever we are doing, there are electronic devices that we rely indispensably on. While some of these technologies, such as those fueled with smart, autonomous systems, are seemingly precocious; others have existed for quite a while. These devices range from simple home appliances, entertainment media to complex aeronautical instruments. Clearly, the daily lives of mankind today are interwoven seamlessly with electronics.

Surprising as it may seem, the cornerstone that empowers these electronic devices is nothing more than a mere diminutive semiconductor cube block. More colloquially referred to as the Very-Large-Scale-Integration (VLSI) chip or an integrated circuit (IC) chip or simply a microchip, this semiconductor cube block, approximately the size of a grain of rice, is composed of millions to billions of transistors. The transistors are interconnected in such a way that allows electrical circuitries for certain applications to be realized. Some of these chips serve specific permanent applications and are known as Application Specific Integrated Circuits (ASICS); while others are computing processors that can be programmed for diverse applications. The computer processor, together with its supporting hardware and user interfaces, is known as an embedded system.

In this book, a variety of topics related to microchips are extensively illustrated. The topics encompass the physics of operation of the microchip device, as well as its design methods and applications.

Chapter 1 presents an overview of microchips. In order to allow readers to appreciate the efforts researchers have sacrificed to arrive at the cutting-edge technology that we savor today, the historical development of microchips and its fundamental building block, i.e. the transistor, is first illustrated. This is then followed by a brief explanation of Moore's law – the law that governs the technological progression of microchips. A brief introduction to the field effect transistor – particularly the MOSFET, its operational principle, and the precipitating factors that necessitate the evolution of the planar MOSFETs to the three-dimensional FinFETs is also covered. At the end of the chapter, a walkthrough of the chip fabrication process is succinctly described.

In Chapter 2, an overview of the main challenges and design techniques for ultralow voltage and low-power analog integrated circuits in nanoscale technologies is illustrated. New design challenges and limitations linked to achieving low voltage operation, low process fluctuation, low device mismatch, and other effects are discussed. In the later part of the chapter, conventional and unconventional design techniques (bulk-driven approach, floating-gate, dynamic threshold, etc.) to design analog integrated circuits towards ultra-low voltage systems and applications are described. Examples of ultra-low voltage analog microchip blocks (such as an operational amplifier, a voltage comparator, a charge pump, etc.) designed in a standard CMOS technology but with an unconventional design approach, are also given.

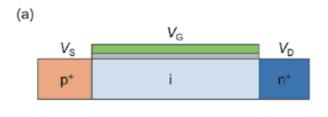

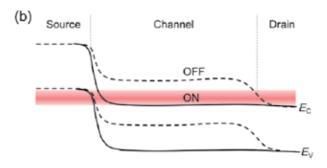

Chapter 3 describes the recent progresses in the tunnel field effect transistors based on 2-D TMD van-der-Waals heterostructure. The chapter covers the theoretical and computational efforts to understand the working mechanism and the limiting factors in these devices. It also sheds light on the design challenges to be addressed for the development of efficient tunnel field-effect transistors based on 2-D material van-der-Waals heterostructures.

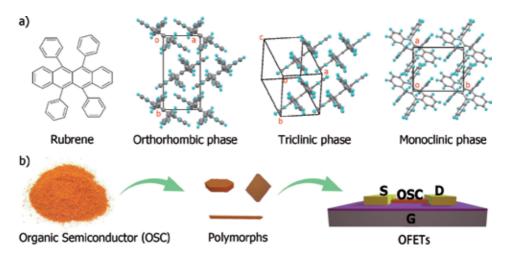

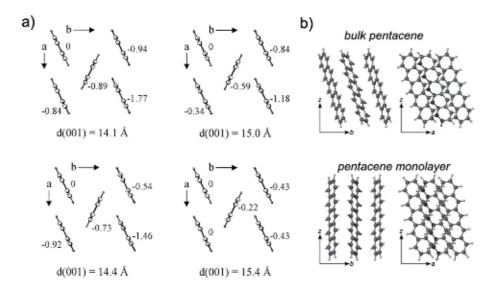

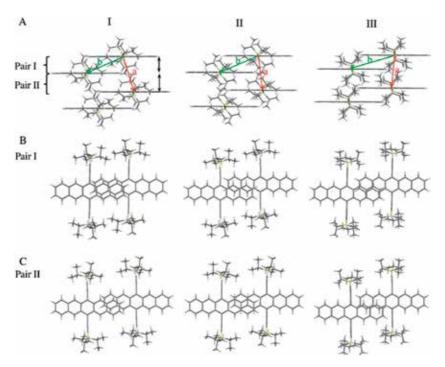

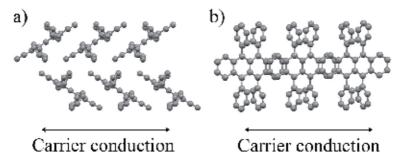

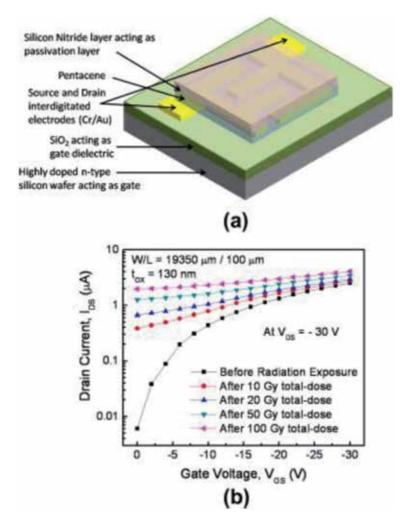

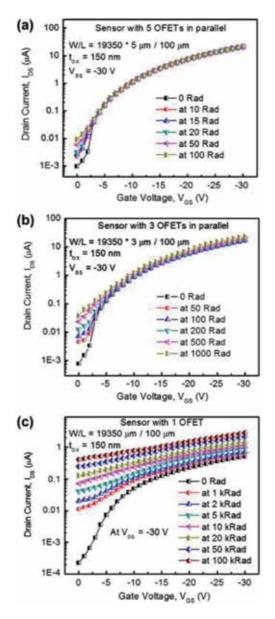

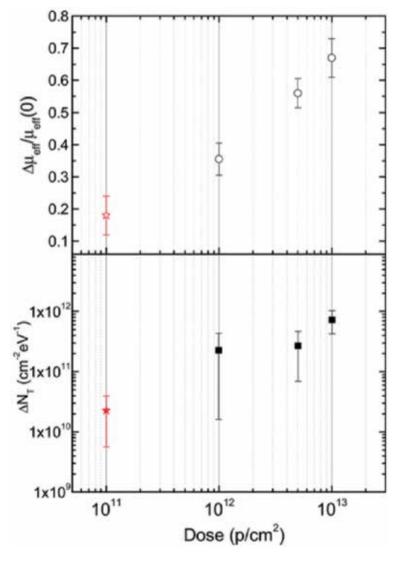

In order to support and promote low-cost and bio-degradable electronics, organic field effect transistors (OFETs) have been introduced. Chapters 4 to 6 present a detailed elaboration on various topics related to OFETs. Since multiple crystalline packing states (crystal polymorphism) exist in the active layer of OFETs, a review on crystal polymorph control is given in Chapter 4. One way to minimize the threshold voltage of an OFET is to reduce the gate dielectric thickness. Chapter 5 discusses some of the most promising strategies towards high capacitance dielectrics for low voltage OFETs. Since OFETs are capable of providing tissue equivalent response to ionizing radiation, Chapter 6 presents the possibility of using different types of OFETs as ionizing and X-ray radiation dosimeters in medical applications.

Chapters 7 to 9 describe some of the recent applications of microchips. Chapter 7 presents several CMOS microchips realized for various optical applications, such as high-definition multimedia interface (HDMI), light detection and ranging (LiDAR), and gigabit Ethernet (GbE). Chapter 8 explains spin-orbit torque magnetic random-access memory (SOT-MRAM) and how it is used to realize reliable, high speed, and energy-efficient on-chip memory. Both non-diode-based SOT-MRAM and diode-based SOT-MRAM cells are discussed in this chapter. The final chapter, Chapter 9, describes the design of a novel offset compensated digital baseline restorer (BLR) and a hybrid interpolator. The behavior of the devices is configured using Very High-Speed Integrated Circuits Hardware Description Language (VHDL) and validated on a Field Programmable Gate Array (FPGA).

#### Kim Ho Yeap

Associate Professor,

Department of Electronic Engineering,

Faculty of Engineering and Green Technology,

Universiti Tunku Abdul Rahman,

Malaysia

#### Jonathan Javier Sayago Hoyos

Postdoctoral Researcher, Instituto de Energías Renovables, Universidad Nacional Autónoma de México, México

# Section 1 Introduction to Microchips

#### Chapter 1

# Introductory Chapter: Integrated Circuit Chip

Kim Ho Yeap, Muammar Mohamad Isa and Siu Hong Loh

#### 1. Introduction

The technological advancement of integrated circuit chips (or colloquially referred to as an IC, a chip, or a microchip) has progressed in leaps and bounds. In the span of less than half a century, the number of transistors that can be fabricated in a chip and the speed of which have increased close to 500 and 5000 times, respectively. Back in the old days, about five decades ago, the number of transistors found in a chip was, even at its highest count, less than 5000. Take, for example, the first and second commercial microprocessors developed in 1971 and 1972. Fabricated in the largescale integration (LSI) era, the Intel 4004 4-bit microprocessor comprised merely 2300 transistors and operated with a maximum clock rate of 740 kHz. Similarly, the Intel 8008 8-bit microprocessor released immediately a year later after its 4-bit counterpart comprised merely 3500 transistors in it and operated with a 800 kHz maximum clock rate. Both these two microprocessors were developed using transistors with 10 µm feature size. Today, the number of transistors in a very large-scale integration (VLSI) (or some prefer to call it the giant large-scale integration [GLSI]) chip can possibly reach 10 billion, with a feature size less than 10 nm and a clock rate of about 5 GHz. In April 2019, two of the world's largest semiconductor foundries— Taiwan Semiconductor Manufacturing Company Limited (TSMC) and Samsung Foundry—announced their success in reaching the 5 nm technology node, propelling the miniaturization of transistors one step further to an all new bleeding edge [1]. According to the announcement made in the IEEE International Electron Devices Meeting in San Francisco, the TSMC's 5 nm chip would be produced in high volume in the first half of 2020 [2, 3]. TSMC has also started work on their 3 nm nodes [3].

There is little doubt that the electronics world has experienced a quantum leap in its technology for the past 50 years or so and this, to a large extent, is due to the rapid improvement in the performance, power, area, cost and "time to market" of an IC chip. This chapter provides a succinct illustration on the historical evolution of the IC chip, a general overview of the fundamental building block of the chip—the field-effect transistors, and a brief description of the IC design process.

#### 2. A brief history

The thermionic triode was regarded as the predecessor of transistors that are prevalently used to build electronic devices today. Being invented in 1907, the triodes were made of vacuum tubes which were relatively large in size and were naturally cumbersome to be used. In December 1947, however, three physicists working in the AT&T Bell Laboratories— Dr. Walter Houser Brattain, Dr. John Bardeen and Dr. William Bradford Shockley, Jr.—achieved a remarkable scientific

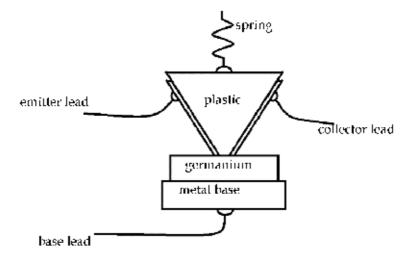

breakthrough when they successfully constructed the solid-state equivalence of the thermionic triode, i.e. the first point-contact germanium transistor. As can be seen in **Figure 1**, the solid-state transistor that they developed consisted of an n-type germanium crystal block and two layers of gold foils placed in close proximity with each other. The foils acted as the contacts of the transistor. Together with the contact at the base, the transistor had a total of three contacts—which were named the emitter, collector and base contacts. When a small current was applied to the emitter contact, the output current at the emitter and base contacts would be amplified [4, 5].

In comparison with its predecessor, the solid-state transistor was diminutive in size. It also consumed much lower power, operated at relatively lower temperature and gave significantly faster response time. It is therefore apparent that the semiconductor transistor is more superior to its conventional vacuum tube brethren. Owing to its advantages and viability, the vacuum tubes were eventually replaced by the solid-state electronic devices. The inexorable widespread usage of the semiconductor transistors in electronic circuits has triggered a dramatic revolution in the electronic industries, kicking off the era of semiconductor. Because of this significant contribution, Bardeen, Brattain and Shockley were awarded the Nobel Prize in Physics in 1956 [4].

It is worthwhile noting that, when the solid-state device was first introduced, it was not coined the term "transistor." Instead, it was generally referred to as the "semiconductor triode." According to the "Memorandum for File" published by the Bell Telephone Laboratories (BTL) [6], six names had been proposed for the device—namely, "semiconductor triode," "surface states triode," "crystal triode," "solid triode," "iotatron" and "transistor." The word "transistor" (which originates from the abbreviated combinations of the words "transconductance" and "varistor") proposed by Dr. John Robinson Pierce of BTL had ultimately turned out to be the winner of the internal poll [6].

The first silicon transistor was developed by Dr. Morris Tanenbaum of BTL in January 1954, whereas the first batch of commercially available silicon transistors were manufactured by Dr. Gordon Kidd Teal of Texas Instruments (TI) in the same year. In 1955, the first diffused silicon transistor made its appearance. To reduce the resistivity of the collector, the transistor with an epitaxial layer

**Figure 1.**An early model of the point-contact transistor.

deposited onto it was developed in 1960. In the same year, the planar transistor was proposed by Dr. Jean Amedee Hoerni [4, 7].

In 1958, Jack St. Clair Kilby, who was then an engineer in TI, successfully developed the first integrated circuit (IC). The device was just a simple 0.5 inch germanium bar, with a transistor, a capacitor and three resistors connected together using fine platinum wires. About half a year later in 1959, Dr. Robert Norton Noyce from Fairchild Camera (also one of the cofounders of Intel Corporation) invented independently his own IC chip. The interconnection in Noyce's 4 inch silicon wafer was realized by means of etching the aluminum film which was first deposited onto a layer of oxide [7]. Both Kilby and Noyce shared the patent right for the invention of the integrated circuit. In 2000, Kilby was awarded the Nobel Prize in Physics "for his part in the invention of the integrated circuit."

The first-generation computers were made of vacuum tubes. Conceived in 1937, the Atanasoff-Berry computer (ABC) (which was generally regarded as the first computer by many) and the Electronic Numerical Integrator and Computer (ENIAC) (which was credited as the first general purpose computer) built in late 1945 belong to the first-generation computers. The vacuum tube triode was swiftly replaced by the solid-state transistor since its advent in 1947. The secondgeneration computers were therefore made of transistors. The prototype computer built at the University of Manchester in November 1953 was widely regarded as the first transistor computer. Like the first transistor computer, most other electronic devices built before 1960 were actually based on germanium transistors. Although silicon transistors had already been developed in the mid-1950s, design engineers were more prone to using germanium than silicon. This is because the technology of germanium devices was very well established at that time and the reliability and yields of the silicon transistor were nowhere close to its germanium brethren [8]. Also, germanium switching diodes exhibited lower threshold voltage than silicon devices, allowing electronic devices made from germanium to be switched on at lower voltage drops [8]. The normal operating temperature of germanium devices, however, did not exceed 70°C, whereas silicon devices could operate well beyond 125°C. Hence, silicon was only used by the military establishment at that time for applications which were to operate at high temperature [8]. Besides its tenacity in withstanding temperature, silicon is also found to have lower leakage voltage and higher thermal conductivity than germanium [8]. These, however, were not the precipitating factors for silicon to replace germanium. It was the development of the oxide masking technique by Carl John Frosch and Lincoln Derick of BTL in 1955 which marked the pivoting point for the role played between silicon and germanium. Researchers found that an oxide film could be easily grown on the surface of a silicon substrate, but attempts to grow a stable oxide layer onto the germanium surface ended in total dismay [8]. BTL ceased meaningful research on germanium since then, and by the end of 1960, most of the electronic devices have been dominated by silicon. During these 5 years, researchers achieved several major technological innovations with the applications of the oxide films—some of which include the fabrication of the monolithic integrated circuit and the invention of the metal oxide semiconductor field-effect transistor (MOSFET) [8]. These innovations reinforce the status of silicon as the key element in electronic devices. In 1961, the first computer made from silicon IC chips was dedicated to the US Air Force.

Since the advent of the solid-state transistor and the demonstration on the workability of the IC chip about some 70 years ago, the electronic industries have been prospering hitherto. IC chips are now closely interwoven with human's life. They have, in many aspects, become indispensable to mankind. Indeed, one can easily

find traces of IC chips intermingle into areas which intertwine seamlessly with the fabric of mankind's living hood. Some of these areas include transportation, telecommunication, security, medicine and entertainment, just to name a few.

#### 3. Moore's law

In the article published in April 1965, one of the cofounders of Intel Corporation, Dr. Gordon Earle Moore, predicted that the number of electronic components (which include not just transistors but capacitors, resistors, inductors, diodes, etc. as well) in an IC chip would double every year [9]. Ten years later, Moore revised his prediction to a doubling of every 2 years. Moore's prediction, which is more commonly known as Moore's law nowadays, has been widely used by the IC manufacturers as a tool to predict the increase of components in a chip for the coming generations [10]. To date, Moore's law has been proven to have held valid for close to half a century. Table 1 tabulates the progressive trend of the integration level for the semiconductor industry. It can be observed from the table that the number of transistors that can be fabricated in a chip has been growing continuously over the years. In fact, this growth has been in close agreement with Moore's law. In order to highlight the technological advancement in the IC industries, each decade since the inception of the semiconductor transistor has been earmarked as a different era. Eight eras have existed hitherto—they are the small-scale integration (SSI), medium-scale integration (MSI), large-scale integration (LSI), very large-scale integration (VLSI), ultra-large-scale integration (ULSI), super largescale integration (SLSI), extra-large-scale integration (ELSI) and giant large-scale integration (GLSI) eras. During the VLSI era, a microprocessor was fabricated for the first time into a single IC chip. Although this era has now long passed, the VLSI term is still being commonly coined today. This is partly due to the absence of a significant qualitative leap between VLSI and its subsequent eras, and partly, it is also because IC engineers have been so used to this term; they decided to continue adopting it.

| Year                        | Number of transistors in a chip                                                                                                                                                                          |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Late 1940s to late<br>1950s | Less than 100                                                                                                                                                                                            |

| Late 1950s to late<br>1960s | Between 100 and 1000                                                                                                                                                                                     |

| Late 1960s to late<br>1970s | Between 1000 and 10,000                                                                                                                                                                                  |

| Late 1970s to late<br>1980s | Between 10,000 and 100,000                                                                                                                                                                               |

| Late 1980s to late<br>1990s | Between 100,000 and 1000,000                                                                                                                                                                             |

| Late 1990s to late<br>2000s | Between 1000,000 and 10,000,000                                                                                                                                                                          |

| Late 2000s to late<br>2010s | Between 10,000,000 and 100,000,000                                                                                                                                                                       |

| Late 2010s to late<br>2020s | More than 100,000,000                                                                                                                                                                                    |

|                             | Late 1940s to late 1950s  Late 1950s to late 1960s  Late 1960s to late 1970s  Late 1970s to late 1980s  Late 1980s to late 1990s  Late 1990s to late 2000s  Late 2000s to late 2010s  Late 2010s to late |

Table 1.

Integration level of an integrated circuit chip.

#### 4. The field-effect transistors

Today, the transistors fabricated in an IC chip are mostly MOSFETs. The earliest paper describing the operation principle of a MOSFET can be traced back to that reported in Julius Edgar Lilienfeld's patent in 1933 [11]. Unfortunately, the technology at that time was inadequate to allow Lilienfeld's idea to be physically materialized. In 1959, Dr. Dawon Kahng and Dr. Martin M. (John) Atalla at the BTL successfully constructed the MOSFET [12]. In 1963, two engineers from the Radio Corporation of America (RCA) Princeton laboratory, Dr. Steven R. Hofstein and Dr. Frederic P. Heiman, presented the theoretical description on the fundamental nature of the silicon planar MOSFET [13]. In the same year, Dr. Tom Chih-Tang Sah and Dr. Frank Marion Wanlass of Fairchild Semiconductor invented the first complementary metal oxide semiconductor (CMOS) logic circuit [14]. In 1989, Dr. Digh Hisamoto and his team member at Hitachi Central Research Laboratory introduced the fin field-effect transistor or better known as the FinFET—a nonplanar MOSFET modified from its planar counterpart. Although the FinFET was found to possess various advantages over the planar MOSFET, it was not adopted by the industries then. This was partly due to the difficulty in fabricating its threedimensional structure and, partly, also because the planar MOSFETs still had plenty of rooms to be improved further. Having realized that the planar MOSFET was gradually approaching its bottleneck in its technological advancement, chipmakers started to resort to FinFETs in the fabrication of high-end electronic devices (such as microprocessors) in 2011.

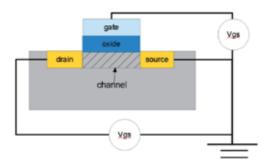

#### 4.1 The MOSFET

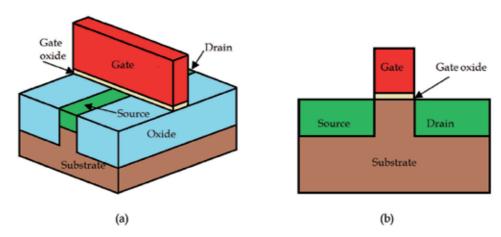

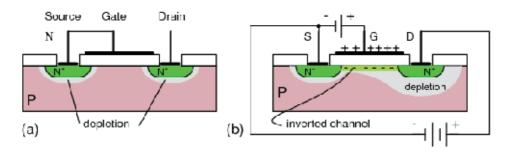

The MOSFET is nothing more than a device which operates as an electronic switch. Figure 2 shows the basic structure of the MOSFET. The transistor comprises four terminals, namely, the drain (D), source (S), gate (G) and substrate or body (*B*) terminals. As can be clearly seen from the figure, the device constitutes three layers—a polysilicon layer (which forms the gate terminal), an oxide layer (known the gate oxide) and a single-crystal semiconductor layer (known as the substrate). In the early days, the gate terminal was made of aluminum. It is from these three layers of materials that the FET device acquired its name. In the mid-1970s, however, the gate material was replaced with polysilicon. When ion implantation was introduced to form the self-aligned source and drain terminals in the 1970s, a hightemperature (higher than 1000°C) annealing process was required to repair the damaged crystal structure at the surface of the substrate, as a result of the energetic dopant ion bombardment and to activate the dopant [15]. IC engineers observed that the aluminum gate melted during the annealing process. This is because aluminum has a melting point of about 660.3°C. In order to overcome this problem, polysilicon which has a melting point of about 1414°C was employed as the replacement for gate material. Although the gate today is no longer made of aluminum, the term MOSFET has been so widely accepted that it stays until today.

The basic operation principle of a MOSFET is actually quite straightforward. When a voltage source is connected in between the drain and source terminals, a conducting channel is to be formed between the two terminals to allow the current to flow. The channel is commonly referred to as the inversion layer since the charges accumulated at the channel oppose those of the substrate. In this case, the gate terminal acts like a switch which controls the formation of the inversion layer. When sufficient voltage drop (and, of course, with the appropriate polarity) is applied to the gate terminal, carriers would be attracted to the gate oxide-substrate interface to form the inversion layer.

Figure 2.

The (a) basic structure and (b) cross section of a MOSFET.

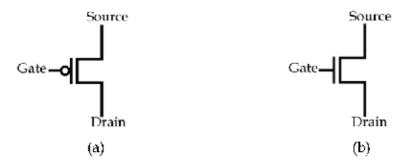

A MOSFET can be classified into two types, depending on the dopants in the drain and source terminals, as well as the substrate. When both the drain and source terminals, in a p-type substrate, are heavily doped with donator ions (such as phosphorous or arsenic), a negative channel is to be formed in between them to conduct current. On the other hand, when both terminals, in an n-type substrate, are heavily doped with acceptor ions (such as boron), a positive channel is to be formed. The former device is therefore known as a negative channel MOSFET or an NMOS transistor, while the latter is known as a positive channel MOSFET or a PMOS transistor. **Figure 3** shows the circuit symbols of both PMOS and NMOS transistors [4].

The size of a MOSFET transistor is measured by the gate length, which is also commonly known as the feature size or feature length as is denoted by the symbol L. The size of the transistor has been shrinking tremendously over the years. This allows a higher number of transistors to be fitted into a single die. Overseen by the Taiwan Semiconductor Industry Association (TSIA), the US Semiconductor Association (SIA), the European Semiconductor Industry Association (ESIA), the Japan Electronics and Information Technology Industries Association (JEITA) and the Korean Semiconductor Industry Association (KSIA), the International Technology Roadmap of Semiconductor (ITRS) is charted to forecast how the technology node is expected to evolve. The purpose of the ITRS is to ensure healthy growth of the IC industries. **Table 2** tabulates the progressive reduction of the feature size published in ITRS 2.0 [16]. In order to provide a clear outline to simplify academic, manufacturing, supply and research coordination regarding the development of electronic devices and systems, the ITRS was continued by the International Roadmap for Devices and Systems (IRDS) in 2018 [17].

#### 4.2 The FinFET

As the feature size reduces to the submicron regimes, fields at the source and drain regions become comparatively high, and this may induce certain adverse effects to the charge distribution. Some of the examples of these short-channel effects are the threshold voltage roll-off in the linear region, drain-induced barrier lowering (DIBL) and bulk punch-through [18]. To suppress these effects, additional steps such as the introduction of retrograde well, the deposition of the sidewall spacers, lightly doped drain (LDD) implantation, halo implantation, etc. have been introduced into the IC fabrication process [19]. As the device continues to shrink,

**Figure 3.**The symbol of (a) a PMOS transistor and (b) an NMOS transistor.

| Physical gate length        | Year |      |      |      |      |      |      |

|-----------------------------|------|------|------|------|------|------|------|

| _                           | 2015 | 2017 | 2019 | 2021 | 2024 | 2027 | 2030 |

| High-performance logic (nm) | 24   | 18   | 14   | 10   | 10   | 10   | 10   |

| Low-performance logic (nm)  | 24   | 20   | 16   | 12   | 12   | 12   | 12   |

**Table 2.** Forecast of gate length by ITRS.

curbing the short-channel effects turns out to be a strenuous task. When the feature size approaches the subnanometer range (i.e. 90 nm and below), static leakage current due to the short-channel effects has become a serious problem.

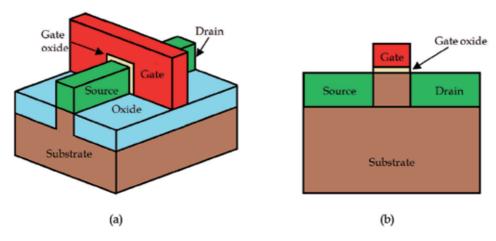

When the technology node reached 22 nm in 2011, Intel Corporation announced the fabrication of the tri-gate transistor, replacing the conventional planar MOSFET. Better known as the FinFET, this device has a three-dimensional transistor structure, as depicted in **Figure 4** [20]. It is apparent from the figure, a FinFET is named so because of the protruding source and drain terminals from its substrate surface, which resemble the fins of a fish. Since the gate wraps around the inversion layer, FinFETs provide higher current flow from the source to the drain terminals. This protruding fin structure also allows better control of the current flow, i.e. it reduces current leakage considerably when the device is at its "off-state" and minimizes short-channel effects at its "on-state". Since the device has lower threshold voltage than the planar MOSFET, a FinFET can also operate at relatively lower voltage drops. In a nutshell, the FinFET shows less leakage, faster switching and lower power consumption in comparison to its planar counterpart.

#### 5. IC design flow

Generally, the design process of an IC chip involves three stages—namely, the (i) behavioral, (ii) logic circuit and (iii) layout representations [4, 21]. At the end of each stage, verification is to be performed before proceeding to the next. Hence, it is common to have repetitions and iterations in the processes [4, 21].

#### 5.1 Behavioral representation

At the initial stage of IC design, it is important to be specific on the functionalities of the chip. The design architecture is to be drawn out. Verilog or SystemVerilog hardware description language (HDL) is used to define the behavior of the IC chip.

Figure 4.

The (a) basic structure and (b) cross section of a FinFET.

#### 5.2 Logic circuit representation

Once the HDL codes are successfully simulated, functional blocks from standard cell libraries are used to synthesize the behavioral representation of the design into logic circuit representation. Once the design is verified, the gate-level netlist is generated. The netlist consists of important information of the circuit such as the connectivity and nodes and is necessary in order to develop the layout of the design.

#### 5.3 Layout representation

The physical layout of the design is created at the final stage. The process starts with floor planning which defines the core and routing areas of the chip. In order to optimize the design, the building blocks are usually adjusted and orientated by IC designers. This process is known as placement. Once this is completed, a routing process is performed to interconnect the building blocks.

#### 6. Microchip fabrication

To fabricate the chip, the layout is sent to a fab or a foundry. In a fab, a single-crystal semiconductor ingot is first grown. Wafers are then sliced from the ingot. The layout is printed onto the dice in each wafer.

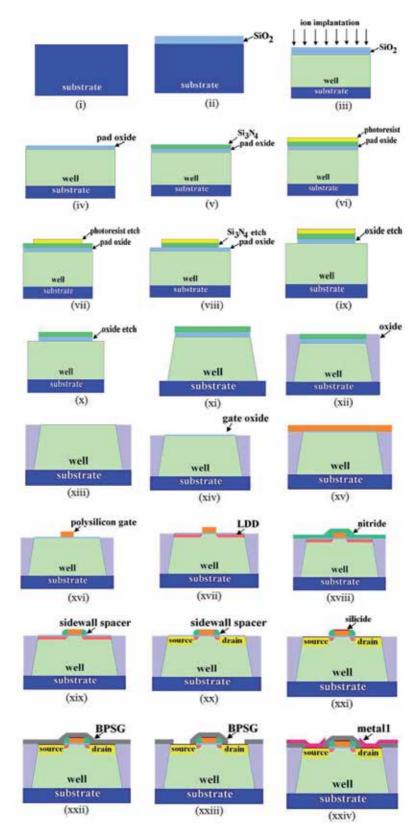

The fabrication process for NMOS and PMOS transistors is similar. The main differences lie within the types and density of dopants applied to the substrate—specifically in the formation of well, threshold voltage  $V_{TH}$  adjust implantation, LDD implantation, source/drain implantation, etc. The process flow of fabricating a planar MOSFET is summarized in the following sections, and it is also graphically depicted in **Figure 5**. The process of chip fabrication can be broadly separated into five stages, i.e. (i) well formation, (ii) device isolation, (iii) transistor making, (iv) interconnection and (v) passivation [15].

#### 6.1 Well formation

Initially, a p-type single-crystal silicon wafer is prepared (**Figure 5(i)**). In order to form a P (for NMOS) or N (for PMOS) well, screen oxide is first grown on the surface of the substrate (**Figure 5(ii)**). A high-energy ion implantation is then

Figure 5.

The fabrication process of a MOSFET.

performed to form the well (**Figure 5(iii)**). The wafer subsequently undergoes annealing and drive-in processes to, respectively, repair the lattice damage caused by the high-energy ion bombardment and to activate the dopant.

#### 6.2 Device isolation

Next, shallow trench isolation STI is employed to isolate neighboring devices. Initially, pad oxide is grown via dry oxidation (**Figure 5(iv**)). Chemical vapor deposition CVD technique is then applied to deposit a layer of silicon nitride Si<sub>3</sub>N<sub>4</sub> onto the oxide surface (**Figure 5(v**)). Pad oxide acts as a stress buffer to avoid cracks on the nitride film, whereas nitride film acts as a mask for silicon etching. A layer of photoresist is subsequently deposited onto the nitride layer (**Figure 5(vi)**). Lithography is performed to develop patterns on the photoresist (Figure 5(vii)). The nitride film and pad oxide are etched in accordance with the pattern formed at the photoresist (Figure 5(viii) and (ix)). The area protected under the nitride mask is known as the active region. As soon as the photoresist is stripped (**Figure 5(x)**), the substrate undergoes reactive ion etching (RIE) to form trenches (**Figure 5(xi)**). A thin layer of barrier oxide is grown in the trenches so as to block impurities from diffusing into the substrate during the CVD process. The trenches are then filled with oxide via the CVD process (**Figure 5(xii)**). The oxide at the surface of the substrate is removed using the chemical mechanical polishing (CMP) technique (**Figure 5**(**xiii**)). The STI is completed after annealing is performed, and the nitride and pad oxide layers are etched.

#### 6.3 Transistor making

A thin layer of gate oxide is applied via dry oxidation (**Figure 5(xiv)**). Threshold voltage  $V_{TH}$  adjust implantation is subsequently performed. This is then followed by thermal annealing to repair the lattice damage at the substrate surface. A layer of polysilicon is deposited onto the substrate surface after the annealing process (**Figure 5(xv)**). The polysilicon is then etched according to the dimension of the feature size and annealed to form the polysilicon gate.

Once the gate is formed, LDD is implanted to suppress hot electron effect in deep submicron MOSFETs (**Figure 5(xvii)**). The CVD process is applied to deposit a layer of silicon nitride  $Si_3N_4$  onto the surface of the substrate (**Figure 5 (xviii)**). The nitride film is etched to form sidewall spacers at both sides of the gate (**Figure 5 (xix)**). The source/drain dopant is then implanted into the substrate. The substrate subsequently undergoes annealing after the implantation process (**Figure 5(xx)**). This is then followed by the removal of the thin oxide layer. A layer of titanium or cobalt is then deposited onto the surface. Rapid thermal annealing (RTA) is employed to form the self-aligned silicide layers on the gate and source/drain surfaces. At the final stage of the transistor fabrication process, the unreacted titanium or cobalt layer is etched away (**Figure 5(xxi)**).

#### 6.4 Interconnection

Once the arrays of transistors are fabricated, metallization is required to interconnect the transistors so as to form electrical circuitries. In the interconnection stage, a layer of premetal dielectric (PMD) is first formed by depositing a layer of borophosphosilicate glass BPSG onto the substrate surface (**Figure 5(xxii)**). The PMD acts as the first layer of insulator for multilevel interconnection. After the die is annealed, the BPSG is etched to form source/drain contacts (**Figure 5(xxiii)**). Metallization is applied by depositing and etching aluminum (Al) on the contacts

Introductory Chapter: Integrated Circuit Chip DOI: http://dx.doi.org/10.5772/intechopen.92818

(**Figure 5(xxiv)**). Phosphosilicate glass PSG is used as the insulator material for the subsequent levels of metal interconnections. The insulator layers after PMD is known as the intermetal dielectric (IMD) layers. Vials filled with tungsten are usually used to interconnect different levels of metal layers.

#### 6.5 Passivation

The passivation layer is the final dielectric layer deposited onto the die after the last metal interconnection is formed. Silicon nitride is usually used as the passivation layer.

#### 7. Packaging

To protect the chip from harsh external environment (e.g. being exposed to UV light or moisture or being scratched), it is essential to encapsulate the chip in a ceramic or plastic package—a process known as packaging. The three most commonly used packaging techniques are (i) wire bonding, (ii) flip chip and (iii) tape-automated bonding (TAB) [10]. IC packaging marks the end of the entire chip manufacturing process. The chip is therefore ready to be released to the market, once the packaging process is completed.

#### **Author details**

Kim Ho Yeap<sup>1\*</sup>, Muammar Mohamad Isa<sup>2</sup> and Siu Hong Loh<sup>1</sup>

- 1 Universiti Tunku Abdul Rahman, Jalan Universiti, Kampar, Perak, Malaysia

- 2 Universiti Malaysia Perlis, Jalan Wang Ulu Arau, Kangar, Perlis, Malaysia

\*Address all correspondence to: yeapkh@utar.edu.my

#### **IntechOpen**

© 2020 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. [cc] BY

#### References

- [1] Nordrum A. Another step toward the end of Moore's law. IEEE Spectrum. 2019;**6**:9-11

- [2] Moore SK. TSMC's 5-nanometer process on track for first half of 2020. BACUS. 2020;**36**(1):8

- [3] Hiramoto T. Five nanometre CMOS technology. Nature Electronics. 2019;2:557-558. DOI: 10.1038/s41928-019-0343-x

- [4] Yeap KH, Nisar H. Introductory Chapter: VLSI. In: Yeap KH, Nisar H, editors. Very-Large-Scale Integration. Rijeka, Croatia: InTechOpen; 2018. pp. 3-11

- [5] Yeap KH, Introductory Chapter NH. Complementary metal oxide semiconductor (CMOS). In: Yeap KH, Nisar H, editors. Complementary Metal Oxide Semiconductor. London, UK: IntechOpen; 2018. pp. p3-p7

- [6] Arsov GL. Celebrating 65th anniversary of the transistor. Electronics. 2013;17:63-70. DOI: 10.7251/ELS1317063A

- [7] Lukasiak L, Jakubowski A. History of semiconductors. Journal of Telecommunications and Information Technology. 2010;1:3-9. DOI: 10.1088/0031-9120/40/5/002

- [8] Seidenberg P. From germanium to silicon: A history of change in the technology of the semiconductors. In: Goldstein A, Aspray W, editors. New Brunswick: IEEE Press; 1997. pp. 35-74

- [9] Moore GE. Cramming more components onto integrated circuits. Electronics. 1965;**38**:14-117. DOI: 10.1109/N-SSC.2006.4785860

- [10] Yeap KH. Fundamentals of Digital Integrated Circuit Design. 1st ed. UK: Authorhouse; 2011

- [11] Lilienfeld JA. Method and apparatus for controlling electric currents. U. S. Patent No. 1745175A (Filed: 08 October 1926. Issued: 28 January 1930)

- [12] Kahng D. Electric field controlled semiconductor device. U. S. Patent No. 3, 102, 230 (Filed: 31 May 1960. Issued: 27 August 1963)

- [13] Hofstein SR, Heiman FP. Silicon insulated-gate field-effect-transistor. Proceedings of the IEEE. 1963;51:1190-1202

- [14] Wanlass SM, Sah CT. Nanowatt logic using field-effect metal-oxide semiconductor triodes. In: Proceedings of the IEEE Conference on Solid-State Circuits Conference. Digest of Technical Papers; US; 1963. pp.32-33

- [15] Xiao H. Introduction to Semiconductor Manufacturing Technology. US: Prentice Hall; 2001

- [16] International Technology Roadmap for Semiconductors 2.0 [Internet]. 2015. Available from: https://www. semiconductors.org [Accessed: 03 April 2017]

- [17] International Roadmap for Devices and Systems [Internet]. Available from: https://irds.ieee.org/

- [18] Sze SM. Semiconductor Devices: Physics and Technology. 2nd ed. US: John Wiley and Sons; 2002

- [19] Ahmad I, Ho YK, Majlis BY. Fabrication and characterization of a 0.14 μm CMOS device using ATHENA and ATLAS simulators. International Scientific Journal of Semiconductor, Physics, Quantum Electronics, and Optoelectronics. 2006;**9**(2):40-44. DOI: 10.15407/spqeo

- [20] Yeap KH, Lee JY, Yeo WL, Nisar H, Loh SH. Design and characterization

Introductory Chapter: Integrated Circuit Chip DOI: http://dx.doi.org/10.5772/intechopen.92818

of a 10 nm FinFET. Malaysian Journal of Fundamental and Applied Sciences. 2019;**15**(4):609-612

[21] Yeap KH, Thee KW, Lai KC, Nisar H, Krishnan KC. VLSI circuit optimization for 8051 MCU. International Journal of Technology. 2018;**9**(1):142-149

# Section 2 Microchip Design Methods

#### **Chapter 2**

## Ultra-Low-Voltage IC Design Methods

Daniel Arbet, Lukas Nagy and Viera Stopjakova

#### **Abstract**

The emerging nanoscale technologies inherently offer transistors working with low voltage levels and are optimized for low-power operation. However, these technologies lack quality electronic components vital for reliable analog and/or mixed-signal design (e.g., resistor, capacitor, etc.) as they are predominantly used in high-performance digital designs. Moreover, the voltage headroom, ESD properties, the maximum current densities, parasitic effects, process fluctuations, aging effects, and many other parameters are superior in verified-by-time CMOS processes using planar transistors. This is the main reason, why low-voltage, low-power high-performance analog and mixed-signal circuits are still being designed in mature process nodes. In the proposed chapter, we bring an overview of main challenges and design techniques effectively applicable for ultra-low-voltage and low-power analog integrated circuits in nanoscale technologies. New design challenges and limitations linked with a low value of the supply voltage, the process fluctuation, device mismatch, and other effects are discussed. In the later part of the chapter, conventional and unconventional design techniques (bulk-driven approach, floating-gate, dynamic threshold, etc.) to design analog integrated circuits towards ultra-low-voltage systems and applications are described. Examples of ultra-low-voltage analog ICs blocks (an operational amplifier, a voltage comparator, a charge pump, etc.) designed in a standard CMOS technology using the unconventional design approach are presented.

**Keywords:** analog/mixed-signal IC design, unconventional design approach, bulk-driven design, ultra-low-voltage, ultra-low-power, standard nanoscale CMOS technology

#### 1. Introduction

The design of ultra-low-voltage (ULV) and low-power (LP) analog and mixed-signal ICs in modern nanotechnologies represents a real challenge for circuit designers and researches, since it introduces several limitations in numerous aspects. Firstly, since advanced nanoscale technologies offer a possibility to design analog, digital, and radio-frequency (RF) circuits as well as micro-electro-mechanical systems (MEMS) on a single chip, there is usually issue of a common value of the supply voltage. With the technology development, the value of the supply voltage is scaled down significantly. However, the threshold voltage ( $V_{TH}$ ) of the MOS devices is *not* lowered at the same pace. This fact reduced the voltage headroom for conventional circuit topologies (e.g., cascode structures) to operate

correctly. Low value of the supply voltage may significantly influence the main parameters of analog ICs such as dynamic range (DR), power supply rejection (PSR), noise immunity, etc. The second limiting factor lies in the significant fluctuation of process parameters in nanoscale technologies that brings new requirements to IC design—circuits have to be robust enough against process, temperature, and voltage variations [1].

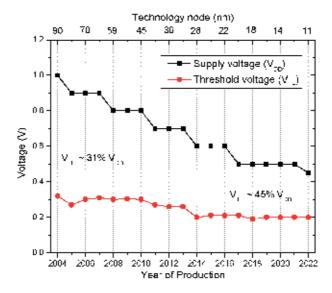

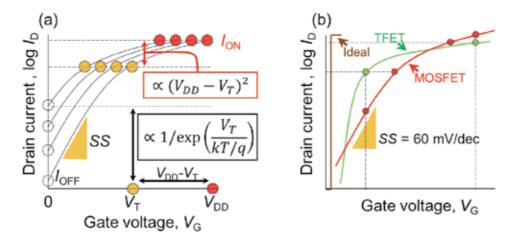

From the IC design point of view, one of the main problems caused by a lowered  $V_{DD}$  value is the reduction of useful voltage range for existing and standard circuit topologies. Analog circuits are suffering mostly from this limiting drawback. Decreasing the threshold voltage, as well as thinner layer of the gate oxide of a MOS (metal oxide semiconductor) transistor cause steep rising of the sub-threshold leakage current that is rather typical for nanotechnologies. These reasons do limit the further decrease of the threshold voltage. **Figure 1** depicts the dependency of the  $V_{DD}$  level and the threshold voltage on the technology node that is predicted for years to come by IRDS (International Roadmap for Devices and Systems). One can observe that the threshold voltage cannot follow the trend of the supply voltage level decrease due to substantial leakage currents.

The minimum power supply voltage of CMOS analog ICs designed without dedicated low-voltage (LV) techniques is limited by a value given by the sum of the turn-on voltage  $V_{GS}$  of MOS transistor and required voltage swing. For example, the voltage of  $\approx 300$  mV can be considered an average threshold voltage level in standard deep sub-micron CMOS fabrication process for transistors with reasonable channel length. This amount of external voltage applied between the gate and bulk terminal (or vice versa) is usually sufficient to introduce a strong inversion in the MOS structure and hence, turn-on the transistor. Another problem created by low supply voltages ( $V_{DD} \approx 600$  mV and lower) is the limited voltage headroom for cascode circuit structures and stacked transistors [2]. Therefore, new design approaches focused on the low-voltage circuit topologies that can overcome limitations mentioned above are still required.

Figure 1.

Scaling the supply voltage and threshold voltage in time.

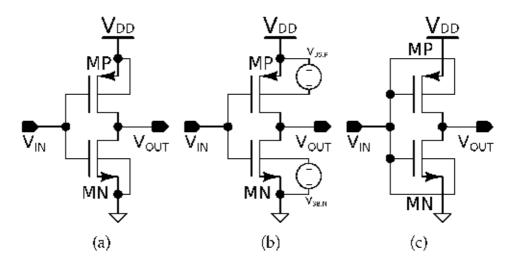

#### 2. Low-voltage design techniques and approaches

In this section, the survey of low-voltage design techniques and approaches that can be used in a standard CMOS technology (no additional process steps) are presented. Generally, low-voltage design techniques can be divided into two groups: conventional methods and unconventional ones. Unconventional methods include bulk-driven (BD) approach, dynamic threshold technique, floating-gate method, quasi-floating gate, and bulk-driven quasi-floating gate approaches. However, only the circuits designed by the bulk-driven and dynamic threshold approaches can be implemented in the standard CMOS technologies without any modification of the fabrication process. On the other hand, the conventional techniques such as circuits with rail-to-rail input/output operating range, MOS transistors working in sub-threshold region, level shifter techniques or MOS transistor in self-cascode structure represent commonly used approaches in the area of low-voltage IC design.

Since only circuits designed by the bulk-driven approach can be implemented in pure CMOS technology, in this chapter, we focus on this LV circuit design technique. At the end of this chapter, some examples of experimental and silicon-proven analog/mixed-signal circuits designed by the BD approach are presented.

#### 2.1 MOS transistor in sub-threshold operation region

Firstly, it is vital to explain the operation regions of the MOS transistor, since this is the most important aspect for analog IC design. The optimum IC design is characterized by the minimum power consumption, minimum silicon area and sufficient frequency response, gain and other circuit specifications. Analog and mixed-signal circuit design procedure of systems using (ultra) low-power supply voltage introduces an extra layer of challenges for even seasoned circuit designers. The problems low supply voltage introduces, negatively influence several design considerations, circuit attributes and possible design options. The first and foremost is the substantially limited inversion level the MOS transistors operate in. This results, among others, in higher mismatch between transistor parameters, exponential temperature sensitivity, and drastically lowered operational frequency. We must not forget the increased silicon area requirements due to large transistors compensating for low transconductance values, increased noise and difficulties with precise secondary effects modeling. All of the above are typical drawbacks of low-voltage/low-power circuit design and their application [3]. The second issue is topological. It lies in constrained possible number of stacked transistors, in order to ensure their operation in saturation region. According to [4], the theoretical lower limit for saturation voltage of a MOS transistor in deep the sub-threshold region is defined as  $V_{DSsat(min)} \approx 4 \cdot \frac{kT}{a}$ , which at room temperature, equals to approximately 105 mV. However, with increasing inversion level, this value grows with square root trend.

The situation has been greatly improved by the development of design-oriented charge-sheet based EKV MOS transistor model (named after its authors—Enz-Krummenacher-Vittoz) [5]. EKV model defines the parameters of MOS device dependent on continuous range of inversion level unlike the industry-standard threshold voltage-based BSIM models. EKV model also introduced the so-called  $g_m/I_D$  design approach, which avails simple, yet accurate hand-calculations, straightforward transistor sizing and complete technology independence. In [4], the author defines the level of inversion, also called *inversion coefficient* (IC) of a MOS structure by Eq. (1).

$$IC = \left[ln\left(1 + e^{rac{V_{GS} - V_{TH}}{2n \cdot U_T}}\right)\right]^2 = \frac{I_D}{I_{technology} \cdot rac{W}{I}},$$

(1)

where  $V_{GS}$  is voltage between gate and source terminal of the MOS transistor,  $V_{TH}$  is a MOS transistor's threshold voltage, n is sub-threshold so-called slope factor,  $U_T$  is Boltzmann's thermal voltage (25.86 mV at room temperature), W is MOS transistor channel width, L is MOS transistor channel length, and  $I_{specific}$  technology specific, current when a square MOS device (W = L) is in the middle of inversion range IC = 1.

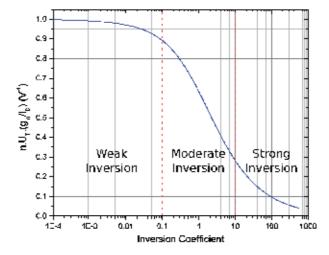

The point when IC = 1 also determines the conditions when the drain diffusion current equals drain drift current. The interpolated dependency of *transconductance efficiency*— $g_m/I_D$  as a function of IC is defined by Eq. (2). It represents very powerful formula since it is completely technology independent [6]. Furthermore, it can be easily implemented into a spreadsheet, introducing automated calculations and transistor sizing.

$$\frac{g_m}{I_D} = \frac{1}{n.U_T.\left(\frac{1}{2} + \sqrt{\frac{1}{4} + IC}\right)}$$

(2)

Figure 2 depicts the dependency of  $g_m/I_D$  on the inversion coefficient—IC, governed by Eq. (2). The area where IC ≤ 0.1 represents the sub-threshold operation region that is also called *weak inversion*. The MOS transistor operating under these conditions exhibits high voltage gain, low drain current, low saturation voltage but also large dimensions in order to compensate low transconductance and very low cut-off frequency. When inversion coefficient becomes IC ≥ 10, the MOS devices is operating in *strong inversion* or above the threshold voltage—the traditional working conditions. MOS transistor can process signals at high frequencies and does not require much of silicon area. However, the gain lowers and the drain current increases. The region in between of the weak and strong inversion (0.1 ≤ IC ≥ 10) describes a smooth transition between these two states. It is often called a *moderate inversion* and it represents a very good trade-off of the transistor and circuit parameters. Furthermore, the modern nanoscale CMOS technologies, working with lowered power supply voltage, are shifting the transistor operation into the

**Figure 2.**  $g_m/I_D$  as a function of inversion coefficient—IC.

moderate inversion, as the voltage headroom decreases and the level of the threshold voltage remains fairly constant over time (**Figure 1**).

## 2.2 Bulk-driven design approach

In the conventional approaches, MOS transistor is usually controlled by its gate potential. However, the current flowing through the device can also be modulated by the bulk-source voltage  $V_{BS}$ , which is usually considered a parasitic effect and may introduce undesired body transconductance  $g_{mb}$ . In the BD design approach, the input signal is applied to the transistor bulk, while a bias voltage is connected to the gate in order establish a channel between the source and drain terminals. If a constant  $V_{GS}$  is kept as the bias voltage and the input signal is applied to the bulk electrode, then a JFET-like transistor behavior can be obtained. In other words, the inversion channel width is modulated according to the voltage applied to the bulk. Using the bulk as the signal input results in significantly reduced need to overcome the threshold voltage at the MOS transistor.

The effect of the  $V_{BS}$  on the drain current is embedded in the threshold voltage  $V_{TH}$ . The threshold voltage of MOS transistor can be expressed by Eq. (3). It also serves as *very important* link between  $g_m/I_D$ , IC and bulk-driven design approaches.

$$V_{TH} = V_{TH0} \pm \gamma \left( \sqrt{2|\Phi_F| - V_{BS}} - \sqrt{2|\Phi_F|} \right), \tag{3}$$

where  $V_{TH0}$  is the threshold voltage with  $V_{BS}$  = 0 V,  $\gamma$  is technology-specific body factor, and  $\Phi_F$  is technology-specific Fermi's potential.

Thus, changes in  $V_{BS}$  value will result in modification of  $V_{TH}$ , which will inevitably modify the inversion coefficient according to Eq. (1) and finally, control the MOS transistor drain current.

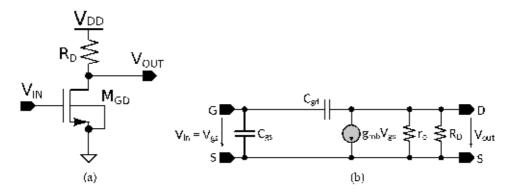

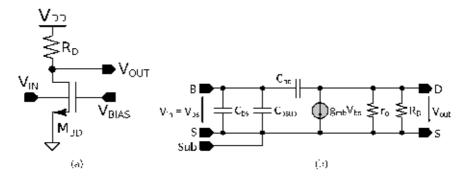

In order to analyze the properties of a MOS transistor driven by the bulk terminal, the conventional gate-driven and bulk-driven single stage common-source amplifiers, depicted in **Figures 3** and **4**, have been investigated and compared.

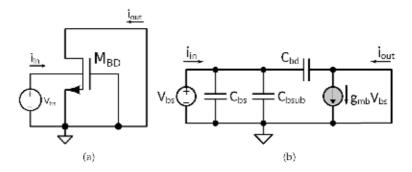

From **Figures 3** and **4**, it can be observed that the input capacitance of the BD single stage amplifier will be higher than in the case of the GD amplifier. It is caused by a parasitic capacitance  $C_{bsub}$  between the bulk and substrate terminals. In the case of the GD amplifier, the input capacitance depends on  $C_{gs}$  and  $C_{gd}$  capacitances, while the BD amplifier has the input capacitance dependent on the bulk-source  $C_{bs}$ , bulk-drain  $C_{bd}$  and bulk-substrate  $C_{bsub}$  capacitances combined together.

Figure 3.

Gate-driven common-source amplifier. (a) Schematic diagram, and (b) Small-signal model.

**Figure 4.**Bulk-driven single stage amplifier. (a) Schematic diagram, and (b) Small-signal model.

The transconductance of the conventional GD transistor can be expressed by the following Eq. (4)

$$g_m = \beta \frac{W}{L} \cdot (V_{GS} - V_{TH}) \tag{4}$$

It is important to point out that Eq. (4) is only valid when the MOS transistor operates in the strong inversion. In the weak inversion, the transconductance is proportionally dependent on the drain current, as given by Eq. (5).

$$g_{m_{wi}} = \frac{I_{DS_{wi}}}{n \cdot U_T} \tag{5}$$

The relationship between the transconductance of a GD transistor  $g_m$  and BD transistor  $g_{mb}$  is given by Eqs. (4) and (6).

$$g_{mb} = \frac{\gamma}{2\sqrt{|2\phi_F - V_{bs}|}} \cdot g_m$$

$$g_{mb} = \frac{C_{btot}}{C_{gtot}} \cdot g_m$$

$$g_{mb} \approx (0.2 \div 0.3) \cdot g_m$$

(6)

where  $C_{btot}$  and  $C_{gtot}$  are the total parasitic capacitances between bulk and channel and gate and channel, respectively. It can be observed that transconductance of the BD MOS transistor is only 20–30% of transconductance of the GD MOS transistor.

In order to determine the frequency performance of the BD transistor, schematic diagram, and small-signal model (depicted in **Figure 5**) have to be employed. Using small-signal model, the transition frequency  $f_{T,BD}$  of the BD MOS transistor can be obtained. Firstly, it is important to define the transition frequency of the GD MOS transistor given by Eq. (7).

$$f_{T,GD} = \frac{g_m}{2\pi C_{gs}} \tag{7}$$

The transfer function and current gain of the BD MOS transistor can be expressed by Eq. (8).

Figure 5. Schematic diagram and small-signal model for  $f_{T,BD}$  calculation. (a) Schematic diagram, and (b) Small-signal model.

$$\frac{i_{out}}{i_{in}} \approx \frac{g_{mb} \cdot V_{bs}}{j\omega(C_{bs} + C_{bsub} + C_{bd}) \cdot V_{bs}}$$

$$\frac{i_{out}}{i_{in}} \approx \frac{g_{mb}}{j\omega(C_{bs} + C_{bsub} + C_{bd})}$$

(8)

If we consider that unity small-signal gain is obtained at frequency  $\omega_{T,BD}$ , the transition frequency of the BD MOS transistor can be expressed as follows:

$$f_{T,BD} = \frac{1}{2\pi} \cdot \omega_{T,BD}$$

$$f_{T,BD} = \frac{g_{mb}}{2\pi (C_{bs} + C_{bsub} + C_{bd})}$$

$$f_{T,BD} \approx (0.2 \div 0.3) \cdot f_{T,GD}$$

$$(9)$$

As can be observed from Eq. (9), the transition frequency of the BD MOS transistor is about five times lower than in the case of a MOS transistor driven by gate terminal. Another important parameter of the amplifier is the noise introduced into the circuit by the active component. The input referred noise of the GD MOS transistor depends on the current  $i_{ds}$  and transconductance  $g_m$ , and can be expressed as follows:

$$v_{noise}^2 = \frac{i_{ds}^2}{\varrho_{re}^2} o \tag{10}$$

Similarly, the input referred noise of the BD MOS transistor is given by Eq. (11), where one can observe that the BD MOS transistor suffers from higher noise due to the lower transconductance  $g_{mb}$ .

$$v_{noise,BD}^2 = \left(\frac{g_m}{g_{mb}}\right)^2 \cdot v_{noise}^2 \tag{11}$$

The small-signal output resistance for both GD and BD transistors is identical, and given by Eq. (12).

$$r_o = \frac{1}{\lambda I_{DS}} = \frac{V_A}{I_{DS}},\tag{12}$$

where  $V_A$  represents early voltage and  $I_{DS}$  is the current flowing through the MOS transistor. As mentioned above, the BD technique uses bulk terminal for the

signal input, which results in significantly reduced need to overcome the threshold voltage at the MOS transistor input, as a whole. In summary, we can state the important advantages of the BD design technique, which include the following:

- BD MOS transistor depletion characteristics significantly reduce the need to overcome the threshold voltage  $V_{TH}$  at the transistor input and increases the voltage headroom for low-voltage applications.

- Suitable for rail-to-rail voltage range.

- Better linearity due to low, transconductance  $(g_{mh})$ .

- Possibility to operate with a low value of the power supply.

- Easy to implement in a standard CMOS technology (twin-well process, both MOS devices available).

Unfortunately, if compared to traditional GD design approach, the bulk-driven design method also exhibits the following disadvantages:

- Body transconductance  $g_{mb}$  of the BD MOS transistor is 4–5 times lower than the gate transconductance  $g_m$ , which leads to inferior frequency response and decreased gain-bandwidth product.

- Input capacitance of the BD MOS transistor is greater, if compared to the traditional GD device.

- Input noise of the BD MOS transistor is increased.

- BD MOS transistors fabricated in a standard CMOS process are prone to the catastrophic latch-up effect.

The last drawback, however, can be effectively mitigated by lowering the power supply voltage below the threshold voltage of a PN junction or by usage of an expensive silicon-on-insulator (SOI) fabrication process. This step would prevent the turn-on of the parasitic bipolar transistor in the substrate.

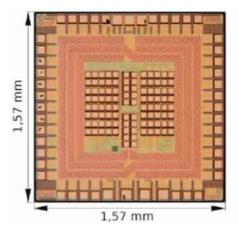

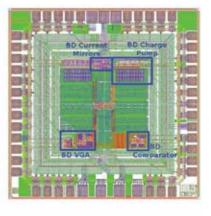

# 3. Design examples of low-voltage analog ICs

In this section, several design examples and circuit topologies of basic analog IC building blocks using bulk-driven approach are presented. The described blocks have been silicon-proven through fabrication in a standard CMOS nanotechnology and measurement evaluation of the chip prototypes.

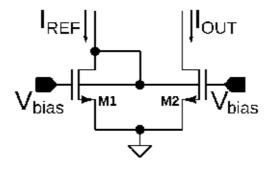

### 3.1 BD current mirrors

One of the most widely used circuit structures employed in IC design are arguably the current mirrors (CM). It is a two-port circuit, which processes the input current  $I_{REF}$  and generates the output current  $I_{OUT}$  based on the formula  $I_{OUT} = k \cdot I_{REF}$ , where k denotes an amplification (or mirroring) coefficient. **Figure 6** depicts the BD configuration of a simple CM. Obviously, more complicated CM structures can be designed using bulk-driven transistors [7].

Figure 6.

Simple BD current mirror.

Bulk terminals of both MOS devices M1 and M2 are tied together and connected to the input branch. The gate terminals are biased by static voltage  $V_{bias}$ . On the input side, the voltage drop  $V_{BS}$  is created by the input reference current flow. This voltage is also applied to the output branch, through the bulk terminal of M2. Hence, the output current is modulated by means of bulk-driving according Eq. (3).

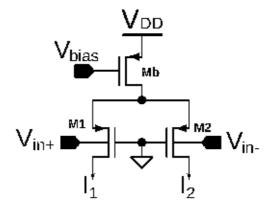

# 3.2 BD differential amplifier

Another widely and frequently implemented circuit topologies the differential amplifier is depicted in **Figure 7**; however, in the bulk-driven configuration. The devices M1 and M2 have their gate terminals tied to the lowest potential to guarantee the highest possible level of inversion. The traditional topology of the differential amplifier suffers from a limited input common-mode range ( $V_{CM}$ ) due to necessity of exceeding the input pair threshold voltage and minimal saturation voltage of the biasing high-side transistor  $M_b$ . The  $V_{CM}$  voltage range can be described by Eq. (13).

$$V_{CM} = V_{DD} - V_{DSsat(Mb)} - V_{TH}$$

(13)

The input BD transistors are used to obtain the rail-to-rail input voltage range, which is important for achieving a sufficient voltage swing when low supply voltage value is used, which greatly enhances the input common-mode range (ICMR). Additional benefit of employing the bulk-driven differential amplifier rather than conventional one lies in highly linear voltage-to-current conversion thanks to

**Figure 7.** *BD differential pair.*

almost perfectly constant transconductance  $g_{mb}$ . The disadvantage of presented topology is linked to the grounded gate terminals of the differential transistor pair. This way, the ground noise will be picked up by the transistors, which degrades the power supply rejection ratio (PSRR) [8]. An example of the BD differential pair use was published in [9], where it was used as the input pair of a variable-gain amplifier (VGA).

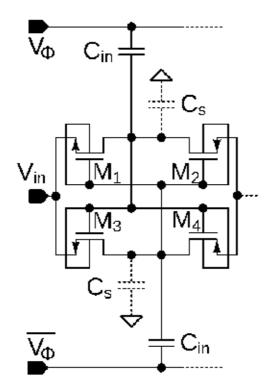

## 3.3 Variable-gain amplifier (VGA)

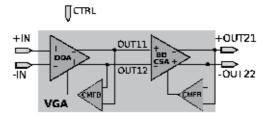

### 3.3.1 Description of BD VGA

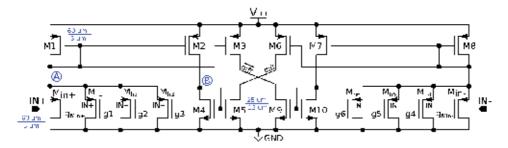

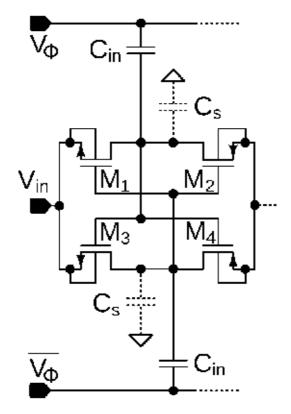

**Figure 8** shows the block diagram of a two-stage VGA. The first stage is formed by a variable-gain differential difference amplifier (DDA) designed using BD approach. The second stage has a fixed gain and is created by a BD common-source amplifier (CSA). For stabilization of the operational point of both stages, two BD common-mode feedback (CMFB) circuits have to be employed. To achieve good stability of the CMFB loop as well as the whole two-stage VGA, frequency compensation circuitry has been applied.

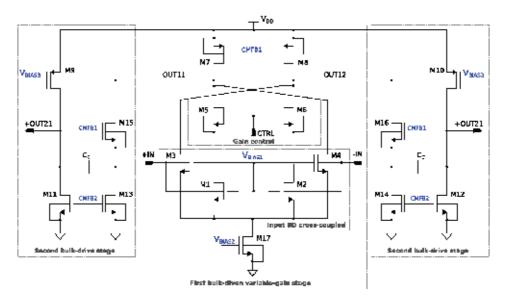

The schematic diagram of the low-voltage VGA circuit is depicted in **Figure 9**. The input stage of the proposed topology is formed by DDA with bulk-driven MOS transistors, in order to obtain rail-to-rail input voltage range. The negative aspect of this solution lies in the reduced voltage gain and the gain-bandwidth product (GBW) [8]. Therefore, it is safe to state, that the proposed approach is suitable for low-voltage and low-frequency applications.

In general, the overall VGA voltage gain can be controlled by adjusting either the total conductance or the total output impedance [8]. Thus, transistors M5 and M6 were employed to control the VGA gain. Modification of control voltage  $V_{CTRL}$  modulates the current flow through the input devices M1 and M2, which eventually changes their effective transconductance. This will, in effect, vary the voltage amplification of the first stage, which will result in modification of overall gain of the proposed VGA. The total VGA voltage gain is directly proportional to the transconductance of the gain control devices  $g_{m5}$  and  $g_{m6}$ . The input transistors along with the gain control devices form a cascode configuration, hence their small-signal parameters affect the overall output resistance of the first stage. Detailed small-signal analysis of the complete VGA is conducted in the following subsection. The second stage represents a BD common-source stage with the fixed gain that offers rail-to-rail input voltage range and a wide swing (nearly rail-to-rail) at the VGA output. Two CMFB circuits were used to achieve the stable operational point of both VGA stages.

**Figure 9** depicts the implemented frequency compensation circuit. The second amplification stage of the proposed VGA consists of devices M9–M12 and transistors M13–M16 along with capacitors  $C_c$  are responsible for the stability of the whole

Figure 8.

Block diagram of VGA.

**Figure 9.** Schematic diagram of VGA.

circuitry. The proposed compensation approach removes the feed-forward path between the outputs of both amplifying stages by introducing a sufficient voltage gain the feedback path (transistor M15 and M16). The position of the dominant pole is, therefore, maintained, but the position of the output pole gets shifted by the factor of introduced gain. The compensation capacitor  $C_c$  is employed between the virtual ground handled by the devices M13 and M14, and the output node of the VGA.

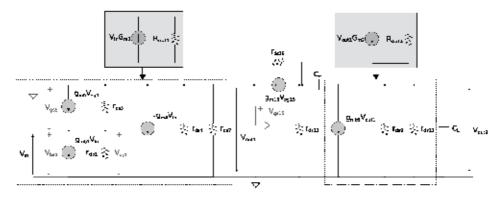

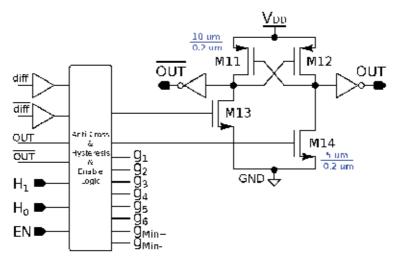

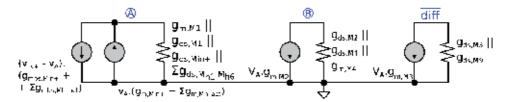

### 3.3.2 Design principle of VGA based on small-signal analysis

From the design point of view, it is important to ensure good stability and investigate the parameters that influence the gain of the proposed two-stage VGA. For this purpose, the small-signal model of VGA shown in **Figure 10** was used. We have to note that the output capacitance of the first stage was neglected. Thanks to the overall symmetry of the topology, we can perform the small-signal analysis just for one half-circuit and investigate the influence of  $+V_{in}$  and  $-V_{in}$  separately. The total voltage gain will be, therefore, equal to the sum of the partial contributions of the respective gain stages.

The resulting formula defining the total DC gain of the discussed VGA is follows:

$$A_{v} = G_{m1}R_{out1} \cdot G_{m2}R_{out2} = A_{1} \cdot A_{2} \tag{14}$$

where  $A_1$  and  $A_2$  is gain of the first stage and the second stage, respectively. The total transconductance and the total output resistance of the first VGA stage are denoted as  $G_{m1}$  and  $R_{out1}$ , respectively. The same parameters associated with the second stage are named  $G_{m2}$  and  $R_{out2}$ . The impact of frequency compensation block has been neglected for additional simplification of the small-signal analysis Eq. (14).

$G_{m1}$  and  $G_{m2}$  depicted in **Figure 10** are defined follows:

$$G_{m1} = g_{mb1} \cdot \frac{g_{m5}}{g_{ds1} + g_{m5}} - g_{mb4} = g_{mb1} \cdot C - g_{mb4}$$

(15)

Figure 10.

Small-signal model of the VGA.

$$G_{m2} = g_{mh9} \tag{16}$$

where  $g_{mb1}$ ,  $g_{mb4}$ , and  $g_{mb9}$  are bulk transconductance of transistors M1, M4, and M9,  $g_{m5}$  is a transconductance of transistor M5, while  $g_{ds1}$  and  $g_{ds5}$  are output transconductance of transistors M1 and M5, respectively. In Eq. (15), we consider that  $g_{m5} > g_{ds5}$ . The total transconductance of the first stage can be varied by the transconductance of transistor M5, while the second stage has a fixed value of transconductance.

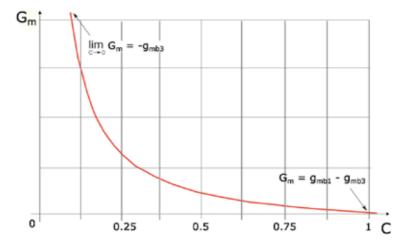

$$C = \frac{g_{m5}}{g_{ds1} + g_{m5}} = \frac{1}{1 + \frac{g}{g_{m5}}} \tag{17}$$

One can observe that the total transconductance of VGA ( $G_{m1}$ ) can be controlled by transconductance  $g_{m5}$ , which depends on the control voltage (CTRL). **Figure 11** shows the dependence of the total transconductance  $G_{m1}$  on the coefficient C that can vary in the range from 0 to 1. If  $g_{m5} < g_{ds1}$ , the coefficient C from Eq. (17) becomes zero and the total transconductance of VGA will be equal to  $-g_{mb3}$ . In the opposite case (when  $g_{m5} > g_{ds1}$ ), coefficient C is equal to 1 and  $G_{m1}$  will be equal to  $g_{mb1} - g_{mb3}$ . This means that by increasing the transconductance  $g_{m5}$ , the total transconductance  $G_{m1}$  is decreased.

**Figure 11.** Transconductance  $G_{m_1}$  versus the coefficient C.

Besides, the total transconductance  $G_{m1}$  also depends on  $g_{ds1}/g_{m5}$  ratio. If numerator and denominator of the ratio are divided by  $I_{ds1}$ , the following expression can be written:

$$\frac{g_{ds1}}{g_{m5}} = \frac{\frac{g_{ds1}}{I_{ds1}}}{\frac{g_{m5}}{I_{ds1}}} = \frac{V_{CTRL} - V_{TH1}}{2 \cdot (V_{A1} + V_{ds1})},$$

(18)

where  $V_{CTRL}$  is the control voltage of VGA, and  $V_{TH1}$ ,  $V_{A1}$ , and  $V_{ds1}$  is the threshold voltage, Early voltage and voltage between source and drain of transistor M1, respectively. From Eq. (18), it can be observed that  $g_{ds1}/g_{m5}$  ratio, which controls the total transconductance  $G_m$ , depends on the control voltage of the proposed VGA. Using the small-signal model depicted in **Figure 10**, the output resistances  $R_{out1}$  and  $R_{out2}$  of the proposed VGA are expressed as

$$R_{out1} = \underbrace{\left[ \left( 1 + g_{m5} r_{ds1} \right) r_{ds5} + r_{ds1} \right]}_{A} \| \underbrace{r_{ds4}}_{B} \| r_{ds7}, \tag{19}$$

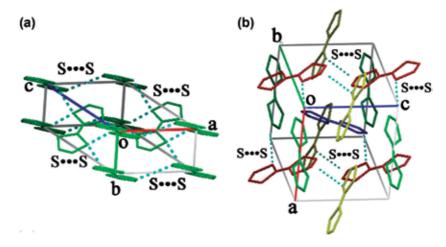

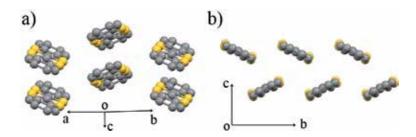

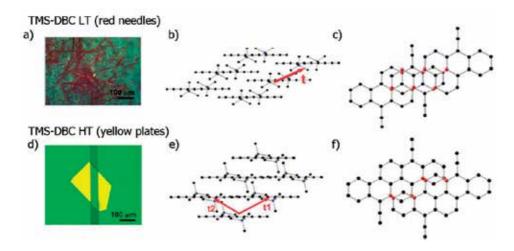

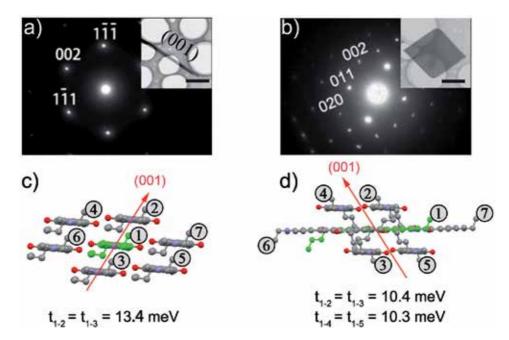

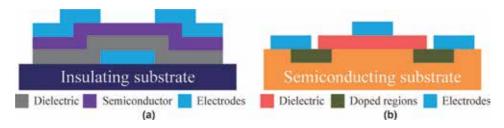

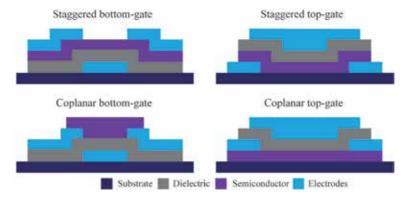

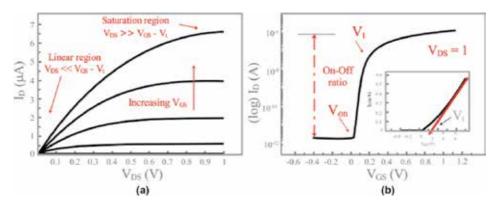

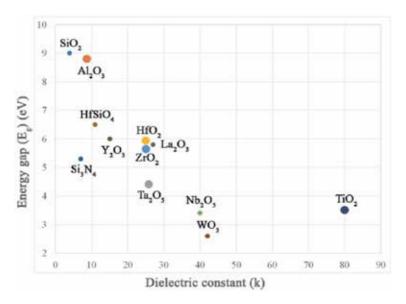

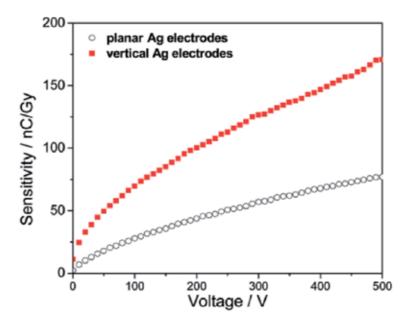

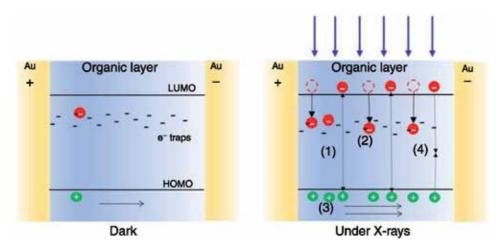

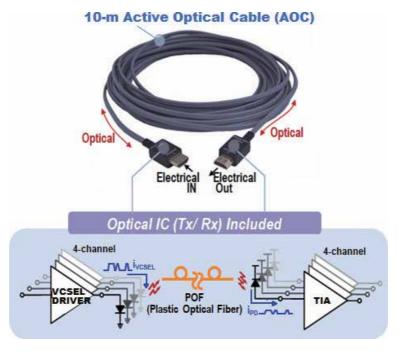

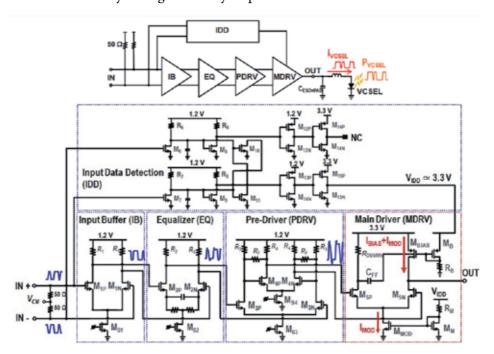

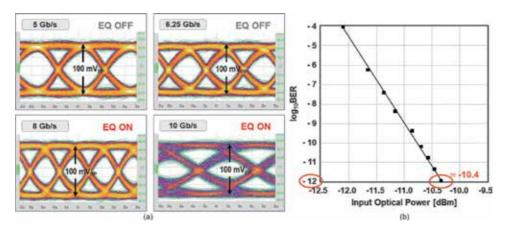

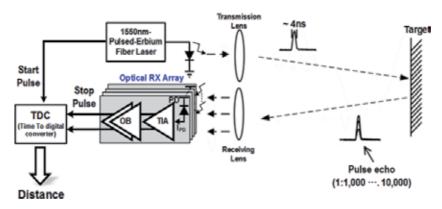

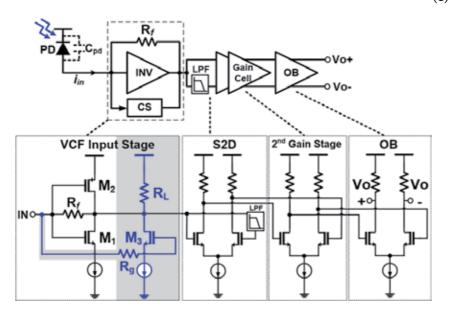

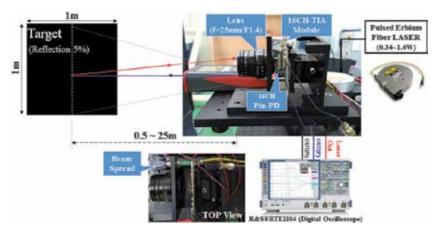

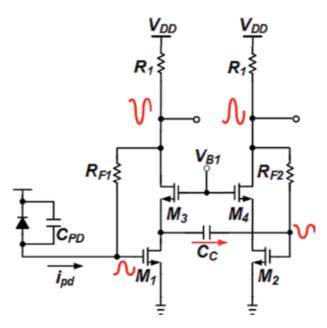

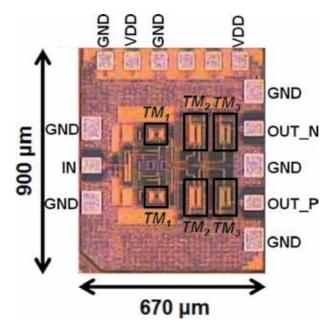

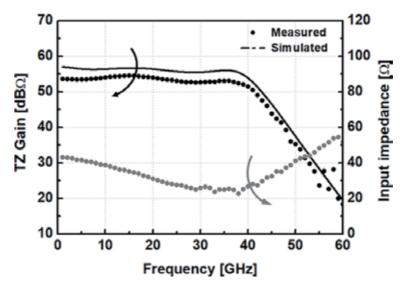

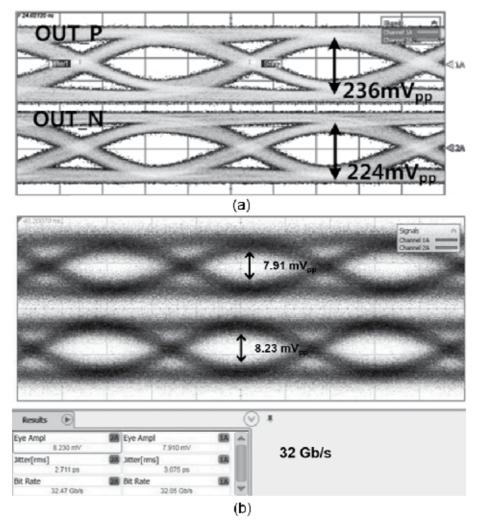

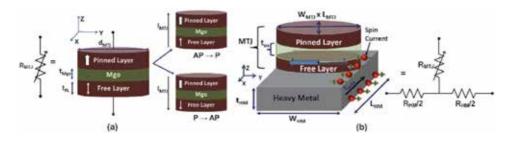

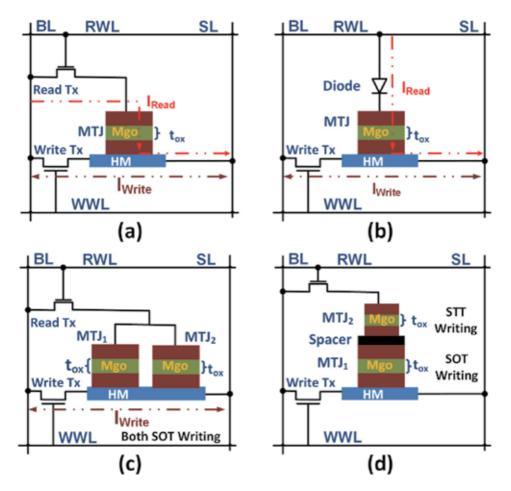

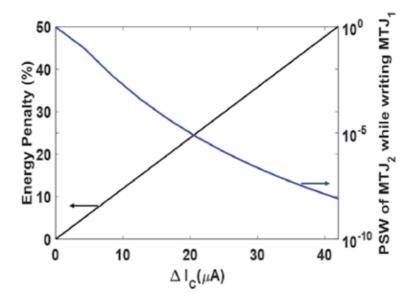

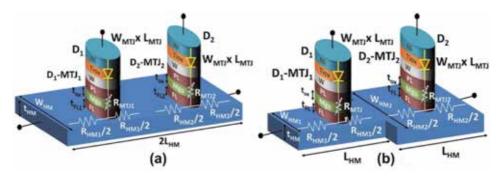

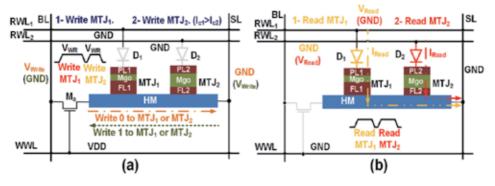

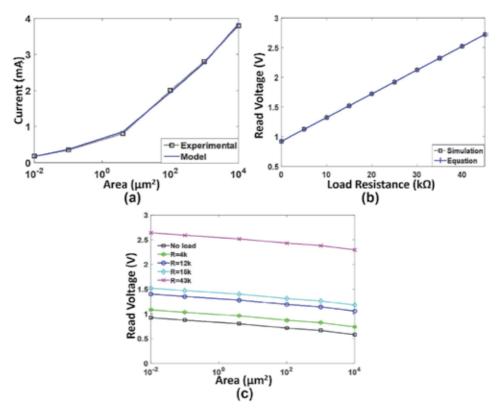

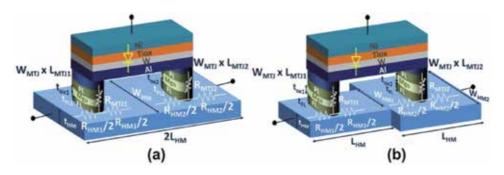

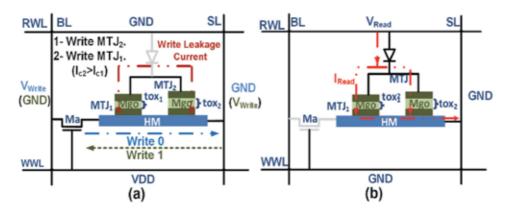

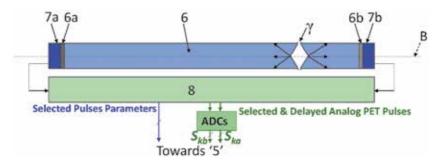

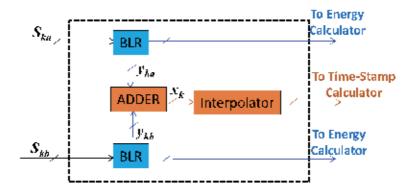

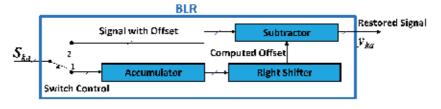

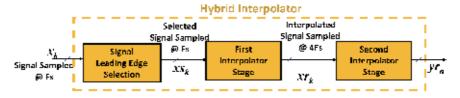

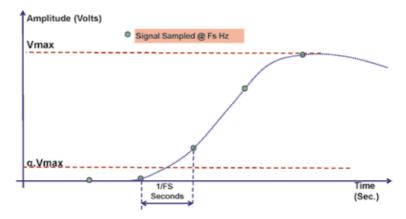

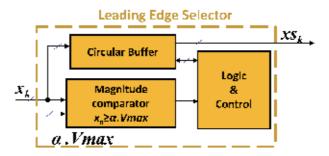

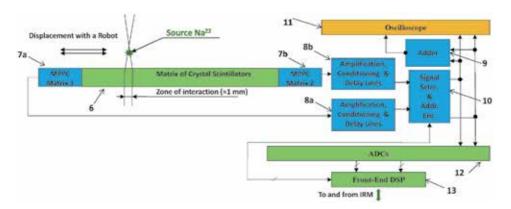

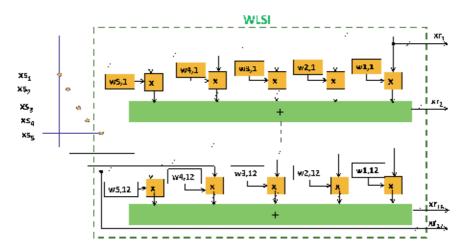

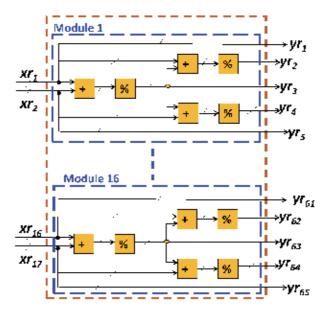

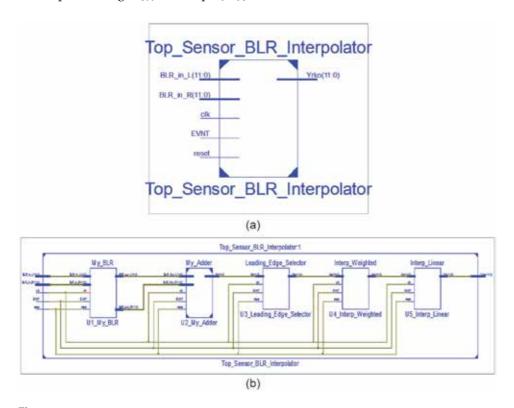

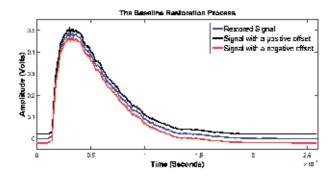

$$R_{out2} = r_{ds9} || r_{ds11}, (20)$$