## **IntechOpen**

# Design, Simulation and Construction of Field Effect Transistors

Edited by Dhanasekaran Vikraman and Hyun-Seok Kim

# DESIGN, SIMULATION AND CONSTRUCTION OF FIELD EFFECT TRANSISTORS

Edited by **Dhanasekaran Vikraman** and **Hyun-Seok Kim**

### Design, Simulation and Construction of Field Effect Transistors

http://dx.doi.org/10.5772/intechopen.72086 Edited by Dhanasekaran Vikraman and Hyun-Seok Kim

### Contributors

Dian Lei, Xiao Gong, Soheli Farhana, Erping Deng, Qiye Wen, Yu-Lian He, Zhi Chen, Qing-Hui Yang, Huai-Wu Zhang, Rupam Goswami, Brinda Bhowmick, Juan Antonio Delgado Notario, Vito Clerico, Kristel Fobelets, Enrique Velazquez, Yahya Moubarak Meziani, Lucas Fugikawa Santos, Giovani Gozzi, Guilherme De Lima, João Paulo Braga

### © The Editor(s) and the Author(s) 2018

The rights of the editor(s) and the author(s) have been asserted in accordance with the Copyright, Designs and Patents Act 1988. All rights to the book as a whole are reserved by INTECHOPEN LIMITED. The book as a whole (compilation) cannot be reproduced, distributed or used for commercial or non-commercial purposes without INTECHOPEN LIMITED's written permission. Enquiries concerning the use of the book should be directed to INTECHOPEN LIMITED rights and permissions department (permissions@intechopen.com). Violations are liable to prosecution under the governing Copyright Law.

Individual chapters of this publication are distributed under the terms of the Creative Commons Attribution 3.0 Unported License which permits commercial use, distribution and reproduction of the individual chapters, provided the original author(s) and source publication are appropriately acknowledged. If so indicated, certain images may not be included under the Creative Commons license. In such cases users will need to obtain permission from the license holder to reproduce the material. More details and guidelines concerning content reuse and adaptation can be foundat http://www.intechopen.com/copyright-policy.html.

### Notice

Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published chapters. The publisher assumes no responsibility for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained in the book.

First published in London, United Kingdom, 2018 by IntechOpen eBook (PDF) Published by IntechOpen, 2019 IntechOpen is the global imprint of INTECHOPEN LIMITED, registered in England and Wales, registration number: 11086078, The Shard, 25th floor, 32 London Bridge Street London, SE19SG – United Kingdom Printed in Croatia

British Library Cataloguing-in-Publication Data A catalogue record for this book is available from the British Library

Additional hard and PDF copies can be obtained from orders@intechopen.com

Design, Simulation and Construction of Field Effect Transistors Edited by Dhanasekaran Vikraman and Hyun-Seok Kim

Print ISBN 978-1-78923-416-9 Online ISBN 978-1-78923-417-6 eBook (PDF) ISBN 978-1-83881-651-3

# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

3,600+

Open access books available

113,000+

International authors and editors

115M+

Downloads

151

Countries delivered to

Our authors are among the

Top 1%

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE<sup>17</sup>

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

## Meet the editors

Dr. Dhanasekaran Vikraman is an Assistant Professor at the Division of Electronics and Electrical Engineering, Dongguk University, Seoul, Korea. He received his bachelor's degree from Mannai Rajagopalaswamy Govt. Arts College, Mannargudi, affiliated to Bharathidasan University, Tiruchirappalli, India. After that, he completed his Master's and PhD degrees at the Department of

Physics, Alagappa University, India. Later, he received a visiting scientist position at KIST, Korea; a Marie Curie Experienced Researcher Fellowship at the Department of Physics, Aristotle University of Thessaloniki, Greece; and a post-doc position at Sejong University and Ajou University, Korea. Dr. Dhanasekaran Vikraman has authored 84 international journal papers, 71 conference papers and 1 book chapter. His research interests are mainly focused on low-cost synthesis of inorganic materials and 2D materials for electronics and energy applications.

Professor Hyun-Seok Kim received his MSc and PhD degrees in electrical engineering from the University of Wisconsin-Madison, USA, in 2003 and 2007, respectively. He was a post-doctoral researcher at the University of Wisconsin-Madison where he was involved in the design and fabrication of nanoelectromechanical single electron transistors. He then joined Intel Corporation in

the USA as a senior R&D engineer from 2008 to 2011. He is currently an Associate Professor in the Division of Electronics and Electrical Engineering, Dongguk University, Seoul, South Korea. His main research interests are nano- and microelectronics and their application in sensors and energy-saving devices.

### Contents

### Preface XI Section 1 Design and Simulation of FETs 1 Chapter 1 Modeling of Nano-Transistor Using 14-Nm **Technology Node 3** Soheli Farhana Dielectric-Modulated TFETs as Label-Free Biosensors 17 Chapter 2 Rupam Goswami and Brinda Bhowmick Chapter 3 Band Gap Modulated Tunnel FET 37 Brinda Bhowmick and Rupam Goswami Chapter 4 Room-Temperature Terahertz Detection and Imaging by Using Strained-Silicon MODFETs 53 Juan Antonio Delgado-Notario, Vito Clericò, Kristel Fobelets, Jesús Enrique Velázquez-Pérez and Yahya Moubarak Meziani Chapter 5 Clamping Force Distribution within Press Pack IGBTs 73 Erping Deng, Zhibin Zhao, Jinyuan Li and Yongzhang Huang Section 2 Construction of FETs 95 Chapter 6 Ge0.83Sn0.17 P-Channel Metal-Oxide-Semiconductor Field-**Effect Transistors: Impact of Sulfur Passivation on Gate** Stack Quality 97 Dian Lei and Xiao Gong Chapter 7 **Graphene Field-Effect Transistor for Terahertz Modulation** 117 Qi-Ye Wen, Yu-Lian He, Jing-Bo Liu, Qi Mao, Qing-Hui Yang, Zhi Chen and Huai-Wu Zhang

### **X** Contents

Chapter 8 Electrical Characterization of Thin-Film Transistors Based on Solution-Processed Metal Oxides 135

João P. Braga, Guilherme R. De Lima, Giovani Gozzi and Lucas Fugikawa Santos

### **Preface**

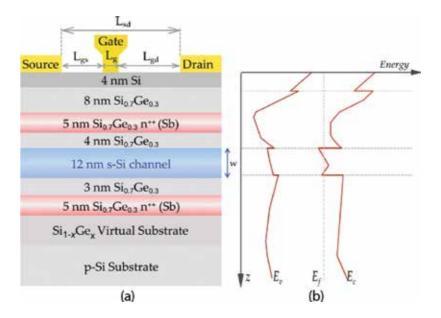

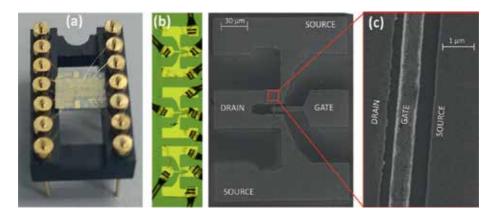

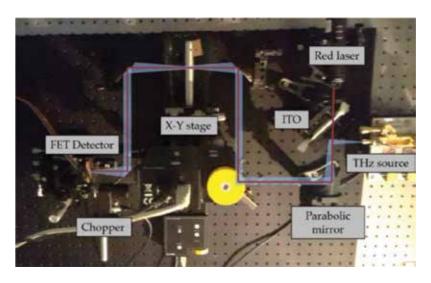

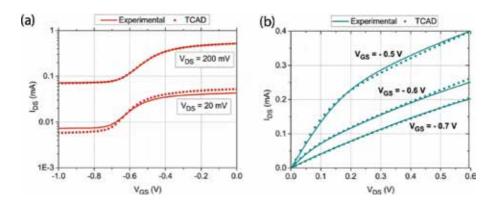

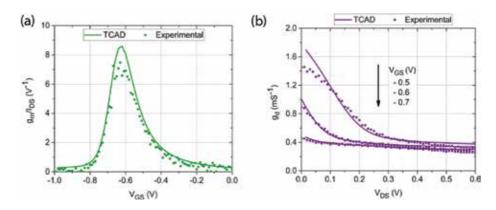

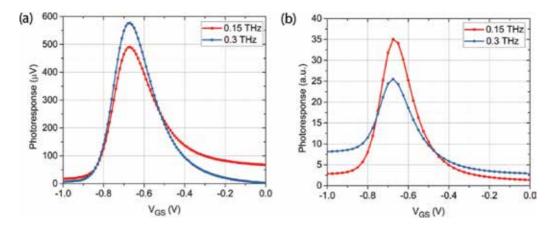

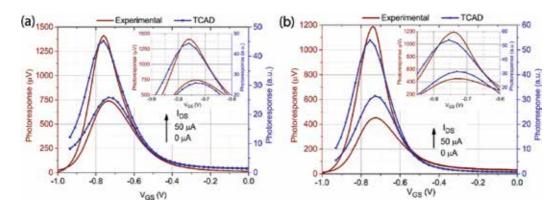

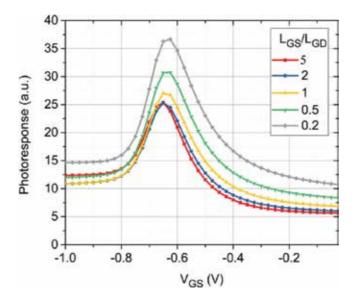

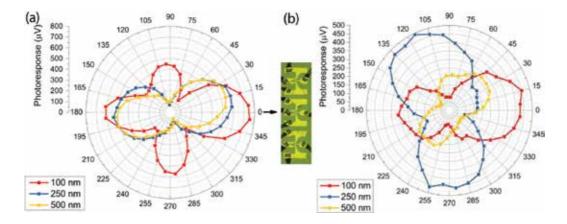

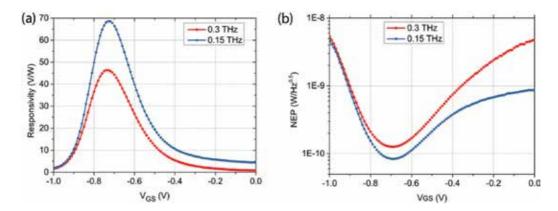

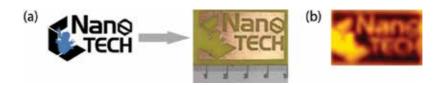

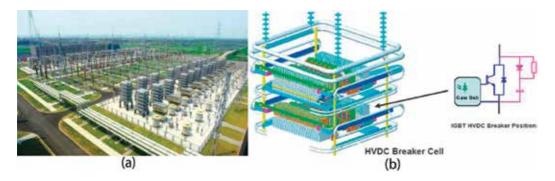

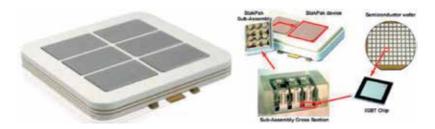

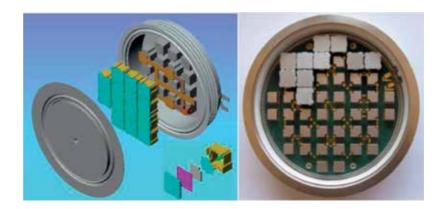

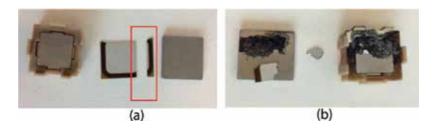

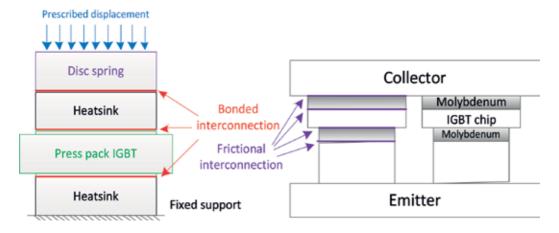

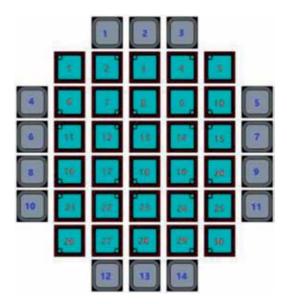

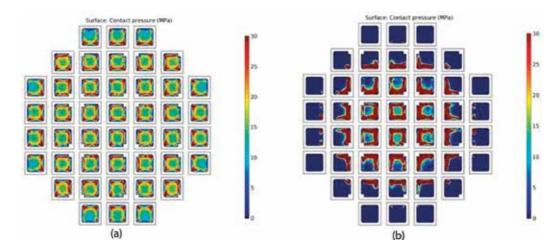

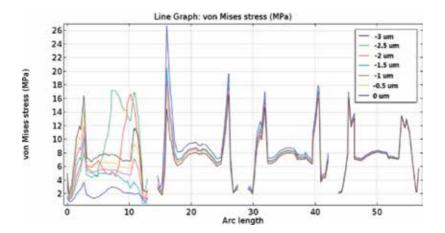

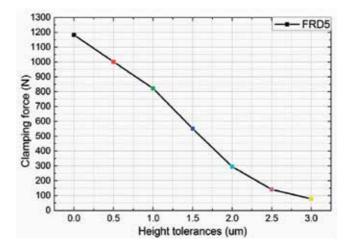

Field effect transistors (FETs) are the fundamental building blocks of microelectronics. In recent years, research on microelectronics has been specifically focused on the proposition of efficient alternative methodologies and materials to fabricate feasible integrated circuits. This book provides a general background of thin film transistors and their simulations. Recent developments in the realm of microelectronics are elaborated with evidence. The FET models and various related issues are also carefully described. The contents of the book are broadly classified into two topics: design and simulation of FETs and construction of FETs. The design and simulation of transistors section is elaborated in Chapters 1 to 5. Chapter 1 describes the 14-nm technology node to model nanosized transistors. Chapter 2 gives a brief account of the existing works on FET-based biosensors, the principle of dielectric modulation in tunnel field effect transistors (TFETs), and TFET simulations using technology computer-aided design (TCAD). Also, a circular gate TFET is presented as a dielectricmodulated biosensor and its practical implications are explained. Chapter 3 presents TFET bandgap modulation, which is supported by simulation results. The different TFET electrical parameters are also propounded in Chapter 3 using TCAD simulations. Chapter 4 reports an experimental and theoretical study of Schottky-gated strained-Si modulationdoped field-effect transistors (MODFETs) with different sub-micron gate lengths of 100, 250, and 500 nm. This chapter also elaborates the performance of strained-Si MODFETs at room temperature detection of 0.15 and 0.3 THz via TCAD simulations . Chapter 5 demystifies the role of clamping force on insulated gated bipolar transistors.

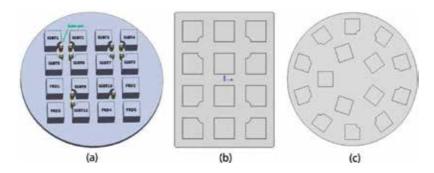

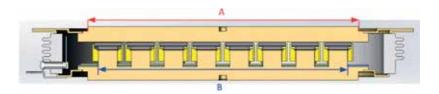

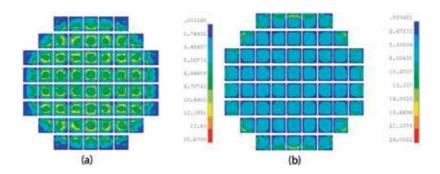

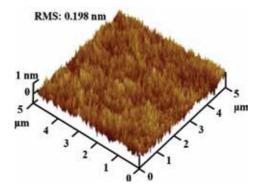

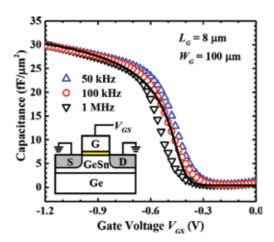

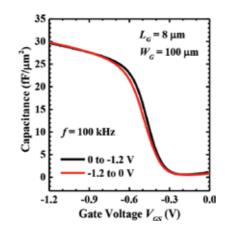

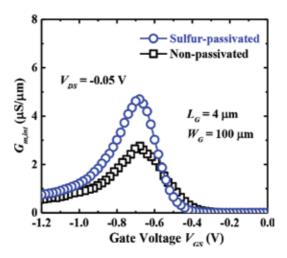

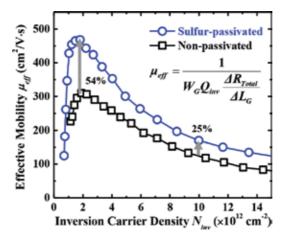

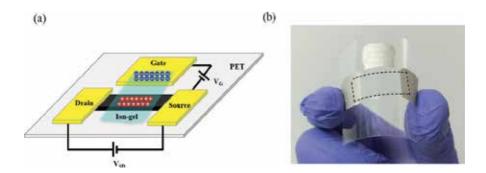

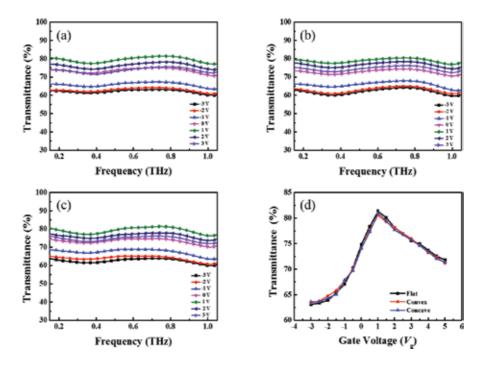

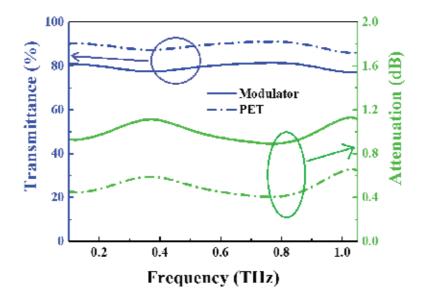

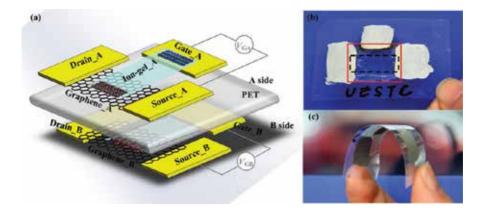

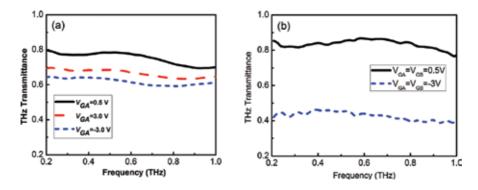

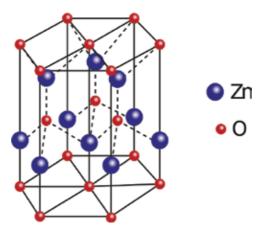

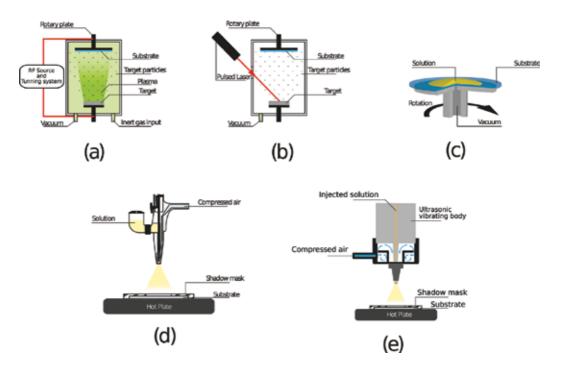

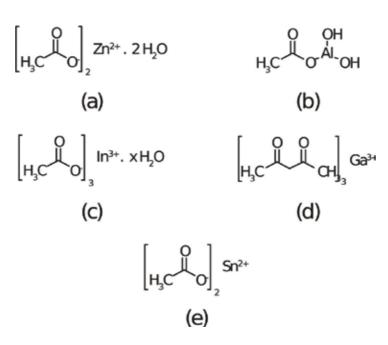

The construction of transistors is explained in Chapters 6 to 8. Chapter 6 demonstrates the effect of sulfur passivation on the surface of  $Ge_{0.83}Sn_{0.17}$  for p-channel metal-oxide-semiconductor field-effect transistors (p-MOSFETs). In addition, it also explains the growth conditions, characterization, and construction parameters of p-MOSFETs. Chapter 7 provides a short review of THz modulators and graphene FETs. The device structure, its construction, and the experimental observation of modulation characteristics of graphene FET-based THz modulators are also probed in detail for both rigid and flexible devices. Chapter 8 gives a brief introduction to TFTs based on transparent semiconducting metal oxides (SMOs) with special focus on solution-processed devices. It also explains the electrical properties of TFTs with the different active layer compositions such as intrinsic zinc oxide (ZnO), aluminum-doped ZnO, and indium-doped ZnO.

All the authors anticipate that the provided chapters will act as a single source of reference for the design, simulation, and construction of FETs. We are deeply grateful to all the authors for their great efforts and outstanding input in writing these chapters. We honestly hope that this book will be a guide to young researchers who are interested in researching FETs in the near future. We believe that the book will be a great addition to semiconductor physics.

Dhanasekaran Vikraman and Hyun-Seok Kim Division of Electronics and Electrical Engineering Dongguk University-Seoul, South Korea

| _        |     |    |   |   | 4 |

|----------|-----|----|---|---|---|

| <b>`</b> | SC. | rı | റ | n | 1 |

| J        | -   | u  | v |   |   |

# **Design and Simulation of FETs**

# Modeling of Nano-Transistor Using 14-Nm Technology Node

Soheli Farhana

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.76965

### Abstract

Latest process technologies in transistor development demonstrate massive changes in the size of transistor chip. In this chapter, a 14-nm technology node is used to model nanosize transistor. The 14-nm technology node consists of multiple numbers of carbon nanotube. Carbon nanotube is a very good energy efficient and low-cost material. Carbon nanotube demonstrates excellent characteristics in metallic and semiconducting characteristics by analyzing electrical properties. At first, the nanotube device physics and material properties are briefly explained in this chapter. Further, a nanotube device is designed for semiconducting properties. The gate length of nanotube is 14 nm which is placed on the gate channel. Finally, the model of 14-nm nano-transistor will be demonstrated for low-energy consumption which can be considered as a better replacement of CMOS.

Keywords: nano-transistor, 14 nm, electrical properties, I-V characteristics, low energy

### 1. Introduction

Nanoelectronics research is upgrading due to the increases of consumer demand of electronics device in small scale. Nanotechnology research area encourages the researchers to work on nanomaterials as an immerging technology for future. Carbon nanotube (CNT) is a potential material in the field on nanotechnology that has the ability to overcome almost all the limitations of other nanomaterials for its excellent electrical and mechanical properties. Therefore, one of the potential uses of CNT is to place as gate channel of a FET is called carbon nanotube field effect transistor (CNTFET). Silicon-based circuit is moving towards its physical limitation point according to the proven experiment [1]. Due to similar ballistic transport and high career portability of silicon material, CNTFET can be a good replacement of silicon [2] while CNT can

4

be acted as a semiconducting material [3, 4]. Nanotube is able to show its excellent electrical properties in designing digital devices [5, 6] in small scales. Another special characteristic also to be highlighted for nanotube is I-V features which enable to use the CNT in MOS transistors [7– 10]. According to device physics, the performance of the chip can be improved by reducing the size but there is a limitation about the reduction of silicon device size. Nano-hardware, which was created from the 1990s, has turned out to be a standout amongst the most dynamic research subjects in this day and age. The nanoelectronics innovation, which can fundamentally diminish the transistor measure, is particularly alluring to individuals. Single-walled carbon nanotube is mostly used in transistor [11]. Ballistic transport properties of MOS transistor are unchanged while the gate channel Si is substituted by nanotube [12]. In perspective of the outstanding sizelessening issues of traditional Si-based hardware, there have as of late been serious examinations on new advances in light of nano-organized materials which are shaped by sorted-out development and self get-together strategies. CVD process was used in the laboratory to grow nanotube from dielectrophoresis in early ages of its generation [13]. The first CNTFET was fabricated for prototype testing [14] which allows the researchers to work on this promising field of nanotechnology. CNTFET shows good performance in designing logic gates for integrated circuit modeling [15, 16]. Therefore, CNTFET can be a promising research in the near future.

### 2. Carbon nanotubes properties

### 2.1. Geometry of carbon nanotubes

A carbon nanotube can be characterized by chiral vector and its length and a vector called the chiral vector. Chiral vector is the sum of the multipliers of the two base vectors, like Eq. (1) [17–20]

$$C_h = ma_1 + na_2 \tag{1}$$

The coordinates of the graphene sheet (m,n) allows finding the chiral vector  $(C_h)$  of the nanotube.

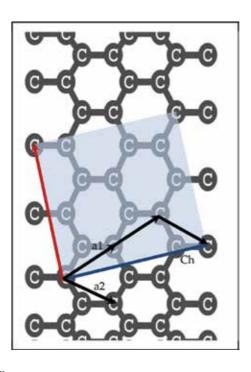

The two-dimensional graphene lattice in real space can be created by translating one unit cell by the vectors  $\overline{T} = n\overline{a}_1 + m\overline{a}_2$  with integer combinations (n, m), where  $\overline{a}_1$  and  $\overline{a}_2$  are basis vectors and is shown in **Figure 1**,

$$\overline{a}_1 = a_0 \left( \frac{\sqrt{3}}{2} \widehat{x} + \frac{1}{2} \widehat{y} \right)

\overline{a}_2 = a_0 \left( \frac{\sqrt{3}}{2} \widehat{x} - \frac{1}{2} \widehat{y} \right)$$

(2)

$a_0 = 3a_{cc}$  is the length of the basis vector, and  $a_{cc} \approx 1.42$  Å is the nearest neighbor C-C bonding distance.

Figure 1. The nanotube unit cell.

To all the more decisively acquire the moment vector T, we can get it from the m, n segments of the  $C_h$  vector. On the off-chance that we demonstrate the parts of T with  $t_1$  and  $t_2$ , as T is opposite to the  $C_h$ , the inward result of these vectors is equivalent to zero and we can conclude Eq. (3)

$$t_1 * a_1 + t_2 * a_2 = 0 (3)$$

The briefest vector  $t_1$  and  $t_2$  that are legitimate as per Eq. (3) can be isolated  $t_1$  and  $t_2$  by their most prominent normal devisor or in short shape most noteworthy basic divisor (gcd), to acquire the briefest nuclear site vector towards the path, opposite to the  $C_h$  vector.  $d_R$  as in Eq. (4),  $t_1$ ,  $t_2$  can be accomplished in Eqs. (5) and (6)

$$d_R = \gcd(m+n, 2n+m) \tag{4}$$

$$t_1 = \frac{2m+n}{d_R} \tag{5}$$

$$t_2 = \frac{2n+m}{d_R} \tag{6}$$

The angle between the chiral vector and the  $a_1$  base vector is called the chiral angle, the twist angle or the helix angle and is denoted by  $\theta_c$  and can be obtained in Eq. (7)

$$\theta_c = Arctg\left(\frac{\sqrt{3}m}{2n+m}\right) \tag{7}$$

Here, we should take note of that to consider a one of a kind chiral plot for each nanotube; the point is expressed by an incentive in the locale  $(0, 30^{\circ})$ . Utilizing these definitions, the breadth of the tube can be processed utilizing the balance of the length of the  $C_h$  and the nanotube's periphery; lastly, we can acquire the measurement characterized by

$$d_{t} = \frac{L}{\pi} = \frac{a}{\pi} \sqrt{n^{2} + nm + m^{2}}$$

(8)

The length of the chiral vector is the peripheral length of the nanotube:

$$L = |C_h| = a\sqrt{n^2 + nm + m^2} \tag{9}$$

The bandgap of a single wall nanotube (SWNT) is defined by

$$E_{\rm g} = 2\gamma_0 a_{cc}/d_t \tag{10}$$

From Eq. (4), if (n-m) is divisible by 3, then nanotube is metallic, otherwise the nanotube is semiconducting.

Now, the number of atom of the nanotube is defined by

$$N_{at} = 4*\frac{n^2 + m^2 + nm}{d_R} \tag{11}$$

### 2.2. Classification of carbon nanotubes

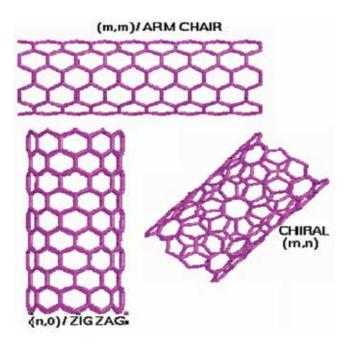

Carbon nanotube (CNT) is classified into three groups as shown in **Figure 2**: (1) armchair, (2) zigzag and (3) chiral, based on the geometrical arrangements of the graphene during the form tube formation.

If the  $C_h$  is defined as (n,0), it is given the name zigzag nanotube and if the  $C_h$  is defined as (n,n), then the tube is called armchair, and these refer to the form shaped on the circumference of the tube.

### 2.3. Carbon nanotube formation

### 2.3.1. Armchair tubes

If the chiral indices (m, n) of a nanotube in a zone-folding region can be divisible by 3, then it becomes metallic. These nanotubes are called 'zone folding metallic', or shortly,  $Z_{F-M}$  tubes.

### 2.3.2. Zigzag tubes (semiconducting tubes with bandgap)

The primary band gap of a nanotube is considered as semiconducting material if the Chirality (m, n) in the zone folding area is not divisible by 3. We should allude to these nanotubes as 'zone collapsing semiconducting', or in a matter of seconds, ZF-S tubes.

Figure 2. Classifications of different CNTs: (a) armchair, (b) zigzag and (c) chiral (François, 2009).

### 2.4. Electrical properties

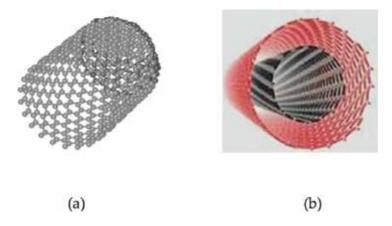

Carbon nanotubes (CNTs) have outstanding electrical properties based on the chirality. There are two types of carbon nanotube, such as single-walled carbon nanotube (SWCNT) and multiple-walled carbon nanotube (MWCNT) based on the requirements of the CNT in the integrated circuit (IC) design [21–23]. Figure 3 shows the different types of carbon nanotube. A single-walled carbon nanotube has only one shell with a small diameter usually less than 2 nm.

Figure 3. Diagram of carbon nanotube: (a) single-walled and (b) multi-walled (François, 2009).

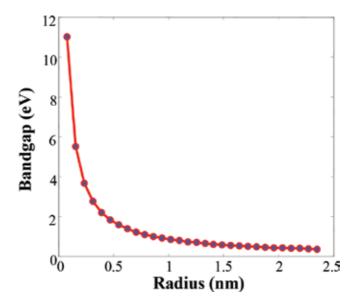

Figure 4. Bandgap versus radius for zigzag nanotube.

As well as multi-walled carbon nanotube consists of two or more concentric cylindrical shells with the diameter of 2–30 nm.

The electrical properties of a nanotube can be realized from its bandgap. Semiconducting nanotube is a novel choice for the transistor development. Thus, **Figure 4** shows bandgap versus radius for semiconducting (zigzag) nanotubes. The bandgap decreases inversely with an increase in diameter. The points with a zero bandgap correspond to metallic nanotubes which satisfy n = 3i, where i is an integer.

### 3. Modeling process of 14-nm CNTFET

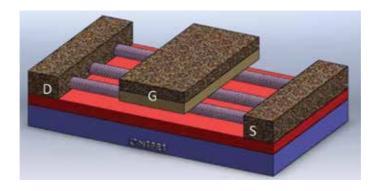

This research consists of the design and verification of the CNTFET device's small signal model. **Figure 5** shows a solid model of CNTFET with a built-in circuit model in this work.

### 3.1. CNTFET biasing

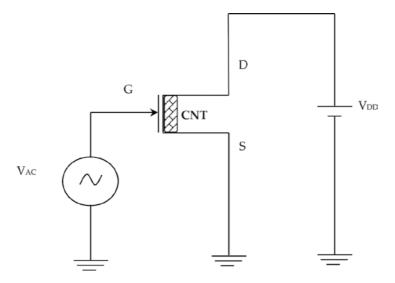

Three different types of biasing structure are seen in the CNTFET device. They are commondrain, common-gate and common-source structure. Common-source transistor circuit is considered in this modeling. The common-source circuit is shown in **Figure 6**; the DC shows bias on drain and gate with an AC signal present as the input at the gate.

Figure 5. Perspective view of the CNTFET 3D solid model.

Figure 6. Common-source biasing circuit.

### 3.2. CNTFET small signal model

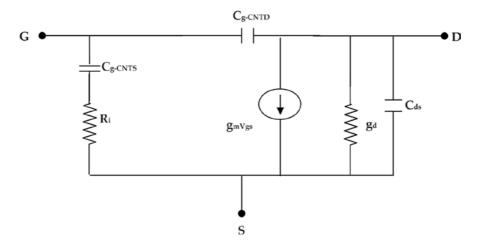

This section describes about the design and analysis of the small signal model circuit for CNTFET. The proposed small signal model of a CNTFET is shown in **Figure 7**. In **Figure 7**,  $C_{g\text{-CNTS}}$  refers to the capacitance between gate electrodes to source,  $C_{g\text{-CNTD}}$  refers to the capacitance between gate electrodes to drain,  $C_{g\text{-CNTS}}$  refers to the capacitance between gate electrodes to source, and Ri represents the internal resistance. Furthermore,  $g_m$  refers to the intrinsic transconductance and  $g_d$  refers to the drain conductance of the circuit as shown in **Figure 7**. In this circuit, the parasitic elements are excluded for the analysis purpose.

Figure 7. Intrinsic circuit model for CNTFET.

### 4. Analysis of CNTFET model

### 4.1. Transconductance of CNTFET SPICE model

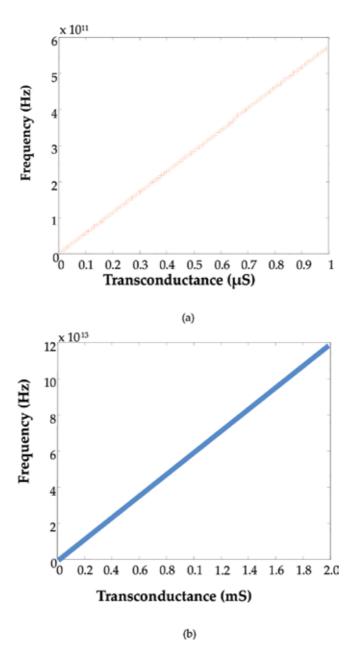

Figure 8(a) and (b) shows the simulation results of frequency versus transconductance while the transconductance is increased linearly. This is as a result with  $\mu S$  through the stage of the lower frequency as well as mS through the stage of increasing frequency. Therefore, high-frequency small signal model of CNTFET is obtained in 10 THz with 1.8 mS. On analyzing the data, we first calculate and simulate the transconductance value in  $\mu S$  and in mS.

**Figure 8(a)** shows the plot for the value of transconductance in  $\mu S$  and **Figure 8(b)** shows the plot for the value of transconductance in mS.

**Tables 1** and **2** show the selected values of transconductance necessary for the small signal model obtained from the analysis of the model as shown in **Figure 8(a)** and **(b)**. By comparing the two tables, transconductance in mS performs the higher frequency rather than to use in  $\mu$ S. Therefore, we consider transconductance in mS in this research.

### 4.2. I-V characteristics of CNTFET

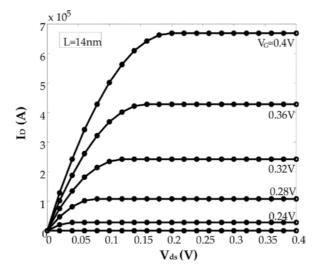

The proposed CNTFET circuit model is implemented in PSpice. A CNTFET DC characteristic is analyzed and simulated to check the output characteristics. Modeling of CNTFET with the I-V characteristics analysis is obtained from the channel length of 14 nm and width of two times the length of the proposed CNTFET. The I-V characteristic curves validate the proposed circuit model by getting drain current of  $6.9 \times 10^5$  A at the applied gate voltage of 0.4 V as shown in **Figure 9**.

Figure 8. Simulation of frequency, fT, versus transconductance, gm: (a) transconductance in  $\mu S$  and (b) transconductance in mS.

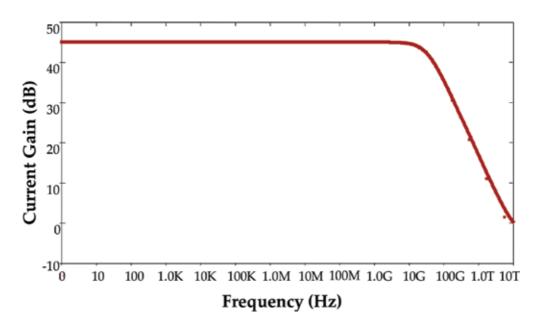

### 4.3. Frequency response of CNTFET

The current gain of the proposed CNTFET is shown in **Figure 10**. Current gain magnitude is found in 45 dB while the frequency is operated in 10 THz. The value of the CNTFET's

| Gm (µS) | F <sub>T</sub> (Hz)     |

|---------|-------------------------|

| 19      | $1.0800 \times 10^{11}$ |

| 22      | $1.2505 \times 10^{11}$ |

| 28      | $1.5915 \times 10^{11}$ |

| 32      | $1.8189 \times 10^{11}$ |

| 36      | $2.0463 \times 10^{11}$ |

| 45      | $2.5578 \times 10^{11}$ |

| 50      | $2.8421 \times 10^{11}$ |

| 55      | $3.1263 \times 10^{11}$ |

| 60      | $3.4105 \times 10^{11}$ |

Table 1. Frequencies for different current gain of small signal model while transconductance in  $\mu S$ .

| Gm (mS) | F <sub>T</sub> (Hz)    |  |

|---------|------------------------|--|

| 1.0     | $5.68 \times 10^{12}$  |  |

| 1.1     | $6.25 \times 10^{12}$  |  |

| 1.2     | $6.82 \times 10^{12}$  |  |

| 1.3     | $7.39 \times 10^{12}$  |  |

| 1.5     | $8.52 \times 10^{12}$  |  |

| 1.6     | $9.00 \times 10^{12}$  |  |

| 1.7     | $9.66 \times 10^{12}$  |  |

| 1.8     | $10.00 \times 10^{12}$ |  |

Table 2. Frequencies for different current gain of small signal model while transconductance in mS.

Figure 9. I-V transfer characteristics of CNTFET.

Figure 10. Output current gain of the CNTFET at 10-THz frequency.

| <b>Device Parameters</b> | CNTFET [25] | This Research |

|--------------------------|-------------|---------------|

| Current gain (db)        | 20          | 45            |

| g <sub>m</sub> (mS)      | 3.8         | 1.8           |

| $C_{gs}(F)$              | 65f         | 14a           |

| C <sub>gd</sub> (F)      | 52f         | 14a           |

| Cut-off-Freq (Hz)        | 30G         | 10T           |

Table 3. Comparison of current research.

transconductance gm is set as 1.8 mS from the analysis as shown in **Figure 10** at the gate voltage of 0.4 V [24].

To validate the output characteristics of the current development of proposed CNTFET, we compare the work with other researches. **Table 3** shows the comparison of the performance of the proposed model. From this performance comparison, we would like to conclude that the proposed CNTFET model is capable of operating in high frequency.

### 5. Conclusion

This chapter discussed the development of the CNTFET model using 14-nm technology. We delineated a short examination of the proposed plan of CNTFET little banner show. The arrangement contains a suitable blueprint of the little banner procedure and demonstrated the displays by re-enacting little banner parameters for CNTFET with respect to that of 45 dB.

The inherent capacitance of 14 aF and transconductance of 1.8 mS are used as a piece of this examination. A benchmark is showed up for the immense execution of the exhibit made by differentiating and late research data. Particular characteristics are showed up by a course of action of multiplication. Besides, this system has familiar capacitance with survey, the charge defending capacitance at the repeat of 10 THz.

### Acknowledgements

The author would like to thank the International Islamic University Malaysia for giving her the opportunity to perform this research.

### Conflict of interest

There is no conflict of interest with this publication.

### **Author details**

Soheli Farhana

Address all correspondence to: soheli.farhana@live.iium.edu.my

International Islamic University Malaysia, Kuala Lumpur, Malaysia

### References

- [1] Sinha S, Balijepalli A, Cao Y. Compact model of carbon nanotube transistor and interconnect. IEEE Transactions on Electron Devices. 2009 Oct;56(10):2232-2242

- [2] Li H, Xu C, Srivastava N, Banerjee K. Carbon nanomaterials for next-generation interconnects and passives: Physics, status, and prospects. IEEE Transactions on Electron Devices. 2009 Sep;56(9):1799-821

- [3] Javey A, Wang Q, Ural A, Li Y, Dai H. Carbon nanotube transistors arrays for multistage complementary logic and ring oscillators. Nano Letters. 2002;2:929-932

- [4] Guo J, Javey A, Dai H, Lundstrom M. Performance analysis and design optimization of near ballistic carbon nanotube FETs. IEDM Technical Digest. 2004:703-706

- [5] Bagherizadeh M, Eshghi M. Two novel low-power and high-speed dynamic carbon nanotube full-adder cells. Nanoscale Research Letters. 2011;6:519

- [6] Maehashi K, Kishimoto T, Ohno Y, Inoue K, Matsumoto K. Fabrication of highperformance voltage inverters based on carbon nanotube field-effect transistors. In: IEEE Nanotechnology Materials and Devices Conference; 2010

- [7] Das S, Bhattacharya S, Das D. Modeling of carbon nanotube based device and interconnect using VERILOG-AMS. In: Proceedings of the International Conference on Advances in Recent Technologies in Communication and Computing. 2011. pp. 51-55

- [8] Das S, Bhattacharya S, Das D. Design of digital logic circuits using carbon nanotube field effect transistors. International Journal of Soft Computing and Engineering. 2011 Dec;1(6): 173-178

- [9] Das S, Bhattacharya S, Das D. Design of transmission gate logic circuits using carbon nanotube field effect transistors. In: Proceedings of the National conference on Advanced Communication Systems and Design Techniques. 2011. pp. 75-78

- [10] Das S, Bhattacharya S, Das D. Performance evaluation of CNTFET-based logic gates using Verilog-AMS. In: Proceedings of the National Conference on Electronics, Communication and Signal Processing. 2011. pp. 85-88

- [11] Koo Y, Littlejohn G, Collins B, Yun Y, Shanov VN, Schulz M, et al. Synthesis and characterization of Ag–TiO2–CNT nanoparticle composites with high photocatalytic activity under artificial light. Composites Part B: Engineering. 2014;57:105-111

- [12] Hoque M, Ahmad H, Reza A. Design optimization of high frequency Op Amp using 32 nm CNFET. In: 6th International Conference on Electrical and Computer Engineering ICECE; 2010

- [13] Kim S, Wang C, Shim M, Mohammadi S. Comparison of single-walled carbon nanotube transistors fabricated by dielectrophoresis and CVD growth. In: Proceedings of 5th IEEE Conference on Nanotechnology. Nagoya, Japan; 2005

- [14] Kim Y. Integrated circuit design based on carbon nanotube field effect transistor. Transactions on Electrical and Electronic Materials. 2011;12(5):175-188

- [15] Hameem Shanavas I, Brindha M, Nallusamy V. An analogous computation of different techniques for the digital implementation of inverter and NAND logic gates. International Journal of Information Engineering and Electronic Business. 2012;4(4):33-38

- [16] Zhang X, Luo D, Cui G, Wang Y, Huang B. Construction of logic gate based on multichannel carbon nanotube field-effect transistors. In: Intelligent Human-Machine Systems and Cybernetics (IHMSC), International Conference; 2011. IEEE; August, 2011. Vol. 2, pp. 94-97

- [17] Farhana S, Alam AHMZ. Carbon nanotubes: A review on future generation Nano device. Middle-East Journal of Scientific Research. 2014;**20**(1):74-81

- [18] Farhana S. Novel carbon nanotube model for low energy loss field-effect transistor. Cogent Engineering. 2017;4(1):1300082

- [19] Farhana S, Alam AHMZ. Modeling and simulation of CNTFET small signal model. In: 2014 IEEE 6th International Nanoelectronics Conference (INEC); 28-31 July 2014; Hokkaido, Japan. 2014. http://irep.iium.edu.my/39069/

- [20] Farhana S, Alam AHMZ, Khan S. DIBL and subthreshold swing effect on carbon nanotube field effect transistor. In: Proceedings of the World Congress on Engineering. 2015. Vol. 1, pp. 455-458

- [21] Gokturk HS. Electrical properties of ideal carbon nanotubes. In: Nanotechnology. 5th IEEE Conference; 2005. IEEE; July, 2005. pp. 677-680

- [22] Krompiewski S. Electronic transport through side-contacted graphene nanoribbons: Effects of overlap, aspect ratio and orientation. Nanotechnology. 2011;22(44):445201

- [23] Sanudin R. Characterisation of ballistic carbon nanotube field-effect transistor [doctoral dissertation]. Malaysia: Universiti Teknologi; 2005

- [24] Farhana S, Alam AZ, Khan S. Small band-gap-based CNT for modeling of nano sensor. Procedia Computer Science. 2014;42:122-129

- [25] Coskun K, Simon D, Qing C, Kurt C, Xinning H, Hoon-Sik K, Dawson D, Payne J, Stuenkel M, Zhang H, Banks T, Feng M, Rotkin SV, Rogers JA. High-frequency performance of submicrometer transistors that use aligned arrays of single-walled carbon nanotubes. Nano Letters. 2009;9(5):1937-1943

### **Dielectric-Modulated TFETs as Label-Free Biosensors**

Rupam Goswami and Brinda Bhowmick

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.76000

### **Abstract**

This chapter presents tunnel field effect transistors (TFETs) as dielectric-modulated (DM) label-free biosensors, and discusses various aspects related to them. A brief survey of the dielectric-modulated TFET biosensors is presented. The concept of dielectric modulation in TFETs is discussed with focus on principle and design perspectives. A Technology Computer Aided Design (TCAD) based approach to incorporate embedded nanogaps in TFET geometries along with appropriate physics-based simulation models are mentioned. Non-ideal conditions in dielectric-modulated biosensors are brought to light, keeping in view the practical considerations of the devices. A gate engineered TFET is taken up for analysis of sensitivities under different conditions through TCAD simulations. Finally, a status map of the sensitivities of the most significant works in dielectric-modulated label-free biosensors is depicted, and the status of the proposed TFET is highlighted.

Keywords: TFET, biosensor, dielectric modulation, biomolecules, sensitivity

### 1. Introduction

The dependence of economics of the semiconductor industry on Moore's Law led to the downscaling of device dimensions in metal oxide semiconductor field effect transistors (MOSFETs) in order to accommodate more transistors in the same chip area. As the device dimensions were scaled down to the nanometer regime, degradation in the performance of MOSFETs in the form of short channel effects (SCEs) was observed. The inversion charge sharing by the source and drain regions in short channel MOSFETs led to problems of drain induced barrier lowering (DIBL), threshold voltage roll-off, mobility degradation and high field saturation [1–3]. These problems hindered the progress of MOSFETs towards low power applications which required reduced supply voltage and targets of low off currents. Since

then, the semiconductor industry has been on the lookout for novel devices which can effectively address the issues of scaling and depict performance which is superior to MOSFETs.

Over the past few decades, industries and researchers have proposed a number of devices as prominent alternatives to MOSFETs for low power applications. Most of these devices possess principles of operation which are different from MOSFETs. The International Technology Roadmap for Semiconductors in its document 'Beyond CMOS' published in 2015 reported the emerging devices based on structure or materials and charge/non-charge entity [4]. This include a number of devices like nanowire FET [5–7], carbon nanotube FET [8–10], graphene FET [11–13], TFET [14–16], spin FET [17–19] and negative gate capacitance FET [20, 21]. Of these devices, TFETs have gained concentrated focus for low power applications due to their fundamental fabrication methodologies being similar to MOSFETs, and their ability to achieve sub-60 mV/dec subthreshold swing and lower off currents than MOSFETs. TFETs operate by interband tunneling mechanism unlike thermionic emission in MOSFETs due to which the high energy tails of the Fermi distribution of carriers while moving from source to drain get curtailed, resulting in low subthreshold swings and off currents. Different architectures of TFETs have been proposed till date to improve their performance and increase the on currents. [22, 23], nanowire TFET [24, 25], heterojunction TFET [26, 27], III-V TFET [28], triple material gate TFET [29, 30], cylindrical TFET [31] and SOI TFET [32] are some of the widely used structures.

TFETs have found their uses in a wide range of low power applications like digital circuits and memory applications [33–35]. However, recently, the emergence of FET-based biosensors has projected TFETs as biosensors based on dielectric modulation in which the dielectric constant along with the charge of the biomolecules in the gate dielectric region affect the drain current [36]. The sensitivity of the biosensor in presence of biomolecules is defined with respect to a reference value. A number of geometries of TFETs has been proposed as dielectric-modulated biosensors, and the analyses of their sensitivities having dependence on device parameters have been reported [37–41].

Section 2 of this chapter presents a brief report on the existing works on FET-based biosensors. In Section 3, the principle of dielectric modulation in TFETs and a reference architecture for TFETs as biosensors are discussed. Section 4 mentions the different physics-based models to be considered while simulating a TFET on a Technology Computer Aided Design (TCAD) tool. The different sensitivities are defined in Section 5. Section 6 mentions the various non-ideal conditions that may possibly exist in case of FET-based biosensors. A circular gate TFET is analyzed as a dielectric-modulated biosensor through TCAD simulation in Section 7. Section 8 concludes the chapter and comments on future scope.

### 2. A brief survey

The compactness, compatibility in fabrication and label-free detection have made FET-based biosensors one of the promising area of interests. Generally, there are two methods to detect the presence of biomolecules: gating effect and dielectric modulation. The gating effect uses

the gate dielectric material with receptors on its surface to immobilize the biomolecules [42]. Dielectric modulation, on the other hand, employs the effect of change in dielectric constant in a portion of the gate dielectric on the drain current and the associated electrical parameters [37–41]. The gating effect is effective for detecting charged biomolecules, while dielectric modulation can assist in sensing charged and neutral biomolecules.

Im et al. proposed a dielectric-modulated (DM) FET-based biosensor [36] after the ion sensitive FETs proposed in 1970s [43]. Sarkar and Banerjee presented a nanowire TFET in [42] demonstrating the gating effect for positively charged biomolecules. It is convenient to assume that the embedded nanogap is completely filled with biomolecules. However, Kim et al. reported on partially filled nanogaps in practical cases due to steric hindrance, and proposed a parameter, fill factor, defined as the percentage of the nanogap occupied by biomolecules [44]. Narang et al. provided similar simulation analyses for partially filled nanogaps for DM FET and PNPN TFET [11]. Narang et al. further presented a Poisson equation based analytical model to account for the effect of dielectric modulation in TFETs [38]. Partially filled nanogaps decrease the response of the biosensor, as the effective dielectric constant varies with position within the nanogap. Abdi and Kumar proposed the concept of deriving the sensitivity through ambipolar current in TFET [45]. Ahangari presented reports of a dual material gate nanowire junctionless TFET as a biosensor [46]. As the nanogap length increased, the sensitivity improved considerably. Kanungo et al. reported that a short gate dielectric-modulated TFET biosensor showed improved sensitivity than a full gate dielectricmodulated TFET [40].

### 3. Dielectric modulation in TFETs: concept and geometry

### 3.1. Principle of operation

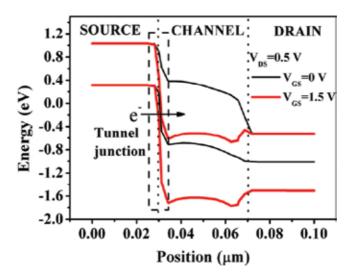

A conventional homojunction TFET is a gated reverse-biased p-i-n structure [3]. As opposed to the thermionic emission in MOSFETs, the mechanism of transport in TFETs is band-to-band tunneling. In an n-TFET, when positive gate bias increases, the energy bands get suppressed as a result of which the width between the p + source valence band, and i-channel conduction bands reduces, thus facilitating the tunneling of electrons from the former to the latter as depicted in **Figure 1** [3]. This contributes to the drain current.

The tunnel barrier at the source-channel junction is modeled as a triangular barrier, and using WKB approximation, its tunneling probability is calculated as [47].

$$T(E) = exp\left(-\frac{4\lambda\sqrt{2}\,m^*\,E_G^{3/2}}{3q\hbar(\Delta\Phi + E_G)}\right) \tag{1}$$

where m\* is the effective mass,  $E_c$  is the energy band gap at the source-channel tunnel junction,  $\Delta \Phi$  is the energy overlap of the bands at tunnel junction,  $\lambda$  is the screening tunneling length, q is the electronic charge, and  $\hbar$  is the reduced Planck's constant. The screening length  $\lambda$  is defined as [47].

Figure 1. Energy band diagram of a p-i-n TFET showing the on and off states.

$$\lambda = \sqrt{\left(\varepsilon_{s}/\varepsilon_{ov}\right)t_{s}t_{ov}} \tag{2}$$

The dielectric modulation in a MOS-based device, and particularly TFETs is the alteration in the dielectric constant in the gate dielectric region of the device. Keeping other parameters constant, the effect of dielectric modulation in TFET is best explained by the parameters,  $\lambda$  and  $\Delta\Phi$ . A low dielectric constant decreases the gate-to-channel coupling as a result of which the tunnel width is more even at high gate voltages, as compared to the presence of higher gate dielectric constants at the tunnel junction [3, 47, 48]. This results in a low tunneling probability, and hence, low tunneling current. Lesser the gate-to-channel coupling, lesser is the amount of  $\Delta\Phi$  at the tunnel junction.

A 2-D Poisson's equation based model of TFET results in a closed form equation of drain current as [49].

$$I_{DS} = W T_{Si,eff} \frac{E_G}{W_{t,min}^2} \cdot \frac{A_K}{B_K} \cdot exp\left(-\frac{B_K E_G}{q W_{t,min}}\right)$$

(3)

where, W is the width of the device,  $T_{s_{i,eff}}$  is the effective Silicon body thickness,  $E_G$  is the band gap of the semiconductor,  $W_{t,min}$  is the minimum tunneling width,  $A_k$  and  $B_k$  are material dependent constants. Equation (3) suggests the dependence of drain current on the minimum tunnel width which, in turn, is dependent on the dielectric constant of the gate insulator region near the tunnel junction. Therefore, as dielectric constant of the nanogap increases,  $W_{t,min}$  decreases, and drain current increases.

Another prospect of utilizing dielectric modulation for biosensing is by placing the embedded nanogap towards the channel-drain junction of the TFET, and exploit its ambipolarity [45]. For a conventional n-TFET, when the drain voltage is positive, and gate voltage is negative,

the energy bands at the channel-drain junction get influenced so as to form a tunneling barrier. This results in flow of current by tunneling at this junction. This becomes the reason for anomalies in complementary TFET digital circuits. However, as far as label-free biosensing is concerned, this ambipolar current can be considered as a measure of sensitivity in TFETs.

### 3.2. Geometry

As evident from Section 3.1, the objective of utilizing dielectric modulation for biosensing requires a modified geometry with the following basic requirements

- The biomolecules must be immobilized in the gate dielectric region. To realize this, a nanogap is required in the gate dielectric. The gate dielectric, therefore, is composed of two regions; apparently, it works like a dual gate dielectric device, where one gate dielectric has a fixed dielectric constant, and the other carries the dielectric constant of the biomolecules.

- The height of the embedded nanogap must be large enough to allow the entry of biomolecules into the cavity or nanogap. A minimum height of 10–11 nm is usually considered for simulation analyses in nanoscale TFETs.

- In order to accommodate more biomolecules, a double gate structure with the above designs may be employed.

- The TFETs must have appropriate source doping. A few biomolecules have dielectric constants of 2 or 3 [39–42], which is closer to the dielectric constant of 1. So, the geometry must be so designed that it is able to respond to immobilization of biomolecules having low dielectric constants as well.

- For TFETs which utilize the ambipolar behavior of the devices, the drain doping concentration is more important.

### 4. Simulation strategy for a DM TFET as a label-free biosensor

The most convenient way to analyze a biosensor is on a computational platform where the physics-based models applied to the architecture assist in analyzing its performance. There are a number of industrial simulators and most of them come equipped with provisions for defining a geometry and feeding it through iterations of selective models available in their libraries.

The embedded nanogap in a DM TFET is designed by substituting that region in the gate dielectric with a dielectric material (oxide) whose dielectric constant can be altered as per requirement [38]. For charged biomolecules, the charges are considered at the oxide-semi-conductor interface. By varying the dielectric constant and the charge, the immobilization of biomolecules may be mimicked appropriately.

The models for TFETs must be chosen with care. Since TFETs usually have high source doping concentration to achieve large band bending at equilibrium, therefore, Fermi-Dirac statistics

is necessary [50]. Bandgap narrowing is important for heavily doped geometries [50]. Non-local band-to-band tunneling models are essential to create a suitable simulation environment for the device whose principle of operation is interband tunneling [50]. Field dependent mobility models may be used [50].

### 5. Sensitivity parameters

The performance of a TFET or any MOS-based device is reflected through its electrical parameters. The most commonly used parameters for defining sensitivity are the drain current and threshold voltage. Subthreshold swing (SS) may also be considered for defining a sensitivity parameter; however, the measurement of SS is dependent on the orders of the logarithmic scale over which the drain current is measured. This value or the measurement may not be consistent as the drain current changes with the variation in the dielectric constant of the immobilized biomolecules. Sensitivities are usually defined with respect to reference values. The reference value in case of a dielectric-modulated biosensor is considered when the nanogap is devoid of biomolecules, and hence, is assumed to be filled with air with a dielectric constant of 1 without any charges at the oxide-semiconductor interface. The drain current based sensitivity is mathematically expressed as [44].

Sensitivity,

$$S_I = \frac{I_{D,k}}{I_{D,k=1}} \bigg|_{V_{CS}}$$

(4)

where  $I_{D,k}$  and  $I_{D,k-1}$  are the values of drain currents when the nanogap is filled with biomolecules and the nanogap is unfilled. The values must be measured at the same gate voltage so as to get a justified value of sensitivity.

The threshold voltage has a dependence on the dielectric constant of the gate dielectric and charge at the semiconductor-oxide interface. The shift in threshold voltage with the immobilization of biomolecules with different dielectric constants may be taken up as a sensitivity parameter. It is mathematically expressed as

Sensitivity,

$$S_{V_{\tau}} = V_{T,k=1} - V_{T,k}$$

(5)

where  $V_{T,k}$  and  $V_{T,k=1}$  are the threshold voltages for the cases when the nanogap is filled with biomolecules and when the nanogap is completely unfilled.

There are many threshold voltage extraction methods for MOSFETs, and TFETs. Of them, the Linear Extrapolation (LE) Method is the most widely used [51, 52]. According to this extraction principle, the intercept on the gate voltage axis made by the tangent to the drain current curve corresponding to the maximum value of  $g_m = dI_D/dV_{CS}$  is defined as the threshold voltage. Although this extraction method may result in change in threshold voltage with change in range in gate voltage, however, we have considered a fixed range of gate voltage in all the cases of comparison. So, we have used this method of threshold voltage extraction from simulation transfer characteristics.

### 6. Non-idealities in dielectric-modulated biosensors

While simulating a geometry of a DM TFET as on a TCAD tool to assess its biosensing capacity, it is convenient to assume that the nanocavity is completely filled with the biomolecules. However, in practical cases, the issues of steric hindrance and probe placement do not allow the embedded nanogap to be completely filled [39]. As a result, partially filled nanogaps are formed.

### 6.1. Steric hindrance

In case of steric hindrance, the biomolecules which get immobilized first prevent the further entry of biomolecules. In fact, there is a hindrance to the biomolecules which are likely to get immobilized in the nanogaps, resulting in partial hybridization. In order to account for this on a TCAD tool for simulation, different patterns of immobilization inside the nanogap are assumed, like increasing, decreasing, concave and convex profiles of placement [39]. As explained in Section 2, this can be designed by defining different heights of gate dielectric material mimicking the biomolecules according to the profile of biomolecules.

### 6.2. Probe placement

In order to immobilize the biomolecules, probes or receptors are used in the nanogap. The placement of probes in the nanogap for immobilization of biomolecules may not be continuous throughout, and this may result in partially filled nanogaps [39]. For simulation, this may be considered in a similar manner as the steric hindrance except that the profiles shall not be continuous as in steric hindrance.

### 6.3. Fabrication issues

The nanogap which is formed in a DM biosensor is carved out by forming a native oxide first, and then etching out the native oxide [38]. This method, however, is challenging, and practically, there is possibility that damages result from the process. These anomalies include creation of trap centers at the interface or incomplete etch of the native oxide along with traps in the residual gate dielectric [38]. The phenomenon of tunneling in a TFET is highly dependent on its source-channel tunnel junction, and the alignment of the gate with the junction. During fabrication, the gate edge may be displaced from the junction. This may result in an overlap or an underlap depending on whether the gate shifts towards the source or the channel respectively. In case of a gate-source overlap, the characteristics of the TFET generally improve as the shifted gate can now influence the energy bands in the source-channel junction with better control. However, in case of an underlap, the gate edge moves away from the junction, and the tunnel junction is least affected by it.

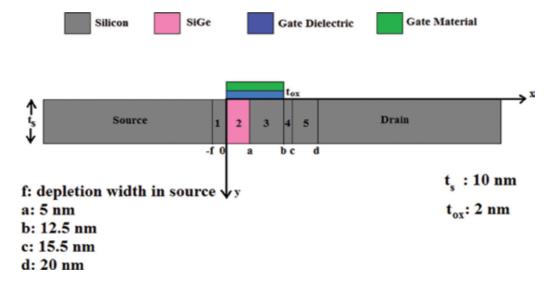

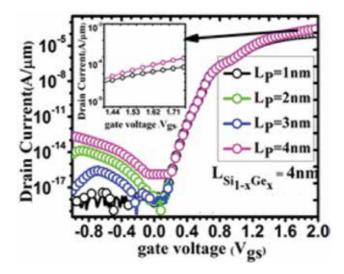

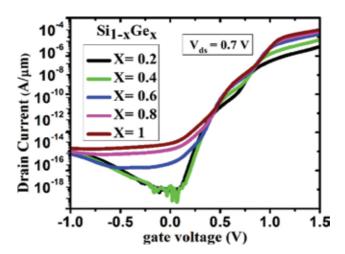

### 7. A circular gate TFET as a DM biosensor

This section presents a geometry of TFET, a Circular Gate TFET (CG) as a dielectric-modulated biosensor, and discusses some of the results. The CG TFET has a non-uniform gate in the

form of a semi-circle. This gate engineering introduces flexibility into the architecture of the device, and aids in optimization of chief electrical parameters, primarily the ambipolar current and ratio of on and off currents [53]. One of the techniques of reducing ambipolar current in a TFET apart from asymmetric source-drain doping is the introduction of gate-drain underlap [3, 45, 53]. In case of Circular Gate TFET, the gate being circular in shape, the gate dielectric thickness is dependent on the radius of the circle. A gate-drain underlap in the architecture shall decrease the thickness of the gate dielectric, which shall, in turn, increase the influence of the gate on the channel. Therefore, reduced ambipolar current can be achieved with appropriate ratio of on and off current simultaneously.

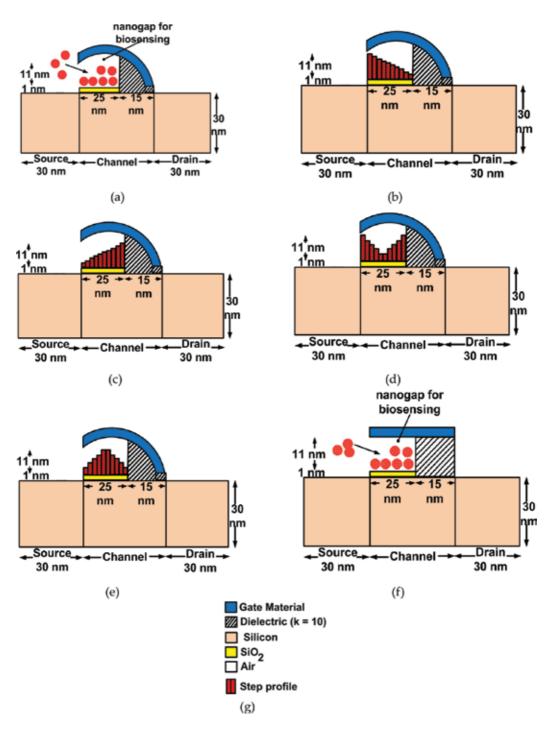

A circular gate TFET as a DM biosensor is depicted in **Figure 2a**. The total length of the Silicon body TFET is 100 nm, where the source and drain are 30 nm each. An embedded nanogap is incorporated into the geometry to immobilize the biomolecules. The embedded nanogap is usually etched out of a dielectric formed by a native oxide. We have considered a native oxide of 1 nm in the nanogap, which is assumed to remain after the gap is etched out.

### 7.1. Fully filled nanogap

Firstly, we assume that the entire embedded nanogap of the CG TFET in **Figure 2b** is filled with biomolecules, and observe the influence of different factors on its sensitivity. The Fill Factor of an embedded nanogap is defined as the ratio of the area covered by immobilized biomolecules to the total area of the nanogap, and is generally expressed in percentage. For a fully filled nanogap, the Fill Factor is 100%.

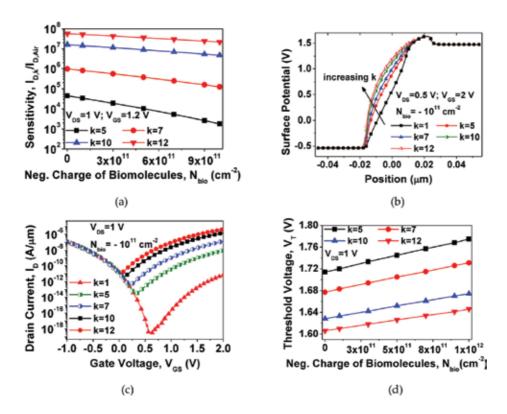

### 7.1.1. Negatively charged biomolecules

The sensitivity of the CG TFET as a biosensor with fully filled nanogap is plotted for negative charge of biomolecules for k = 5, 7, 10 and 12 in **Figure 3a**. With the increase in magnitude of negative charge, the sensitivity decreases. The presence of negatively charged biomolecule- $SiO_2$  interface prevents depletion of the p-type channel, thus requiring a higher gate voltage than a neutral interface to deplete the p-type substrate, and cause reduction in tunnel width. The voltage balance equation of a metal-oxide-semiconductor structure is represented as [54].

$$V_G = \psi_s + \Phi_{MS} - \frac{q N_{bio}}{C_{os}^{\prime}} \tag{6}$$

where,  $V_G$  is the gate voltage,  $\Psi_S$  is the electrostatic potential at the surface,  $\Phi_{MS}$  is the difference between the work functions of metal and semiconductor, q is the value of electronic charge,  $N_{hi}$  denotes the number of charges per unit area, and  $C_{ex}$  is resultant capacitance per unit area. Furthermore,

$$C'_{ox} = \frac{k}{t_{ox}(\alpha)} \tag{7}$$

where k is the dielectric constant, and  $t_{\alpha}(x)$  is the dielectric thickness as a function of lateral position due to the circular gate.

**Figure 2.** 2-D schematic of dielectric-modulated biosensors: (a) CG TFET, (b) decreasing step profile of biomolecules, (c) increasing step profile of biomolecules, (d) concave step profile of biomolecules, (e) convex step profile of biomolecules, (f) MOSFET, and (g) legend for all the 2D schematics.

**Figure 3.** (a) Sensitivity versus negative charge of biomolecules for dielectric constant, k = 5, 7, 10 and 12; (b) surface potential versus position from source to drain at gate voltage 2 V, drain voltage 0.5 V, and  $N_{bio} = -10^{11}$  cm<sup>-2</sup> for dielectric constant, k = 1, 5, 7, 10 and 12; (c) transfer characteristics of CG TFET as biosensor for k = 1 (air), 5, 7, 10 and 12 at fixed negative charge,  $N_{bio} = -10^{11}$  cm<sup>-2</sup>; (d) threshold voltage versus negative charge of biomolecules for dielectric constant, k = 5, 7, 10 and 12.

Considering a fixed gate voltage, as the negative charge of biomolecules increases,  $\Psi_s$  must decrease in order to satisfy the potential balance in Eq. (6). As a result, the drain current decreases, thus reducing the sensitivity.

The change in sensitivity of the sensor with increasing magnitude of negative charge is more in case of a low dielectric constant and reduces as the dielectric constant of the nanogap increases. At k = 5, the sensitivity decreases by a factor of 25 when the charge of the immobilized biomolecules changes from neutral to  $-10^{12}$  cm<sup>-2</sup> as compared to k = 12, where it drops by 2.61. In Eq. (6), at fixed negative  $N_{bio}$  and  $V_{cs'}$  as k in Eq. (7) increases, the potential  $-\frac{qN_{bio}}{C_{ci}}$  decreases, resulting in a corresponding increase in  $\Psi_s$ . This increases the drain current, and hence, the sensitivity of the biosensor. This effect is demonstrated in **Figure 3b**.

**Figure 3c** shows the plots of transfer characteristics of a fully filled nanogap CG TFET biosensor at drain voltage 1 V and charge of biomolecules equal to  $-10^{11}$  cm<sup>-2</sup>. The absence of biomolecules corresponds to k = 1 with no charge at the air-SiO<sub>2</sub> interface as the nanogap remains devoid of biomolecules. Due to the presence of unaltered gate dielectric towards the channel-drain junction of the geometry, therefore, the ambipolar current is same for all dielectric constants of the nanogap. The dielectric constant of the fully filled nanogap closer to the

source-channel tunnel junction has an impact on the drain current. However, as the dielectric constant increases, the minimum value of drain current shifts to the left, thus, verifying the increase in gate capacitance. This corresponds to a decrease in the threshold voltage as shown in **Figure 3d**. The threshold voltage exhibits a high shift with increasing negative charge for low-k biomolecules as compared to high-k cases. For k = 5, the threshold voltage increases by 3.56% as the charge of the immobilized biomolecules change from neutral to  $-10^{12}$  cm<sup>-2</sup> as compared to k = 12 where the increase is relatively small, that is, 2.49%.

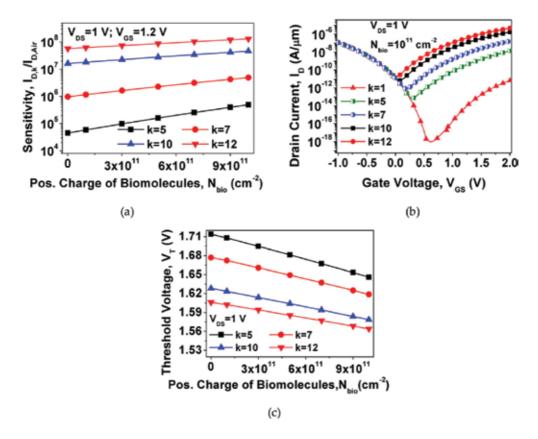

## 7.1.2. Positively charged biomolecules

Like Section 7.1.1, similar plots are presented here for positive charge of biomolecules. The variation of sensitivity with increasing positive charges for k = 5, 7, 10 and 12 is shown in **Figure 4a**. The positive charge of biomolecules depletes the p-type channel, and causes more tunneling of electrons at the source-channel tunnel junction. Hence, the sensitivity increases. For k = 5, the sensitivity increases by a factor of 11 when the charge changes from neutral to  $10^{12}$  cm<sup>-2</sup>, whereas for k = 12, the factor is 2.29. The explanation for the trend of the plot can be made in a similar manner as in Section 7.1.1 with the help of Eqs. (6) and (7).

**Figure 4.** (a) Sensitivity versus positive charge of biomolecules for dielectric constant, k = 5, 7, 10 and 12; (b) transfer characteristics of CG TFET as biosensor for k = 1 (air), 5, 7, 10 and 12 at fixed negative charge,  $N_{bio} = 10^{11}$  cm<sup>-3</sup>; (c) threshold voltage versus positive charge of biomolecules for dielectric constant, k = 5, 7, 10 and 12.

**Figure 4b** depicts the transfer characteristics of the CG TFET for k = 5, 7, 10, and 12 at  $N_{bio} = 10^{11}$  cm<sup>-2</sup>. The on current in case of positive charged biomolecules is higher than that in case of negatively charged biomolecules as evident from **Table 1**.

In **Figure 4c**, for k = 5, the threshold voltage decreases by 4.03% when the charge changes from neutral to  $10^{12}$  cm<sup>-2</sup>, whereas for k = 12, the drop is 2.68%.

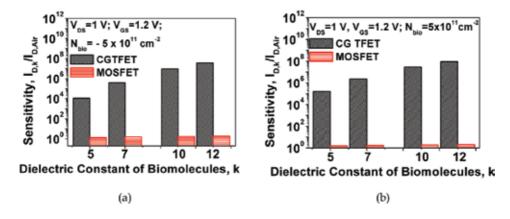

## 7.1.3. Sensitivities of DM CG TFET and MOSFET

The comparisons of sensitivities of CG TFET and MOSFET are shown in **Figure 5a** and **b**. At  $N_{bio} = \pm 5 \times 10^{11}$  cm<sup>-2</sup>, the values are extracted for k = 5, 7, 10, and 12. The MOSFET with exactly equal nanogap height and length as that of CG TFET exhibits extremely inferior sensitivity as compared to CG TFET. Earlier works on dielectric-modulated MOSFET have reported similar poor sensitivity of the device as compared to TFET [38, 39].

| Sl. No.                       | Biosensors                                                                                                               | Reference     |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------|

| (horizontal axis of Figure 7) |                                                                                                                          |               |

| 1                             | Conventional FET                                                                                                         | [42]          |

| 2                             | Nanowire TFET                                                                                                            |               |

| 3                             | DM FET ( $L_{GAP} = 200 \text{ nm}$ , $H_{GAP} = 15 \text{ nm}$ , $k = 2.1$ )                                            | [36]          |

| 4                             | DM FET ( $L_{GAP} = 100 \text{ nm}$ , $H_{GAP} = 15 \text{ nm}$ , $k = 2.1$ )                                            |               |

| 5                             | Full Gate DMTFET ( $L_{GAP}$ = 10 nm, $L_{GATE}$ = 42 nm, $H_{GAP}$ = 5 nm, $k$ = 4)                                     | [40]          |

| 6                             | Short Gate DMTFET ( $L_{GAP} = 10 \text{ nm}$ , $L_{GATE} = 20 \text{ nm}$ , $H_{GAP} = 5 \text{ nm}$ , $k = 4$ )        |               |

| 7                             | DM FET ( $L_{GAP} = 30 \text{ nm}$ , $L_{GATE} = 100 \text{ nm}$ , $H_{GAP} = 9 \text{ nm}$ , $k = 10$ )                 | [39]          |

| 8                             | DM FET ( $L_{GAP} = 75 \text{ nm}$ , $L_{GATE} = 250 \text{ nm}$ , $H_{GAP} = 9 \text{ nm}$ , $k = 10$ )                 |               |

| 9                             | DM PNPN TFET ( $L_{GAP}$ = 30 nm, $L_{GATE}$ = 100 nm, $H_{GAP}$ = 9 nm, $k$ = 10)                                       |               |

| 10                            | DM PNPN TFET ( $L_{GAP}$ = 75 nm, $L_{GATE}$ = 250 nm, $H_{GAP}$ = 9 nm, $k$ = 10)                                       |               |

| 11                            | DM STS I-MOS ( $L_{GAP} = 50 \text{ nm}, L_{GATE} = 120 \text{ nm}, H_{GAP} = 15 \text{ nm}, k = 10$ )                   | [55]          |

| 12                            | SiGe Source DM PNPN TFET, Ge composition = 0% ( $L_{GAP}$ = 15 nm, $L_{GATE}$ = 100 nm, $H_{GAP}$ = 9 nm, $k$ = 2.1)     |               |

| 13                            | SiGe Source DM PNPN TFET, Ge composition = 10% ( $L_{GAP}$ = 15 nm, $L_{GATE}$ = 100 nm, $H_{GAP}$ = 9 nm, $k$ = 2.1)    | [41]          |

| 14                            | SiGe Source DM PNPN TFET, Ge composition = 20% ( $L_{GAP}$ = 15 nm, $L_{GATE}$ = 100 nm, $H_{GAP}$ = 9 nm, $k$ = 2.1)    |               |

| 15                            | CG TFET ( $L_{GAP} = 25 \text{ nm}, L_{GATE} = 40 \text{ nm}, H_{GAP} = 11 \text{ nm}, k = 10$ )                         | Proposed Work |

| 16                            | CG TFET (decreasing step) ( $L_{GAP}$ = 25 nm, $L_{GATE}$ = 40 nm, $H_{GAP}$ = 11 nm, $k$ = 10)                          |               |

| 17                            | CG TFET (concave step) ( $L_{GAP} = 25 \text{ nm}$ , $L_{GATE} = 40 \text{ nm}$ , $H_{GAP} = 11 \text{ nm}$ , $k = 10$ ) |               |

Table 1. Different reported works on biosensors numbered along the horizontal axis of Figure 7.

Figure 5. (a) Comparison of sensitivities of dielectric-modulated CG TFET and MOSFET biosensors at gate voltage 1.2 V, drain voltage 1 V and  $N_{bio} = -5 \times 10^{11}$  cm $^{\circ}$  for dielectric constant, k = 5, 7, 10 and 12; (b) comparison of sensitivities of dielectric-modulated CG TFET and MOSFET biosensors at gate voltage 1.2 V, drain voltage 1 V and  $N_{bio} = 5 \times 10^{11}$  cm $^{-2}$  for dielectric constant, k = 5, 7, 10 and 12.

Not only does a shorter channel length affect the electrical characteristics of a MOSFET, but also its principle of thermionic emission by which its operation contributes to such low sensitivity. On the contrary, TFETs which operate by band-to-band tunneling perform well even when scaled. This advantage of TFET is suitable to be exploited for its biosensing capabilities.

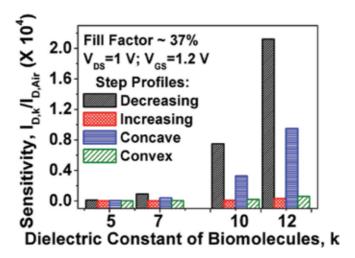

## 7.2. Partially filled Nanogap

The comparison of sensitivity for the four different profiles of partially filled nanogap shown in **Figure 1b–e** is shown in **Figure 6**. Only the decreasing and concave step profiles of biomolecule immobilization respond well to the change in dielectric constant. Contrary to this, the

**Figure 6.** Comparison of sensitivities of step profiles of partially filled nanogap in CG TFET biosensor for dielectric constant, k = 5, 7, 10 and 12.

increasing and convex step profiles demonstrate poor sensitivity. The reason for this is the proximity of the highest step with the source-channel tunnel junction. In case of decreasing and concave step profiles, the higher steps are present near to the tunnel junction as shown in **Figure 1b**, **d** respectively. As the value of k increases, the gate-channel coupling increases in the region of higher steps closer to the tunnel junction. So, the response of the biosensor is better than that of the increasing and convex step profiles where the higher steps are located away from the source-channel tunnel junction.

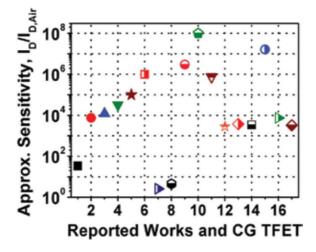

## 7.3. Status map of biosensors

There are a number of important simulated and modeled works reported on dielectric-modulated TFET and FET. This section presents a map of the sensitivities of such biosensors proposed till date along with sensitivity of the proposed CG TFET.

Although the status map of **Figure 7** mentions the maximum or best sensitivities of each work, yet the architectural specifications under which the biosensors have been reported vary from one to another, and hence, drawing comparisons among them through **Figure 7** is not justified. However, there are a few conclusions that can be derived from the status map. Dielectric-modulated TFETs are more sensitive to the presence of biomolecules than MOSFETs due to the difference in their current transport mechanisms. In MOSFETs, sensitivities reduce at lesser channel lengths. The CG TFET, with a channel length of 40 nm, shows significant sensitivity; a fully filled nanogap in CG TFET for k = 10 has sensitivity closer to that of DM PNPN TFET for k = 10 possessing a channel length of 250 nm and nanogap length of 75 nm. However, the partially filled nanogaps (decreasing and concave step profiles) have lesser sensitivities than the fully filled case as explained in Section 7.2.

**Figure 7.** Sensitivities of FET-based biosensors of reported works and those of CG TFET. The sensitivities are extracted from the published works, and due to the possible tolerances in extraction, the vertical axis is named as 'approximate sensitivity'. The various biosensors are referred by using serial numbers from 1 to 17, the details of which are listed in **Table 1**.

## 8. Conclusion

This chapter has presented an overview on Tunnel Field Effect Transistors (TFETs) as dielectric-modulated biosensors. Tunnel Field Effect Transistors have emerged as one of the most significant devices for low power applications due to their ability to withstand the effects of scaling. With the interests gathering around FET-based biosensors, research on TFETs as biosensors has recently brought new focus. This chapter has discussed the various aspects of dielectric-modulated TFET as biosensor with emphasis on the design and development through simulation analyses. Practical implications of the biosensors are presented. A Circular Gate TFET as a dielectric-modulated biosensor is presented and analyzed at lesser channel length. The CG TFET is observed to offer an impressive sensitivity as compared to other biosensors. The different challenges in implementing a TFET-based dielectric-modulated biosensor are varied, ranging from the problems of steric hindrance, fabrication issues and uncertainty of probe placement. Simulation and modeling may enable one to predict the various effects. Appropriate physics-based models are necessary to validate the results on TCAD tool.

## **Author details**

Rupam Goswami<sup>1\*</sup> and Brinda Bhowmick<sup>2</sup>

- \*Address all correspondence to: rupam.goswamifet@kiit.ac.in

- 1 Kalinga Institute of Industrial Technology, Bhubaneswar, India

- 2 National Institute of Technology Silchar, Silchar, India

## References

- [1] Sarangi S, Bhushan S, Santra A, Dubey S, Jit S, Tiwari PK. A rigorous simulation based study of gate misalignment effects in gate engineered double-gate (DG) MOSFETs. Superlattices and Microstructures. 2013;60:263-279. DOI: 10.1016/j.spmi.2013.05.009

- [2] Choi WY, Park B-G, Lee JD, Liu T-JK. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Letters. 2007;28(8):743-745. DOI: 10.1109/led.2007.901273

- [3] Royer CL, Mayer F. Exhaustive experimental study of tunnel field effect transistors (TFETs): From materials to architecture. In: 10th International Conference on Ultimate Integration of Silicon; March 18-20, 2009. Aachen: IEEE; 2009. pp. 53-56. DOI: 10.1109/ ulis.2009.4897537

- [4] International Technology Roadmap for Semiconductors. http://public.itrs.net/. 2015 Edition. [Accessed: January 06, 2018]

- [5] Yang F-L et al. 5nm-gate nanowire fin FET. In: Digest of Technical Papers Symposium. VLSIT; June 15-17, 2004. Honolulu: IEEE; 2004. pp. 196-197. DOI:10.1109/VLSIT.2004. 1345476

- [6] Elmessary MA, Nagy D, Aldegunde M, Seoane N, Indalecio G, Lindberg J, et al. Scaling/LER study of Si GAA nanowire FET using 3D finite element Monte Carlo simulations. Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), January 25-27, 2016. Vienna: IEEE; 2016. pp. 52-55. DOI: 10.1109/ulis.2016.7440050

- [7] Yoon J-S, Kim K, Rim T, Baek C-K. Performance and variations induced by single interface trap of nanowire FETs at 7-nm node. IEEE Transactions on Electron Devices. 2017;64(2): 339-345. DOI: 10.1109/ted.2016.2633970

- [8] Wong HSP. Beyond the conventional transistor. IBM Journal of Research and Development. 2002;46(2.3):133-168. DOI: 10.1147/rd.462.0133

- [9] Guo J, Datta S, Lundstrom M. A numerical study of scaling issues for Schottky-barrier carbon nanotube transistors. IEEE Transactions on Electron Devices. 2004;51(2):172-177. DOI: 10.1109/ted.2003.821883

- [10] Yousefi R, Shabani M. A model for carbon nanotube FETs in the ballistic limit. Microelectronics Journal. 2011;42(11):1299-1304. DOI: 10.1016/j.mejo.2011.08.012

- [11] Fiori G, Iannaccone G. Simulation of graphene nanoribbon field-effect transistors. IEEE Electron Device Letters. 2007;28(8):760-762. DOI: 10.1109/led.2007.901680

- [12] Echtermeyer T, Lemme M, Baus M, Szafranek B, Geim A, Kurz H. Nonvolatile switching in graphene field-effect devices. IEEE Electron Device Letters. 2008;29(8):952-954. DOI: 10.1109/led.2008.2001179

- [13] Tamersit K, Djeffal F. Double-gate graphene Nanoribbon field-effect transistor for DNA and gas sensing applications: Simulation study and sensitivity analysis. IEEE Sensors Journal. 2016;**16**(11):4180-4191. DOI: 10.1109/jsen.2016.2550492

- [14] Nirschl T, Wang P-F, Hansch W, Schmitt-Landsiedel D. The tunnelling field effect transistors (TFET): The temperature dependence, the simulation model, and its application. In: IEEE International Symposium on Circuits and Systems; May 23-26, 2004. Vancouver: IEEE, p. III-713-16. DOI: 10.1109/ISCAS.2004.1328846

- [15] Jiang C, Liang R, Xu J. Investigation of negative capacitance gate-all-around tunnel FETs combining numerical simulation and analytical modeling. IEEE Transactions on Nanotechnology. 2016;16(1):58-67. DOI: 10.1109/tnano.2016.2627808

- [16] Omura Y, Mallik A, Matsuo N. The impact of a fringing field on the device performance of a P-channel tunnel field-effect transistor with a high-κ gate dielectric. In: MOS Devices for Low-Voltage and Low-Energy Applications. Singapore: Wiley; 2016. pp. 399-411. DOI: 10.1002/9781119107361.ch34

- [17] Shen M, Saikin S, Cheng M-C. Spin injection in spin FETs using a step-doping profile. IEEE Transactions On Nanotechnology. 2005;4(1):40-44. DOI: 10.1109/tnano.2004.840150

- [18] Datta S, Das B. Electronic analog of the electro-optic modulator. Applied Physics Letters. 1998;**56**(7):665-667. DOI: 10.1063/1.102730

- [19] Sugahara S, Tanaka M. A spin metal-oxide-semiconductor field-effect transistor (spin MOSFET) with a ferromagnetic semiconductor for the channel. Journal of Applied Physics. 2005;97(10):10D503. DOI: 10.1063/1.1852280

- [20] Salahuddin S. Review of negative capacitance transistors. In: International Symposium on VLSI Technology, Systems and Application (VLSI-TSA); April 25-27, 2016. Hsinchu: IEEE. pp. 1-1. DOI: 10.1109/vlsi-tsa.2016.7480491

- [21] Jo J, Shin C. Impact of temperature on negative capacitance field-effect transistor. Electronics Letters. 2015;51(1):106-108. DOI: 10.1049/el.2014.3515

- [22] Boucart K, Ionescu A. Double gate tunnel FET with ultrathin silicon body and high-k gate dielectric. In: Proceedings of the European Solid-State Device Research Conference, September 19-21, 2006. Montreux: IEEE; 2007. pp. 1725-1733. DOI: 10.1109/essder.2006. 307718

- [23] Boucart K, Ionescu AM. Length scaling of the double gate tunnel FET with a high-K gate dielectric. Solid-State Electronics. 2007;51(11-12):1500-1507. DOI: 10.1016/j. sse.2007.09.014

- [24] Lam K-T, Seah D, Chin S-K, Kumar SB, Samudra G, Yeo Y-C, et al. A simulation study of graphene-nanoribbon tunneling FET with heterojunction channel. IEEE Electron Device Letters. 2010;31(6):555-557. DOI: 10.1109/led.2010.2045339

- [25] Vishnoi R, Kumar MJ. Compact analytical drain current model of gate-all-around nanowire tunneling FET. IEEE Transactions on Electron Devices. 2014;61(7):2599-2603. DOI: 10.1109/ted.2014.2322762

- [26] Toh E-H, Wang GH, Chan L, Sylvester D, Heng C-H, Samudra GS, et al. Device design and scalability of a double-gate tunneling field-effect transistor with silicon-germanium source. Japanese Journal of Applied Physics. 2008;47(4):2593-2597. DOI: 10.1143/ jjap.47.2593

- [27] Ahish S, Sharma D, Kumar YBN, Vasantha MH. Performance enhancement of novel InAs/Si hetero double-gate tunnel FET using Gaussian doping. IEEE Transactions on Electron Devices. 2016;63(1):288-295. DOI: 10.1109/ted.2015.2503141

- [28] Dewey G, Chu-Kung B, Boardman J, Fastenau JM, Kavalieros J, Kotlyar R, et al. Fabrication, characterization, and physics of III-V heterojunction tunneling field effect transistors (H-TFET) for steep sub-threshold swing. In: International Electron Devices Meeting, December 5-7, 2011. Washington, DC: IEEE; 2012. pp. 33.6.1-33.6.4. DOI: 10.1109/ iedm.2011.6131666

- [29] Bagga N, Dasgupta S. Surface potential and drain current analytical model of gate all around triple metal TFET. IEEE Transactions on Electron Devices. 2017;64(2):606-613. DOI: 10.1109/ted.2016.2642165

- [30] Bagga N, Sarkar SK. An analytical model for tunnel barrier modulation in triple metal double gate TFET. IEEE Transactions on Electron Devices. 2015;62(7):2136-2142. DOI: 10.1109/ted.2015.2434276

- [31] Dash S, Mishra G. A new analytical threshold voltage model of cylindrical gate tunnel FET (CG-TFET). Superlattices and Microstructures. 2015;86:211-220. DOI: 10.1016/j. spmi.2015.07.049

- [32] Lee MJ, Choi WY. Analytical model of single-gate silicon-on-insulator (SOI) tunneling field-effect transistors (TFETs). Solid-State Electronics. 2011;63(1):110-114. DOI: 10.1016/j. sse.2011.05.008

- [33] Luong G, Strangio S, Tiedemannn A, Lenk S, Trellenkamp S, Bourdelle K, et al. Experimental demonstration of strained Si nanowire GAA n-TFETs and inverter operation with complementary TFET logic at low supply voltages. Solid-State Electronics. 2016;115:152-159. DOI: 10.1016/j.sse.2015.08.020

- [34] Mookerjea S, Mohata D, Krishnan R, Singh J, Vallett A, Ali A, et al. Experimental demonstration of 100nm channel length In0.53Ga0.47As-based vertical inter-band tunnel field effect transistors (TFETs) for ultra low-power logic and SRAM applications. In: IEEE International Electron Devices Meeting (IEDM), December 7-9, 2009. Baltimore: IEEE; 2010. pp. 1-3. DOI: 10.1109/iedm.2009.5424355

- [35] Singh J, Ramakrishnan K, Mookerjea S, Datta S, Vijaykrishnan N, Pradhan D. A novel Si-tunnel FET based SRAM design for ultra low-power 0.3V VDD applications. In: 15th Asia and South Pacific Design Automation Conference (ASP-DAC), January 18-21, 2010. Taipei: IEEE; 2010. pp. 181-186. DOI: 10.1109/aspdac.2010.5419897

- [36] Im H, Huang X-J, Gu B, Choi Y-K. A dielectric-modulated field-effect transistor for biosensing. Nature Nanotechnology. 2007;2(7):430-434. DOI: 10.1038/nnano.2007.180

- [37] Narang R, Saxena M, Gupta RS, Gupta M. Dielectric modulated tunnel field-effect transistor—A biomolecule sensor. IEEE Electron Device Letters. 2012;33(2):266-268. DOI: 10.1109/led.2011.2174024

- [38] Narang R, Reddy KVS, Saxena M, Gupta RS, Gupta M. A dielectric-modulated tunnel-FET-based biosensor for label-free detection: Analytical modeling study and sensitivity analysis. IEEE Transactions on Electron Devices. 2012;59(10):2809-2817. DOI: 10.1109/TED.2012.2208115

- [39] Narang R, Saxena M, Gupta RS, Gupta M. Comparative analysis of dielectric-modulated FET. IEEE Transactions on Nanotechnology. 2015;14(3):427-435. DOI: 10.1109/TNANO.2015.2396899

- [40] Kanungo S, Chattopadhyay S, Gupta PS, Rahaman H. Comparative performance analysis of the dielectrically modulated full-gate and short-gate tunnel FET-based biosensors. IEEE Transactions on Electron Devices. 2015;62(3):994-1001. DOI: 10.1109/ ted.2015.2390774

- [41] Kanungo S, Chattopadhyay S, Gupta PS, Sinha K, Rahaman H. Study and analysis of the effects of SiGe source and pocket-doped channel on sensing performance of dielectrically modulated tunnel FET-based biosensors. IEEE Transactions on Electron Devices. 2016;63(6):2589-2596. DOI: 10.1109/ted.2016.2556081

- [42] Sarkar D, Banerjee K. Proposal for tunnel-field-effect-transistor as ultra-sensitive and label-free biosensors. Applied Physics Letters. 2012;**100**(14):143108. DOI: 10.1063/1.36 98093

- [43] Bergveld P. Thirty years of ISFETOLOGY. Sensors and Actuators B: Chemical. 2003;88(1): 1-20. DOI: 10.1016/s0925-4005(02)00301-5

- [44] Kim C-H, Ahn J-H, Lee K-B, Jung C, Park HG, Choi Y-K. A new sensing metric to reduce data fluctuations in a nanogap-embedded field-effect transistor biosensor. IEEE Transactions on Electron Devices. 2012;59(10):2825-2831. DOI: 10.1109/ted.2012.2209650

- [45] Abdi DB, Kumar MJ. Dielectric modulated overlapping gate-on-drain tunnel-FET as a label-free biosensor. Superlattices and Microstructures. 2015;86:198-202. DOI: 10.1016/j. spmi.2015.07.052

- [46] Ahangari Z. Performance assessment of dual material gate dielectric modulated nanowire junctionless MOSFET for ultrasensitive detection of biomolecules. RSC Advances. 2016;6(92):89185-89191. DOI: 10.1039/c6ra17361f

- [47] Knoch J, Appenzeller J. A novel concept for field-effect transistors The tunneling carbon nanotube FET. In: 63rd Device Research Conference Digest, DRC 05; June 20-22, 2005. Santa Barbara: IEEE; 2005. pp. 153-156. DOI: 10.1109/drc.2005.1553099

- [48] Knoch J, Mantl S, Appenzeller J. Impact of the dimensionality on the performance of tunneling FETs: Bulk versus one-dimensional devices. Solid-State Electronics. 2007;**51**(4):572-578. DOI: 10.1016/j.sse.2007.02.001

- [49] Wang C, Wu C, Wang J, Huang Q, Huang R. Analytical current model of tunneling field-effect transistor considering the impacts of both gate and drain voltages on tunneling. Science China Information Sciences. 2014;58(2):1-8. DOI: 10.1007/s11432-014-5196-3

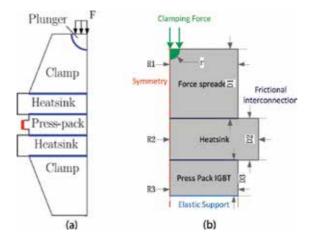

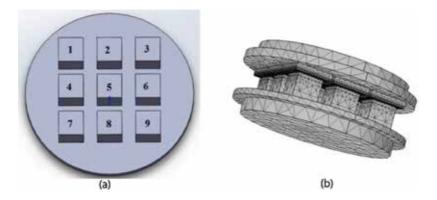

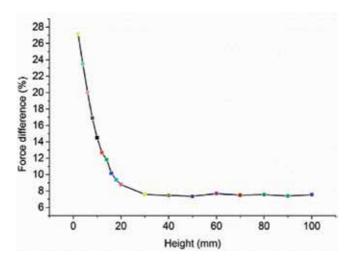

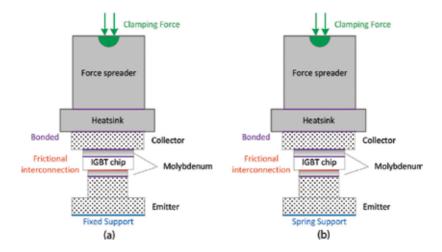

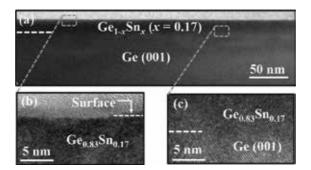

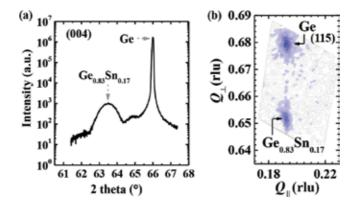

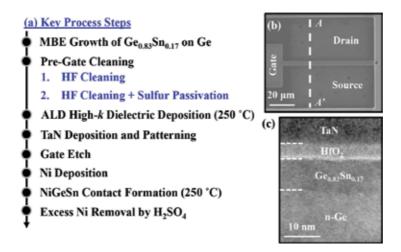

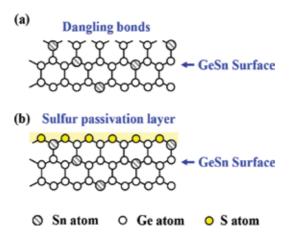

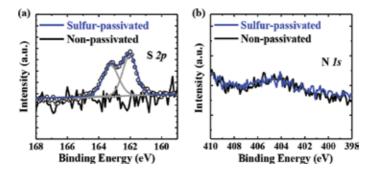

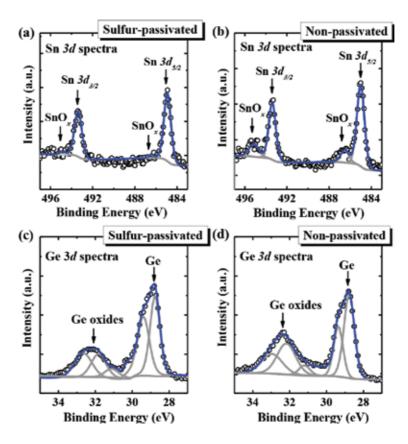

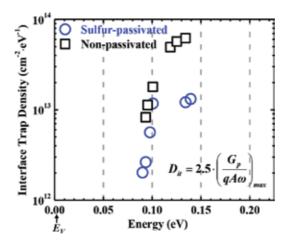

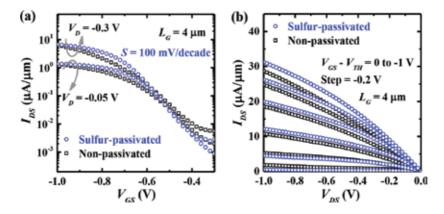

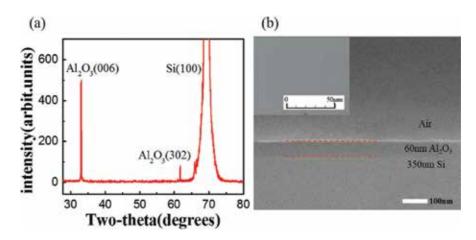

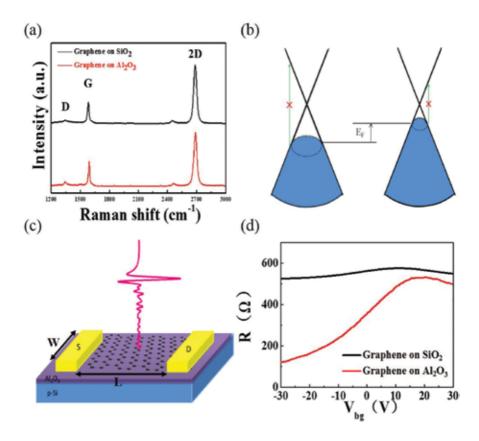

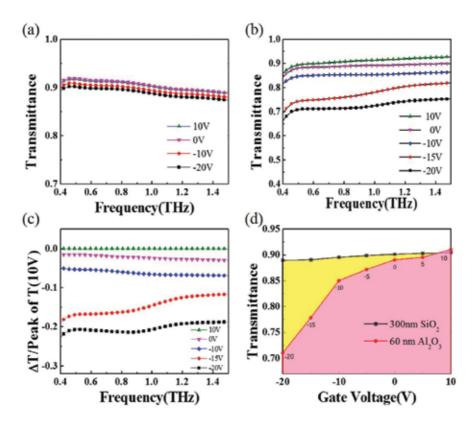

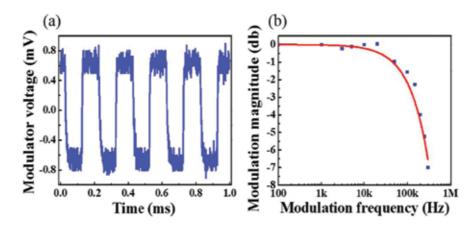

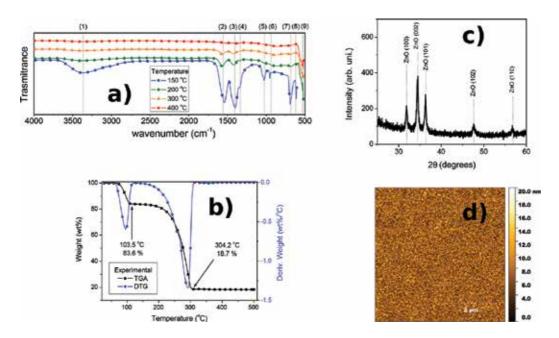

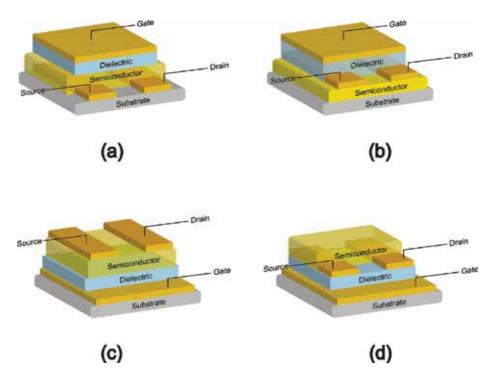

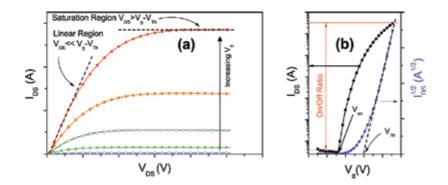

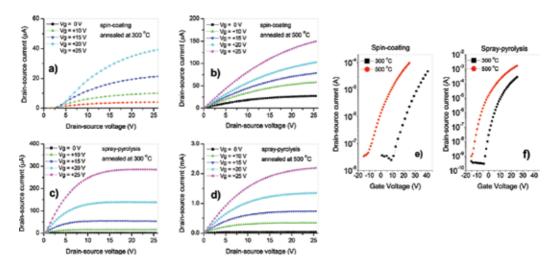

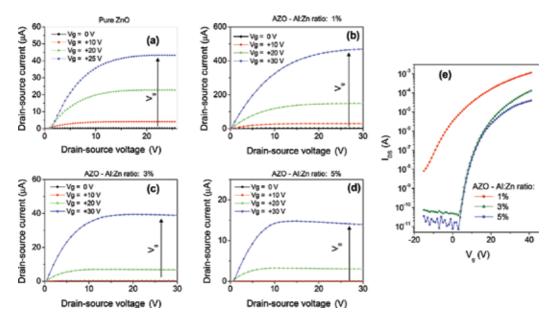

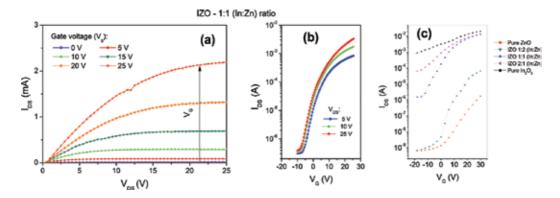

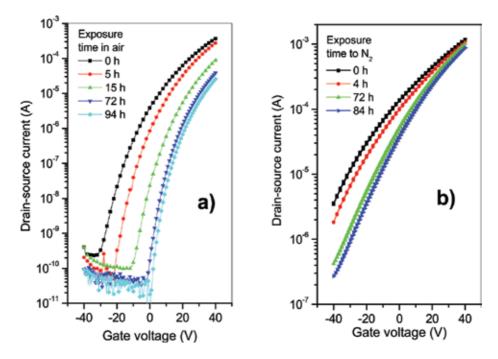

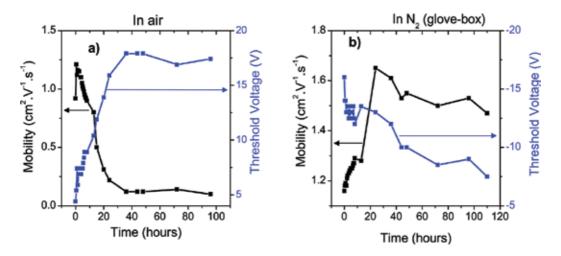

- [50] Synopsys. Sentaurus Device User Guide. Mountain View: Synopsys, Inc.; 2011