IntechOpen

# Memristor and Memristive Neural Networks

Edited by Alex Pappachen James

# MEMRISTOR AND MEMRISTIVE NEURAL NETWORKS

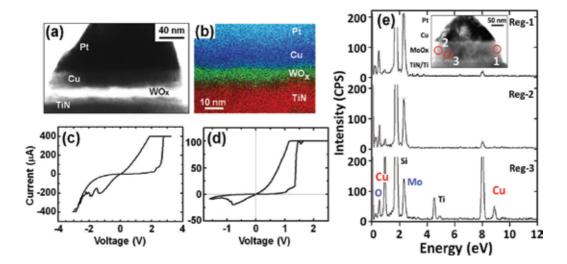

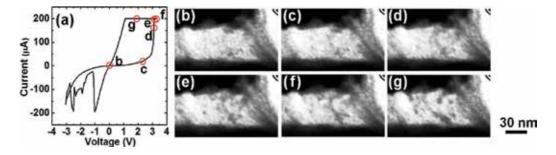

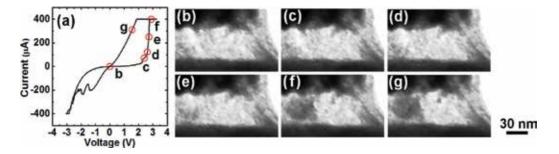

Edited by Alex Pappachen James

#### **Memristor and Memristive Neural Networks**

http://dx.doi.org/10.5772/66539 Edited by Alex Pappachen James

#### Contributors

Xinjiang Zhang, Runmiao Li, Huang Anping, Yu Chi, Yao-Feng Chang, Cheng Chih Hsieh, Ying-Chen Chen, Chih-Yang Lin, Meiqi Guo, Fei Zhou, Burt W. Fowler, Ting-Chang Chang, Jack C. Lee, Jason Eshraghian, Kamran Eshraghian, Herbert Ho-Ching Iu, Carlos Sanchez-Lopez, Illiani Carro-Pérez, Victor H. Carbajal-Gomez, Miguel Angel Carrasco-Aguilar, Francisco Epimenio Morales-López, Atsushi Tsurumaki-Fukuchi, Masashi Arita, Yasuo Takahashi, Luis-Miguel Procel-Moya, Henrique Gomes, Stefan Meskers, Dago De Leeuw, Alex Pappachen James, Timur Ibrayev, Olga Krestinskaya, Irina Dolzhikova, Dietmar Fey, Lukas Riedersberger, Marc Reichenbach, Yao Shuai, Geetika Khurana, Nitu Kumar, James Scott, Ram S. Katiyar, Aigerim Tankimanova, Fatih Gul, Yunus Babacan, Abdullah Yesil, Yasin Oğuz

#### © The Editor(s) and the Author(s) 2018

The moral rights of the and the author(s) have been asserted.

All rights to the book as a whole are reserved by INTECH. The book as a whole (compilation) cannot be reproduced, distributed or used for commercial or non-commercial purposes without INTECH's written permission. Enquiries concerning the use of the book should be directed to INTECH rights and permissions department (permissions@intechopen.com).

Violations are liable to prosecution under the governing Copyright Law.

#### (cc) BY

Individual chapters of this publication are distributed under the terms of the Creative Commons Attribution 3.0 Unported License which permits commercial use, distribution and reproduction of the individual chapters, provided the original author(s) and source publication are appropriately acknowledged. If so indicated, certain images may not be included under the Creative Commons license. In such cases users will need to obtain permission from the license holder to reproduce the material. More details and guidelines concerning content reuse and adaptation can be foundat http://www.intechopen.com/copyright-policy.html.

#### Notice

Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published chapters. The publisher assumes no responsibility for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained in the book.

First published in Croatia, 2018 by INTECH d.o.o. eBook (PDF) Published by IN TECH d.o.o. Place and year of publication of eBook (PDF): Rijeka, 2019. IntechOpen is the global imprint of IN TECH d.o.o. Printed in Croatia

Legal deposit, Croatia: National and University Library in Zagreb

Additional hard and PDF copies can be obtained from orders@intechopen.com

Memristor and Memristive Neural Networks Edited by Alex Pappachen James p. cm. Print ISBN 978-953-51-3947-8 Online ISBN 978-953-51-3948-5 eBook (PDF) ISBN 978-953-51-4009-2

# We are IntechOpen, the first native scientific publisher of Open Access books

3.350+ Open access books available

International authors and editors

108,000+ 115M+ Downloads

15Countries delivered to Our authors are among the

Top 1% most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science<sup>™</sup> Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# Meet the editor

Alex Pappachen James received his PhD degree from the Queensland Micro- and Nanotechnology Centre, Griffith University, Brisbane, QLD, Australia. He is internationally known for his contributions on memristive networks, neuromorphic computing and image processing. Currently, he is chairing the Electrical Engineering Department at Nazarbayev University. He is a mentor to

several tech start-ups and co-founded companies in machine learning and computer vision hardware. He has been a founding chair for IEEE R10 Circuits and Systems Society Chapter and an executive board member of IET Vision and Imaging Network. He is the founding chair of IEEE Kazakhstan subsection, R8, and mentor to IEEE NU Student Branch. He was an editorial member of Information Fusion (2010–2015), Elsevier, and is an associate editor for HCIS (2015–present), Springer; IEEE Access (2017–present); IEEE Transactions on Emerging Topics in Computational Intelligence (2017–present); and IEEE Transactions on Circuits and Systems 1 (2018–present). He was a faculty senate chair of NU between 2016 and 2017. He received an award from the president of Kazakhstan for his services in the field of education in Kazakhstan in 2017. He is a senior member of IEEE, life member of ACM and senior fellow of HEA.

# Contents

#### Preface XI

| Section 1 | Memristor Devices 1                                                                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 | Physical Models for Resistive Switching Devices 3<br>Luis-Miguel Procel-Moya                                                                                                       |

| Chapter 2 | <b>Graphene Oxide-Based Memristor 19</b><br>Geetika Khurana, Nitu Kumar, James F. Scott and Ram S. Katiyar                                                                         |

| Chapter 3 | <b>Emulator Circuits and Resistive Switching Parameters of Memristor 41</b><br>Abdullah Yesil, Fatih Gül and Yunus Babacan                                                         |

| Chapter 4 | Nanoscale Switching and Degradation of Resistive Random<br>Access Memory Studied by In Situ Electron Microscopy 63<br>Masashi Arita, Atsushi Tsurumaki-Fukuchi and Yasuo Takahashi |

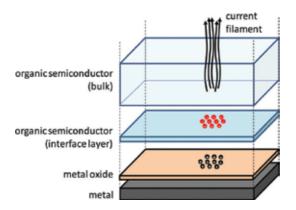

| Chapter 5 | Resistive Switching in Metal Oxide/Organic Semiconductor<br>Nonvolatile Memories 93<br>Henrique L. Gomes, Dago M. de Leeuw and Stefan C.J. Meskers                                 |

| Section 2 | Memristor Modelling 113                                                                                                                                                            |

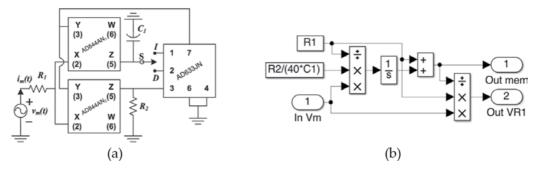

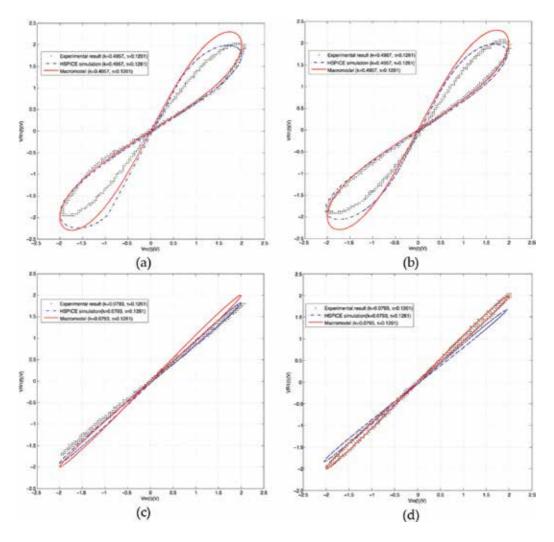

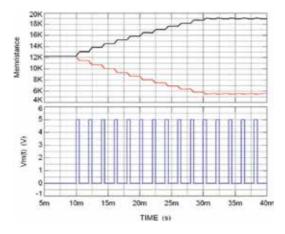

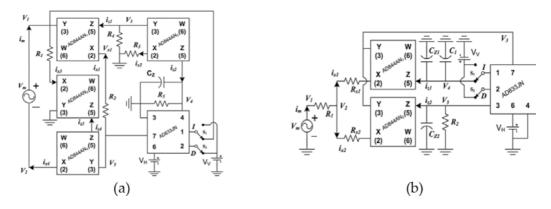

| Chapter 6 | Memristor Emulator Circuit Design and Applications 115                                                                                                                             |

- Carlos Sánchez-López, Illiani Carro-Pérez, Victor Hugo Carbajal-Gómez, Miguel Angel Carrasco-Aguilar and Francisco Epimenio Morales-López

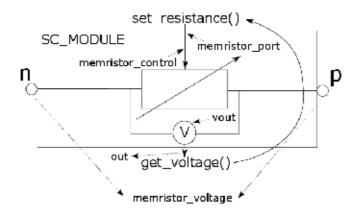

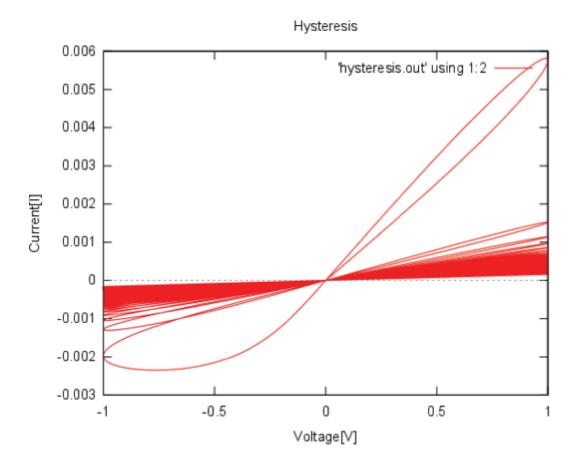

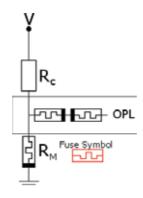

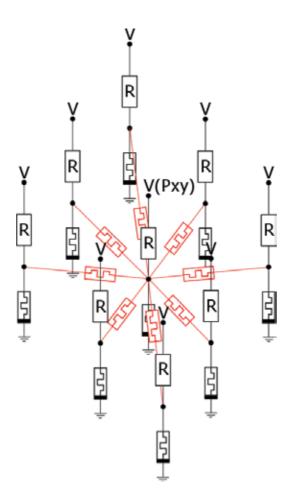

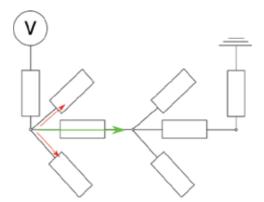

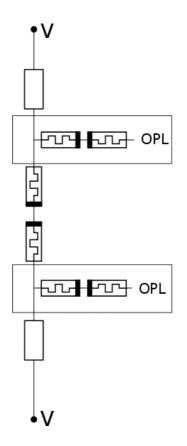

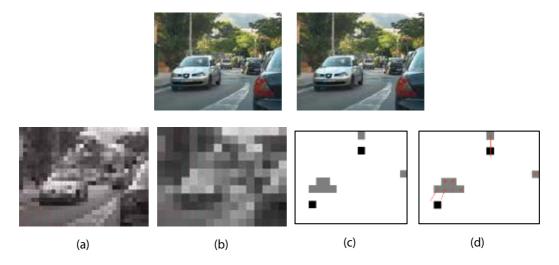

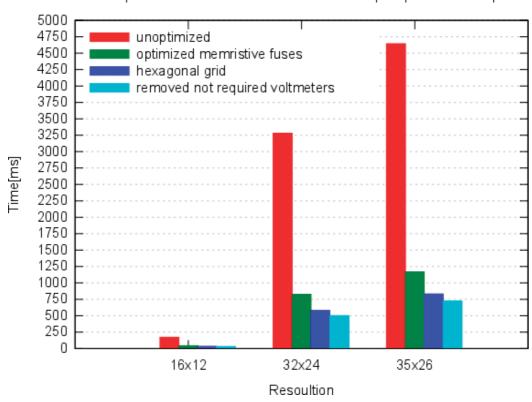

- Chapter 7 Simulating Memristive Networks in SystemC-AMS 147 Dietmar Fey, Lukas Riedersberger and Marc Reichenbach

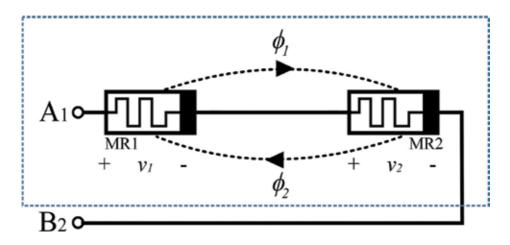

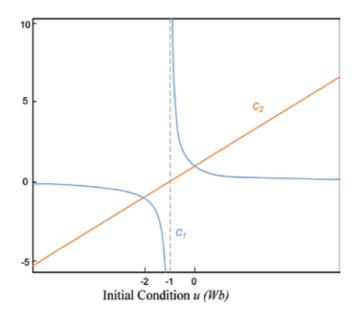

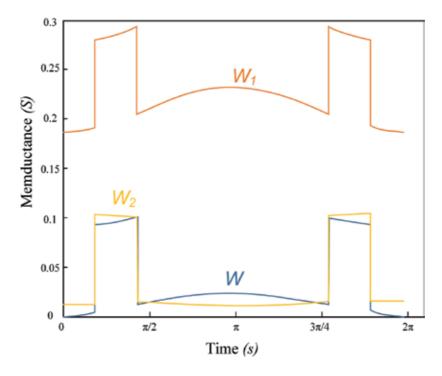

| Chapter 8  | <b>Modeling of Coupled Memristive-Based Architectures</b><br><b>Applicable to Neural Network Models 167</b><br>Jason Kamran Jr Eshraghian, Herbert H.C. Iu and Kamran<br>Eshraghian                                                                                                                                               |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 9  | Mathematical Modeling of Memristors 187<br>Yasin Oğuz                                                                                                                                                                                                                                                                             |

| Section 3  | Memristor Neuromorphic Applications 207                                                                                                                                                                                                                                                                                           |

| Chapter 10 | Introduction to Memristive HTM Circuits 209<br>Alex James, Timur Ibrayev, Olga Krestinskaya and Irina Dolzhikova                                                                                                                                                                                                                  |

| Chapter 11 | Review of Recently Progress on Neural Electronics and<br>Memcomputing Applications in Intrinsic SiOx-Based Resistive<br>Switching Memory 227<br>Cheng-Chih Hsieh, Yao-Feng Chang, Ying-Chen Chen, Xiaohan Wu,<br>Meiqi Guo, Fei Zhou, Sungjun Kim, Burt Fowler, Chih-Yang Lin,<br>Chih-Hung Pan, Ting-Chang Chang and Jack C. Lee |

| Chapter 12 | <b>Memristor Neural Network Design 249</b><br>Anping Huang, Xinjiang Zhang, Runmiao Li and Yu Chi                                                                                                                                                                                                                                 |

| Chapter 13 | <b>Spike-Timing-Dependent Plasticity in Memristors 283</b><br>Yao Shuai, Xinqiang Pan and Xiangyu Sun                                                                                                                                                                                                                             |

Chapter 14 Neural Network-Based Analog-to-Digital Converters 297 Aigerim Tankimanova and Alex Pappachen James

# Preface

The growth in internet of things, devices and systems has resulted in the need to develop energy-efficient near-sensor processing devices and circuits. This requires the development of alternative computing implementations such as neuromorphic computing, quantum computing and approximate computing. Memristor devices and their natural properties to change states can be used to mimic neural circuits and neural networks. It is estimated that these networks can be scaled in the future to create large-scale neurocomputing solution.

This book covers a range of models, circuits and systems built with memristor devices and networks in applications to neural networks. It is divided into three parts: (1) Devices, (2) Models and (3) Applications. The resistive switching property is an important aspect of the memristors, and there are several designs of this discussed in this book, such as in metal oxide/organic semiconductor nonvolatile memories, nanoscale switching and degradation of resistive random access memory and graphene oxide-based memristor. The modelling of the memristors is required to ensure that the devices can be put to use and improve emerging application. In this book, various memristor models are discussed, from a mathematical framework to implementations in SPICE and verilog, that will be useful for the practitioners and researchers to get a grounding on the topic. The applications of the memristor models in various neuromorphic networks are discussed covering various neural network models, implementations in A/D converter and hierarchical temporal memories.

This book is a response to the growing field of memristor networks and applications, providing insights into a collection of topics in memristor devices, circuits and systems. It is suitable for the introductory studies and equally useful for the researchers to discuss the emerging topics in the memristor networks.

> Alex Pappachen James Nazarbayev University Kazakhstan

Section 1

**Memristor Devices**

# **Physical Models for Resistive Switching Devices**

## Luis-Miguel Procel-Moya

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.69025

#### Abstract

We present a classification and description of the principal resistive switching and transport mechanisms in chalcogonides materials. We classify the model according to how many material dimensions are involved in the resistive switching mechanism. In this way, we describe the phase change model (3D), the interface modulation model (2D) and models where the switching mechanism depends on the formation of a conduction filament (1D). Among the conduction filament models, we include the thermochemical oxygen diffusion mechanism, the oxidation/reduction mechanism and the quantum point effect.

Keywords: chalcogonides, resistive switching, physical models

## 1. Introduction

Typically, a resistive switching material changes its resistance between two states: High Resistive State (HRS or OFF-state) and Low Resistive State (LRS or ON-state). The most common structure for a resistive switching devices is an insulator between two metals or metal/insulator/metal (MIM) structure. One of the most important applications of these kind of devices is for non-volatile memories or Resistive RAMs (ReRAMs).

The metal elements of the MIM structure are called top and bottom electrodes. An electrical stimulus is necessary to apply between these electrodes to change the resistive state of the insulator material. In order to determine the resistive state (HRS or LRS), a low voltage is applied on the electrodes, and the current, which flows through the insulator, is measured ( $I_{\text{HRS}}$  or  $I_{\text{LRS}}$ ). There are several orders of magnitudes of difference between  $I_{\text{HRS}}$  and  $I_{\text{LRS}}$  currents. The change from the HRS to the LRS is called SET process and the change from the LRS to the HRS is called RESET process.

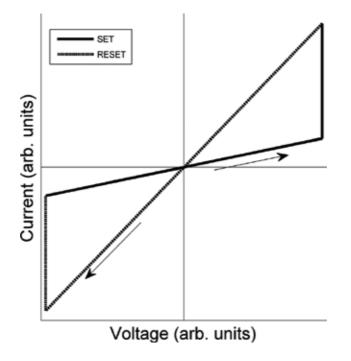

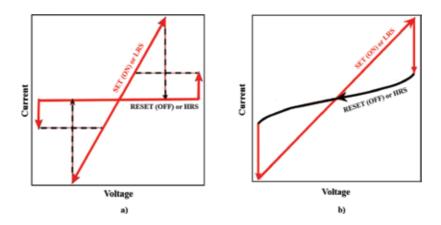

Depending on the voltage polarity applied on the electrodes, there are two schemes to change the resistive state: unipolar and bipolar. On the one hand, in the unipolar scheme, the resistive state change does not depend on the voltage polarity and there are two threshold voltages: one

for the RESET process ( $V_{\text{RESET}}$ ) and one for the SET process ( $V_{\text{SET}}$ ) with the same polarity as we can see in **Figure 1**. On the other hand, in the bipolar scheme,  $V_{\text{RESET}}$  and  $V_{\text{SET}}$  have different polarities (**Figure 2**).

There is no universal theory or model which explains the electron conduction in the two resistive states and the SET and RESET processes because there are many factors that affect the switching behaviour, such as the type of the insulator material, fabrication process, nature of the dielectric breakdown, among others. However, Waser and Wutting proposed a classification based on the type of the resistive switching mechanisms, such as nanochemical materials, ferroelectric tunnelling, electrostatics effects, phase change mechanism, thermochemical mechanism, redox-based effect, electrochemical effect, molecular switching effect and magnetoresistive effect [1].

Chalcogonides are one of the most used materials in the fabrication of resistive memory devices. The switching mechanisms related to these materials are: phase change memory effect, thermochemical memory effect, redox-based memory effect and interface defect modulation. The phase change mechanism affects the complete volume of the insulator material and it is considered as a 3D mechanism. A 2D resistive switching mechanism is the modulation of the defect density at the metal/insulator interface. Finally, when the resistivity material depends on the formation of a conduction filament (CF), 1D mechanisms are involved in the resistive switching process. Thermochemical diffusion of oxygen, reduction/oxidation of the CF and quantum point contact effects are typical 1D mechanisms.

Figure 1. SET and RESET process for unipolar behaviour.

Figure 2. SET and RESET process for bipolar behaviour.

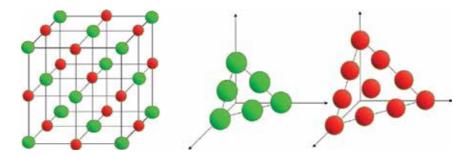

### 2. Phase change model

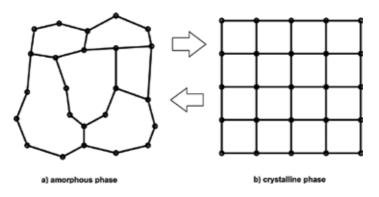

Heavier chalcogonides, such as tellurides and selenides, show different electrical and optical properties in their amorphous and crystalline phases (**Figure 3**). The resistive switching of these materials is unipolar. On the one hand, the amorphous phase of these materials has high resistivity and low reflectivity and, on the other hand, crystalline phase has low resistivity and high reflectivity [2]. These properties are being exploited in the development of optical storage

Figure 3. Phase change mechanism: the phase material changes from (a) amorphous phase to (b) crystalline phase (and vice versa) to have different resistivity and reflectivity.

products, such as compact disks (CD), digital versatile disks (DVD), high-definition digital versatile disks (HD-DVD) and Blu-ray disks (BR). The first kind of materials used for optical storage were good glasses, such as Te-based alloys like Te<sub>85</sub>Ge<sub>13</sub> doped with Sb, S and P. These materials show good electrical switching properties in the amorphous and crystalline phases but the crystallization time was in the order of microseconds, too high to be considered for optical storage. The second generation of these materials shows shorter crystallization time and good optical properties. Among these materials, we have GeTe, Ge<sub>11</sub>Te<sub>80</sub>Sn<sub>4</sub>Au<sub>23</sub>, GeTe-Sb<sub>2</sub>Te<sub>3</sub>, GeBiTe and GeInSbTe. After, a third family of materials was later discovered which includes alloys of Sb<sub>2</sub>Te doped with Ag, In and Ge [2].

There are two important temperature thresholds in these materials: the melting temperature  $(T_m)$  and the glass-transition temperature  $(T_g)$  with  $T_m > T_g$ . The process to change the material phase from crystalline to amorphous and vice versa is as follows [2]:

- To write a bit, a short high-pulse laser or current is applied on the crystalline material to reach *T<sub>m</sub>* temperature.

- The material is cooling down rapidly with a rate higher than 10<sup>9</sup> K/s. In a very short time, the material reaches the amorphous phase without passing through the crystalline one.

- To erase the bit, a long short-pulse laser or current is applied on the amorphous material. The material temperature increases over  $T_{g}$ . There is an increment of the electron mobility and the material changes to the crystalline phase.

For electrical storage devices, the resistive switching property is fundamental and all these materials have it. However, not all these materials have the reflectivity switching property. To have this property, a very short time (few tens of nanoseconds) is needed for cooling down the material from the liquid phase to amorphous phase (step 2) [2].

When a low voltage is applied to the material in the amorphous phase, a very low current is measured due to the high resistance. When the voltage reaches a value around 0.7 V, the resistivity decreases and the material reach the so-called ON-amorphous phase [1, 2]. In these phases, the current increases significantly and enables enough heat to recrystallize the material. During the phase change, material defects play an important role. In the amorphous phase, the current is controlled by the Pool-Frenkel conduction, where carriers are trapped in defect sites according to the following equation (electron hopping mechanism) [1]:

$$I = 2qAN_T \frac{\Delta z}{\tau_0} e^{-(E_C - E_F)/kT} \sinh\left(\frac{qV\Delta z}{2kTt_h}\right)$$

(1)

where *A* is the contact area, *V* the applied voltage,  $N_T$  the integral of the trap distribution,  $\Delta z$  the intertrap distance,  $\tau_0$  the scape time for a trapping electron,  $E_F$  the Fermi energy,  $E_C$  the conduction band energy, *q* the elementary electron charge and  $t_h$  the thickness of the material. Because of the total conduction is presented in the complete material volume, this mechanism is called 3D. Experimental results show that the defect density in the material is very high and most of the defects are negative U-centres [1]. On the other hand, computational simulations show that in the crystalline phase, vacancy defects predominate with a concentration of 25% [1].

### 3. Metal/insulator interface modulation model

In this model, the resistive switching is presented at the metal/insulator interface. In other words, there is a contact resistance switching behaviour. This interface depending mechanism is presented in Peroskite oxides in which the material resistivity strongly depends on the interface area and the switching mechanism is always bipolar. A typical material that shows this behaviour is the Nb-doped  $SrTiO_3$  [3].

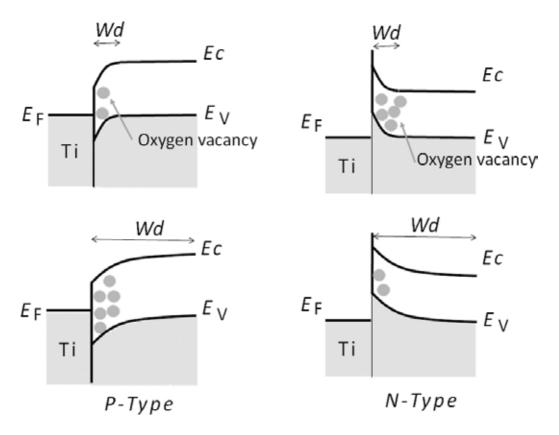

The origin of this resistivity change can be understood by examining the metal/insulator interface band diagram as shown in **Figure 4**. The insulator oxide is usually doped with different metals. Depending of doped metal and its density, the insulator behaves as semiconductor at the interface. This provokes a Schottky barrier contact instead of a pure ohmic contact [3].

An electric field applied on the metal electrodes can electrochemically modify the oxygen vacancy density at the interface. For an n-type semiconductor, an increment of the oxygen vacancies density reduces the depletion layer,  $W_{d}$ , in the energy band diagram provoking an increment of the tunnel electron conduction and, therefore, a decrement of the contact

**Figure 4.** Band diagrams at the Metal/Insulator interfaces. For a p-type semiconductor, the presence of oxygen vacancies increases  $W_d$ . For an n-type semiconductor, the presence of oxygen vacancies decreases  $W_d$ .

resistance (LRS). If an electric field is applied on the opposite direction, the number of oxygen vacancies in the n-type semiconductor decreases and provokes an increment of  $W_d$  and, therefore, the contact resistance increases (HRS). On the other hand, for a p-type semiconductor, the increment of oxygen vacancies increases  $W_d$  and the contact resistance (HRS), and a diminution of the oxygen vacancies decreases  $W_d$  and the contact resistance (LRS). In this model, the metal work function plays a very important role because the band bending strongly depends on this parameter.

Sawa showed very good resistive switching results for  $Ti/Pr_{07}Ca_{0.3}MnO_3/SrRuO_3$  (Ti/PCMO/SRO) cells, where SRO has metal properties and PCMO acts as p-type semiconductor. As well, the SRO/SrTi<sub>0.99</sub>Nb<sub>0.01</sub>O<sub>3</sub>/Ag (SRO/Nb:STO/Ag) cell showed a good resistive switching behaviour where Nb:STO acts as an n-type semiconductor [3].

Another way to change the contact resistance is by adding a thin semiconductor layer of an oxide material between the metal and the insulator materials [3]. The semiconductor layer transforms the contact resistance from ohmic to a Schottky barrier. Without this layer, there is no switching resistance for some insulators. Sawa shows experimental results for Ti/ $Sm_{0.7}Ca_{0.3}MnO_3(n unit cells)/La_{0.7}Sr_{0.3}MnO_3/SRO$  (Ti/SCMO(n)/LSMO/SRO) where SCMO is a p-type semiconductor [3]. It was demonstrated that for n = 5 unit cells, there was a very good hysteresis in the I-V curve. As well, the SRO/SrTiO<sub>3</sub>/SrTi<sub>0.99</sub>Nb<sub>0.01</sub>O<sub>3</sub>/Ag (SRO/STO/Nb:STO) cell showed a resistivity changes but not a good hysteresis in the I-V curve [3].

### 4. One dimensional models for resistive switching materials

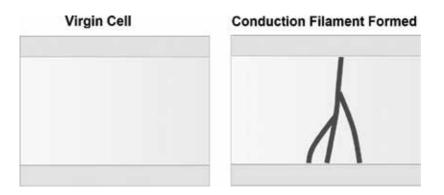

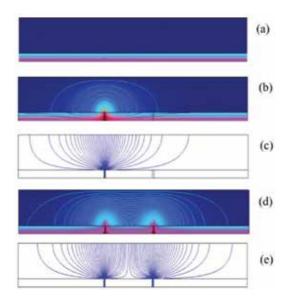

In several transition metal oxides, when a voltage is applied on the electrodes of a pristine MIM cell, the current measured is very low. When the voltage increases up to a threshold value, the electric field applied provokes a dielectric breakdown. When this occurs, a conduction filament (CF) is formed in the insulator as shown in **Figure 5**. The necessary potential to form this filament is called forming voltage ( $V_F$ ). The CF is formed due to the Joule-heating effect, which leads a temperature increment in the insulator. The dielectric breakdown is driven by a thermal runway. When a voltage is applied on a transition metal oxide, the resistance

Figure 5. Left: virgin cell. Right: Cell with conduction filament formed.

starts to decrease but not in a permanent way. In this process, the material temperature increases up to certain value (related to a threshold voltage) when a local redox reaction begins and causes structural defects (grain boundaries or dislocations) [4].

The voltage polarity to change states in cells with CF can be unipolar or bipolar. For unipolar behaviour, the electron conduction mechanism is related to thermochemical changes in the filament due to the Joule-heating effect. On the other hand, for bipolar behaviour, the electron conduction through the CF depends on redox effects or quantum point contact effects. In both cases, the switching mechanisms (SET and RESET processes) are related to the thermochemical oxygen diffusion in the CF. We can consider the CF as a 1D parameter because the material resistivity is area independent. It is very important to note that in CF programmable devices, there exist a variability problem because not all filaments are equal or similar [5].

#### 4.1. Thermochemical oxygen diffusion model

Ielmeni, Nardi and Cagli have been developed a physical model for NiO cells with very good concordance with experimental results [4]. In this material, the RESET process happens in small steps, whereas the change of states occurs suddenly during the SET process. The  $V_{\text{RESET}}$  parameters depend on the resistance material in the HRS.  $I_{\text{RESET}}$  always decreases when the resistance increases. On the other hand, the  $V_{\text{RESET}}$  in function of *R* curve has an *U* behaviour. That is, for low values of *R*,  $V_{\text{RESET}}$  decreases when *R* increases, and for high values of *R*,  $V_{\text{RESET}}$  increases when *R* increases. For the RESET process, the CF temperature depends on the square of the applied voltage as follows [4]:

$$T = T_0 + \frac{R_{\rm th}}{R} V^2 \tag{2}$$

where  $T_0$  is the room temperature and  $R_{\text{th}}$  is the effective thermal resistance. By using Eq. (2), we can obtain the  $V_{\text{RESET}}$  voltage:

$$V_{RESET} = \sqrt{\frac{R\Delta T_{RESET}}{R_{th}}}$$

(3)

where  $\Delta T_{\text{RESET}}$  is the critical temperature increment for the onset oxidation. The ratio  $R/R_{\text{th}}$  is almost constant according to the Wiedemann-Franz law for metals [4]. This means that  $V_{\text{RESET}}$  is almost constant and  $I_{\text{RESET}}$  decreases with respect to R. This is not true in experimental results. For explaining the increment of  $V_{\text{RESET}}$  with respect to high values of R, we have to study the sizedependent Joule-heating effect. The parameter  $R_{\text{th}}$  is the parallel of two resistances:  $R_{\text{th}}'$  and  $R_{\text{th}}''$ , where  $R_{\text{th}}'$  only depends on the CF and  $R_{\text{th}}''$  depends on the rest of the material (bulk oxide).  $R_{\text{th}}'$ can be computed by considering the thermal nanofilament conductivity,  $k_{\text{th}}$ , as follows [4]:

$$R_{\rm th}' = \frac{t_h}{8k_{\rm th}A_{\rm CF}} \tag{4}$$

where  $t_h$  is the oxide thickness and  $A_{CF}$  is CF area. As  $R_{th}$  is inverse proportional to  $A_{CF}$ , for high values of  $A_{CF}$  (low resistance)  $R_{th}$  is approximately  $R_{th}$ '. On the other hand, for low values of ACF, we have that  $R_{th} \approx R_{th}$ ". As well, when  $k_{th}$  increases,  $R_{th}$ ' predominates over  $R_{th}$ ". For explaining the behaviour of the  $V_{\text{RESET}}$ -R curve for low values of R, we have to consider that the ratio  $R/R_{\text{th}}$  is almost constant in Eq. (3) and  $\Delta T_{\text{RESET}}$  must increase in order to obtain a metal diffusion in the filament, which is a filament area dependent process. Hence,  $V_{\text{RESET}}$  increases for low values of R. This size-dependent diffusion is considering in following Arrhenius expression developed in Ref. [4]:

$$T_{RESET} = \frac{E_A}{k \log\left(\frac{t_{RESET}}{t_0} \left(\frac{\varphi_0}{\varphi}\right)^2\right)}$$

(5)

where  $E_A$  is the activation energy, k the Boltzmann constant,  $t_0$  and  $\phi_0$  are constants,  $\phi$  is the CF diameter and  $t_{\text{RESET}}$ = 1s is the reset time. Ielmini et al. showed very good results between their model and experimental data of NiO devices [4].

The electron conduction mechanism in the LRS strongly depends on the activation energy. For low values of  $E_{AV}$  the filament has a metallic behaviour and the resistance is given by:

$$R = R_{0m}(1 + \alpha(T - T_0))$$

(6)

where  $T_0$  is the room temperature,  $R_{0m}$  is the metallic resistant at  $T_0$  and  $\alpha$  is the temperature coefficient. On the other hand, for high values of  $E_A$ , electron conduction is driven by the Pool-Frenkel model in semiconductors and the resistance follows the following equation:

$$R = R_{0s} \exp\left(\frac{E_{AC}}{kT}\right) \tag{7}$$

where  $R_{0s}$  is the extrapolated resistance at infinite *T*, *k* is the Boltzmann constant and  $E_{AC}$  is the activation energy for conduction. Both conduction behaviours are related to position of Fermi level ( $E_F$ ). Inside the CF filament, there are oxygen vacancies, whereas the bulk oxide is doped by oxygen. An insulator doped by oxygen behaves as a p-type semiconductor and, on the other hand, oxygen vacancies provoke an n-type behaviour. Therefore, the conduction filament in LRS behaves as an n-type semiconductor and the electron conduction is modulated by the concentration of oxygen vacancies, which is directly related to the  $E_F$  position. When the oxygen vacancies concentration is too high, the CF behaves as a degenerately doped semiconductor and  $E_F$  is very close or above the conduction band [4].

As was mentioned before, the SET process happens suddenly and it strongly depends on the resistance of the HRS (before the SET process). The HRS resistance can be described by the Pool-Frenkel model and is given by Ielmini et al. [4]:

$$R = \frac{kT\tau_0 t_h}{q^2 A_{\rm CF} N_T \Delta z^2} \exp\left(\frac{E_{AC}}{kT}\right) \tag{8}$$

where  $\tau_0$  is the attempt-to-escape characteristic time for a carrier from a specific state,  $t_h$  is the material thickness (or filament length),  $N_T$  is the dopant density,  $A_{CF}$  is the filament area and  $\Delta z$  is the distance between positive charged defects. Ielmini et al. showed, from experimental

data, that necessary power for the setting process ( $P_{\text{SET}}$ ) is directly proportional to  $R^{-0.5}$ , which means that [4]:

$$V_{\rm SET} = \frac{P_{\rm SET}}{I_{\rm SET}} = \sqrt{P_{\rm SET}R} \propto R^{0.25}$$

(9)

$$I_{\text{SET}} = \frac{P_{\text{SET}}}{V_{\text{SET}}} = \sqrt{\frac{P_{\text{SET}}}{R}} \propto R^{-0.75}$$

(10)

The tendencies for  $V_{\text{SET}}$  and  $I_{\text{SET}}$  parameters in function of *R* were experimentally confirmed the Ielmini group in Ref. [4].

#### 4.2. Trap-assisted-tunnelling model

In bipolar cells, the transition between the LRS and the HRS is commonly related to the formation and rupture of the CF. A typical material which presents a CF with bipolar behaviour is the HfO<sub>2</sub>. As well as in unipolar cells, oxygen vacancies play an important role. The most accepted theory for forming the CF in a virgin cell is that the oxygen atoms migrate from the CF to the insulator/metal interface due to the Joule-heating effect. When the CF is already formed, to change from the LRS to the HRS, the CF is oxidized (oxygen atoms migrate from the electrode to the CF), whereas to change from the HRS to the LRS, the CF is reduced leaving oxygen vacancies and forming percolation paths (oxygen atoms migrate from the CF to the electrode).

Guan, Yu and Wong have developed a model for explaining the carrier conduction through the CF in bipolar cells where the principal transport mechanism is the trap-assisted-tunnelling (TAT). The continuity transport equation in the oxide region is given by Guan et al. [6]:

$$\frac{df_n}{dt} = (1 - f_n) \sum_{m=1, \ m \neq n}^N R_{mn} f_m - f_n \sum_{m=1, \ m \neq n}^N R_{mn} (1 - f_n) + (R_n^{iL} + R_n^{iR})(1 - f_n) - (R_n^{oL} + R_n^{oR}) f_n$$

(11)

where  $f_n$  is the electron occupation probability of the *n*th trap,  $R_{mn}$  is the electron hopping rate from trap *n* to trap *n*,  $R_n^{oL}/R_n^{oR}$  are the electron hopping rate from trap *n* to the right/left electrode and  $R_n^{iL}/R_n^{iR}$  the electron hopping rate from the right/left electrode to trap *n*. It is well known that oxygen vacancies contribute to the TAT. In quasi-steady state, Eq. (11) transform to [6]:

$$(1-f_n)\sum_{m=1,\ m\neq n}^{N} R_{mn}f_m - f_n\sum_{m=1,\ m\neq n}^{N} R_{mn}(1-f_n) + (R_n^{iL} + R_n^{iR})(1-f_n) - (R_n^{oL} + R_n^{oR})f_n = 0 \quad (12)$$

The current can be computed by evaluating the electron flow near the electrode:

$$I = I^{L} = I^{R} = -q \sum_{n=1}^{N} \left( (1 - f_{n}) R_{n}^{iL} - f_{n} R_{n}^{oL} \right) = -q \sum_{n=1}^{N} \left( (1 - f_{n}) R_{n}^{iR} - f_{n} R_{n}^{oR} \right)$$

(13)

The hopping rate can be computed by the Mott hopping model as [7]:

$$R_{mn} = R_0 \exp\left(-\frac{r_{mn}}{a_0} + \frac{qV_{mn}^H}{kT}\right)$$

(14)

where  $R_0 \approx 10^{12}$ Hz is the vibration electron frequency,  $r_{mn} = |r_m - r_n|$  is the distance between vacancies *n* and *m*,  $a_0$  is the attenuation length wave function,  $V_{mn}^{H} \approx -F^{H}(r_m - r_n) \approx V^{H}(r_m) - V^{H}(r_n)$  is the barrier change due to an external electric field and  $V^{H}(r_n)$  is the homogeneous component of the potential solution of the Poisson equation. The hopping rates from a trap to an electrode are [6]:

$$R_{n}^{iL,R} = R_{\text{tunnel}}^{0} N^{L,R}(E_{v}^{+}) F_{\text{in}}^{L,R}(E_{v}^{+}) T_{n}^{L,R,+}$$

$$R_{n}^{oL,R} = R_{\text{tunnel}}^{0} N^{L,R}(E_{v}^{\bullet}) F_{\text{out}}^{L,R}(E_{v}^{\bullet}) T_{n}^{L,R,\bullet}$$

(15)

where e  $R^0_{\text{tunnel}}$  is the tunnel coupling strength between a trap and an electrode,  $N^{L,R}$  is the number of states at a given energy in an electrode and  $E_v^+/E_v^{\bullet}$  are the energy of an empty/ filled trap given by Guan et al. [6]:

$$E_{v}^{+,\bullet}(r_{n}) = E_{v}^{+,\bullet} - qV^{H}(r_{n})$$

(16)

$T_n^{L,R,+\bullet}$  is the tunnel probability from the left/right electrode into a trap given by the Wentzel-Kramers-Brilloin approximation [6]:

$$T_{n}^{L+,\bullet} = \exp\left[\int_{0}^{x_{n}} \frac{1}{h} \sqrt{2m^{*} [E_{C} - E_{v0}^{+,\bullet} - qV^{H}(x_{n})]} dx\right], \quad E_{v}^{\pm} < E_{C} - qV^{H}(x)$$

$$T_{n}^{R+,\bullet} = \exp\left[\int_{x_{n}}^{L} \frac{1}{h} \sqrt{2m^{*} [E_{C} - E_{v0}^{+,\bullet} - qV^{H}(x_{n})]} dx\right], \quad E_{v}^{\pm} < E_{C} - qV^{H}(x)$$

(17)

where  $x_n$  is the *x*th component of  $r_n$ , L is the oxide thickness and  $m^*$  is the tunnelling effective mass in the oxide.  $F_{in}^{L,R}$  is the Fermi integral which represents the filled states in an electrode above  $E_v^+$  and takes into account the inject electrons from the electrode into the trap n:

$$F_{in}^{L,R}(E_v^+) = \int_{E_{v0}^+ - qV(x_n)}^{+\infty} f\left(E - (E_F^{L,R} - qV^{L,R})dE\right) = \int_{E_{v0}^+ - qV(x_n)}^{+\infty} \frac{1}{1 + \exp\left((E - (E_F^{L,R} - qV^{L,R})/kT\right)} dE$$

(18)

where  $E_{\rm F}^{L,R}$  is the Fermi level of the right/left electrode and  $V^{L,R}$  is the applied voltage on the left/right electrode. On the other hand,  $F_{\rm out}^{L,R}$  is the Fermi integral which takes into account the number of empty states in an electrode bellow  $E_{\rm v}^{-}$  which can accept electrons from the trap *n*:

$$F_{out}^{L,R}(E_v^-) = \int_{-\infty}^{E_{v0}^- - qV(x_n)} \left[1 - f\left(E - (E_F^{L,R} - qV^{L,R})\right)\right] dE = \int_{-\infty}^{E_{v0}^- - qV(x_n)} \frac{1}{1 + \exp\left((E_F^{L,R} - qV^{L,R}) - E/kT\right)} dE$$

(19)

According to Guan et al. model, the generation oxygen vacancies are given by [7]:

$$P_G(F^{eq}, T, t) = \frac{t}{t_0} \exp\left(-(E_a - \gamma |F^{eq}|)/kT\right)$$

(20)

where the time, *t*, is within the interval  $[\tau, \tau + t]$ ,  $F^{eq}$  is the local electric field of an ion,  $1/t_0 \approx 10^{13}$ Hz is the oxygen vibration frequency,  $E_a \approx 1$ eV is a parameter related to the height of the potential barrier and  $\gamma$  is a coefficient which represents the local enhancement due to the electric field. This rate dominates the SET process.

On the other hand, during the equilibrium state (absence of  $F^{eq}$ ), the oxygen vacancy recombination rate is given by Guan et al. [6]:

$$P_R^0 = P_G(F^{eq} = 0, T, t) = \frac{t}{t_0} \exp\left(-E_a/kT\right)$$

(21)

Therefore, the recombination rate for a non-equilibrium state is [7]:

$$P_R = \beta P_R^0$$

where  $\beta$  is a parameter related to concentration of oxygen ions which can be computed by the following approximation [6]:

$$\beta(x,t) = \beta_0 \exp\left(-\frac{vt}{L_p}\right) u(x,t)$$

(22)

where  $L_p$  is decaying length of ion concentration, u(x,t) is a function related to the oxygen diffusion and can be approximated by the complementary error function. v is velocity of the oxygen ions waveform given by Yu et al. [7]:

$$v = \frac{a}{t_0} \exp\left(-E_m/kT\right) \sinh\left(q\gamma^{drift}F/kT\right)$$

(23)

where *a* is the lattice constant,  $E_m$  is the migration barrier,  $\gamma^{drift}$  is the enhancement coefficient related to the dielectric material and *F* is the electric field left by an oxygen ion. Eq. (13) is coupled with the solution of the Poisson equation to obtain the potential distribution in the cell:

$$-\nabla^2 V = \frac{\rho}{\varepsilon} \tag{24}$$

where  $\rho$  is the volumetric charge density and  $\varepsilon$  is the material permittivity. The border conditions for Eq. (24) are:  $V(x=0)=V^L$  and  $V(x=L)=V^R$ . Guan et al. showed very god results of their model for experimental data of HfO<sub>x</sub> devices [7].

#### 4.3. Quantum point contact model

The complete quantum point contact (QPC) model was developed by Miranda and Suñe [8]. Originally, the model was developed for explaining the soft and hard-dielectric-breakdown in SiO<sub>2</sub>. If the dimension of the narrowest point of the CF is in the order of the Fermi wavelength,  $\lambda_{\rm F}$ , quantum point contact effects are presented. There are some experimental works, where the QPC model could explain well the transport conduction in the HRS and LRS for HfO<sub>2</sub> devices [9–11].

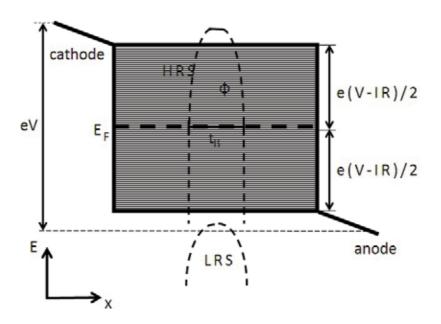

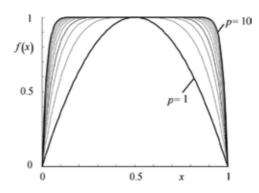

According to the QPC model, the first quantized sub-band behaves as a potential barrier for the incoming electrons as shown in **Figure 6**. We used a parabolic potential as potential barrier with the following physical parameters:  $\Phi$  being the potential barrier height measured at the Fermi level,  $t_B$  is the potential thickness at the Fermi level, R is a series resistance external to the constriction, V is the applied voltage on the electrodes, q is the elementary electron charge and I is the filament current that flows in the x direction.

The potential barrier height is defined by the cross-sectional area of the constriction and determines two conduction states. For the HRS, the top of the potential barrier is above or inside the energy window and the dominant conduction mechanism is tunnelling (this description is valid only for low-voltages). On the other hand, if the top of the potential barrier is below the energy window, the cell is in the LRS and the conduction mechanism is essentially ballistic (transmission probability close to 1). The conduction in the LRS is independent of the

**Figure 6.** Energy band diagram of the narrow constriction, where *V* is the applied voltage on the electrodes, *R* is an external series resistance that takes into account the non-idealities of the model, *I* is the filament current, e(V-IR) is the energy window associated to the electron conduction (shaded region), EF is the Fermi level,  $\Phi$  is the potential height with respect to *EF*, *tB* is the potential thickness at *EF* and e is the elementary electron charge. The conduction is in the *x* direction. The top of the potential barrier is above or inside the energy window for the HRS and below for the LRS.

potential barrier. By assuming a parabolic potential barrier in the narrow constriction and by using the Landauer formalism for 1D quantum conductors and the zero-temperature limit for the parabolic potential barrier, the current through the filament is [9, 10]:

$$I = \frac{2e}{h} N \int_{-e(V-IR)/2}^{e(V-IR)/2} T(E) dE$$

(25)

where T(E) is the electron transmission probability, N is the number of active channels in the filament and h is the Planck's constant. For a parabolic potential barrier, there is an analytical expression for T(E):

$$T(E) = \left(1 + \exp\left(-\alpha(E - \Phi)\right)^{-1}\right)$$

(26)

where  $\alpha$  is a shape parameter related to  $t_{\rm B}$ . By integrating over the total energy window, we have that the filament current is [9, 10]:

$$I = \frac{2eN}{h} \left\{ e(V - IR) + \frac{1}{\alpha} \ln \left[ \frac{1 + \exp\left\{ \alpha [\Phi - e(V - IR)/2] \right\}}{1 + \exp\left\{ \alpha [\Phi + e(V - IR)/2] \right\}} \right] \right\}$$

(27)

If we consider  $V \gg IR$  and only one active filament for the HRS (not multiple filaments), we obtain [9, 10]:

$$I \approx \frac{2e}{h} \left\{ eV + \frac{1}{\alpha} \ln \left[ \frac{1 + \exp\left\{ \alpha [\Phi - eV/2] \right\}}{1 + \exp\left\{ \alpha [\Phi + eV/2] \right\}} \right] \right\}$$

(28)

For the LRS, we suppose an ideally ballistic transport that  $(T(E) \approx 1)$  and the current is [9, 10]:

$$I \approx \frac{NG_o}{1 + NG_o R} V \tag{29}$$

where  $G_0 = 2q^2/h$  is the quantum conductance unit.

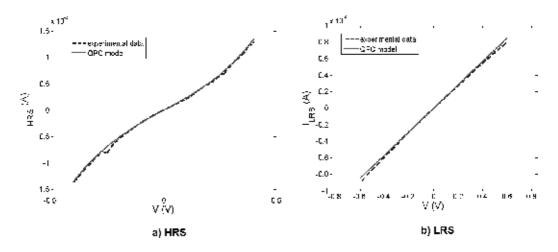

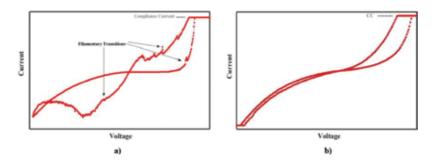

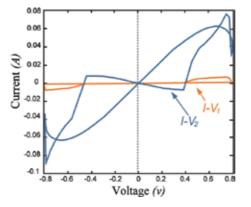

We show in **Figure 7** experimental results of I-V curves for the HRS and LRS and its fitting with the QPC model for HfO<sub>2</sub> cells. We have found in Ref. [10] that  $\alpha \propto \Phi^n$  with n = -0.35. There is a QPC expression which relates  $\Phi$  and  $\alpha$  by considering  $t_B$  constant [9, 10]:

$$t_B = \frac{h\alpha}{2\pi^2} \sqrt{\frac{2\Phi}{m^*}} \tag{30}$$

where  $m^*$  is the electron effective mass in the constriction. Moreover, the constriction radius,  $r_{B}$ , can be extracted by using another QPC equation [9, 10]:

$$r_{\rm B} = \frac{hz_o}{2\pi\sqrt{2m*\Phi}} \tag{31}$$

where  $z_0$ = 2.404 is the first zero of the Bessel function  $J_0$ . In Ref. [10], we have experimentally found that  $r_{\rm B}$ = 1.14 nm with a standard deviation of 0.06 nm for bipolar HfO<sub>2</sub> cells, which

Figure 7. Experimental and theoretical I-V characteristics for the (a) HRS and (b) LRS. The QPC model (Eqs. (28) and (29)) was used for theoretical curves.

agrees with the quantum approach of this model. Miranda et al. showed that  $\Phi$  has a linear dependence with respect to the temperature given by Avellán et al. [12]:

$$\Phi(T) = \Phi_0 - \gamma T \tag{32}$$

where  $\Phi_0$  is a potential height at a  $T_0$  temperature (a given temperature) and  $\gamma$  is a temperature coefficient. For extracting  $\gamma$ , we can use the following expression [12]:

$$\frac{d(\log[I/1A])}{dT}\ln(10) = \alpha\gamma \tag{33}$$

This dependence has been probed in experimental results of HfO<sub>2</sub> cells in Ref. [10].

#### 5. Conclusions

We have presented a classification of physical models for explaining the resistive switching mechanisms in chalcogonides materials. In the literature, there are many physical models proposed for explaining the electron conduction and switching mechanism in specific materials and fabrication process conditions. In the present work, we divide the models according to the number of material dimensions involved on the resistive switching mechanism. The phase change mechanism (PCM) is presented in some Te-alloys used an optical storage devices. In this switching mechanism, the material changes from the amorphous phase to the crystalline phase. Because of the resistivity affects the complete cell volume, the phase change mechanism is considered a 3D model. On the other hand, the modulation of the resistive contact is a 2D model because the defect concentration only affects the metal/insulator interface. This mechanism is presented in some perovskite materials.

The principal component of 1D models is the presence of a conduction filament. The filament is formed in a virgin cell by applying a certain threshold voltage. Depending on the cell polarity, the transport mechanisms can be: thermochemical diffusion of oxygen, filament oxidation-reduction or quantum point contact. For unipolar cells (like NiO cells), the resistive switching and the carrier conduction are controlled by the thermochemical diffusion of oxygen in the CF due to the Joule-heating effect. For bipolar cells (like HfO<sub>2</sub>), the switching mechanism is related to the oxidation/reduction of CF. If the CF radius at the narrowest part of the CF is in the order of the Fermi wavelength, the transport is driven by the quantum point contact effect, otherwise the transport depends on the oxidation/reduction of CF.

## Author details

Luis-Miguel Procel-Moya

Address all correspondence to: lprocel@usfq.edu.ec

Instituto de Micro-Nanoelectrónica, Universidad San Francisco de Quito, Quito, Ecuador

## References

- Waser R, Wuttig M. Function by defects at the atomic scale new concepts for nonvolatile memories. In: Proceedings of ESSCIRC; IEEE.org, USA. Athens, Greece. 14–18 November 2009. pp. 65-72

- [2] Wuttig M, Yamada N. Phase-change materials for rewriteable data storage. Nature Materials. 2007;6:824-832

- [3] Sawa A. Resistive switching in transition metal oxides. Materials Today. 2008;11:28-36

- [4] Ielmini D, Nardi F, Cagli C. Physical models of size-dependent nanofilament formation and rupture in NiO resistive switching memories. Nanotechnology. 2011;22:254022-1-254022-12

- [5] Degraeve R, Fantini A, Raghavan N, Goux L, Clima S, Govoreanu B, Belmonte A, Linten D, Jurczak M. Causes and consequences of the stochastic aspect of filamentary RRAM. Microelectronic Engineering. 2015;147:171-175

- [6] Guan X, Yu S, Philip Wong H -S. On the switching parameter variation of metal-oxide RRAM—Part I: Physical modeling and simulation methodology. Transactions on Electron Devices. 2012;59:1172-1182

- [7] Yu S, Guan X, Philip Wong H-S. On the switching parameter variation of metal oxide RRAM—Part II: Model corroboration and device design strategy. IEEE Transactions on Electron Devices. 2012;59:1183-1188

- [8] Miranda E, Suñé J. Analytic modeling of leakage current through multiple breakdown paths in SiO<sub>2</sub> films. In: IEEE International Proceedings Reliability Physics Symposium. IEEE.org, USA; Orlando. USA. 30 April–3 May 2001. pp. 367-379

- [9] Miranda E, Walczyk C, Wenger C, Schroeder T. Model for the resistive switching effect in HfO<sub>2</sub> MIM structures based on the transmission properties of narrow constrictions. IEEE Electron Device Letters. 2010;31:609-611

- [10] Procel LM, Trojman L, Moreno J, Crupi F, Maccaronio V, Degraeve R, Goux L, Simoen E. Experimental evidence of the quantum point contact theory in the conduction mechanism of bipolar HfO<sub>2</sub>-based resistive random access memories. Journal of Applied Physics. 2012;074509:074509 (1-5)

- [11] Degraeve R, Roussel Ph, Goux L, Wouters D, Kittl J, Altimime L, Jurczak M, Groeseneken G Generic learning of TDDB applied to RRAM for improved understanding of conduction and switching mechanism through multiple filaments. In: IEEE International Electron Devices Meeting. IEEE.org, USA; San Francisco. USA. 6–8 December 2010. pp. 632-635

- [12] Avellán A, Miranda E, Schroeder D, Krautschneider W Model for the voltage and temperature dependence of the soft breakdown current in ultrathin gate oxides. Journal of Applied Physics. 2005;014104:014104-1-014104-5

# **Graphene Oxide-Based Memristor**

Geetika Khurana, Nitu Kumar, James F. Scott and Ram S. Katiyar

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.69752

#### Abstract

A memristor is the memory extension to the concept of resistor. With unique superior properties, memristors have prospective promising applications in non-volatile memory (NVM). Resistive random access memory (RRAM) is a non-volatile memory using a material whose resistance changes under electrical stimulus can be seen as the most promising candidate for next generation memory both as embedded memory and a stand-alone memory due to its high speed, long retention time, low power consumption, scalability and simple structure. Among carbon-based materials, graphene has emerged as wonder material with remarkable properties. In contrast to metallic nature of graphene, the graphene oxide (GO) is good insulating/semiconducting material and suitable for RRAM devices. The advantage of being atomically thin and the two-dimensional of GO permits scaling beyond the current limits of semiconductor technology, which is a key aspect for high-density fabrication. Graphene oxide-based resistive memory devices have several advantages over other oxide materials, such as easy synthesis and cost-effective device fabrication, scaling down to few nanometre and compatibility for flexible device applications. In this chapter, we discuss the GO-based RRAM devices, which have shown the properties of forming free, thermally stable, multi-bit storage, flexible and high on/ off ratio at low voltage, which boost up the research and development to accelerate the GO-based RRAM devices for future memory applications.

Keywords: memristor, graphene oxide, forming free, multi-bit storage, flexible devices

## 1. Introduction

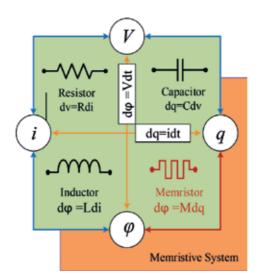

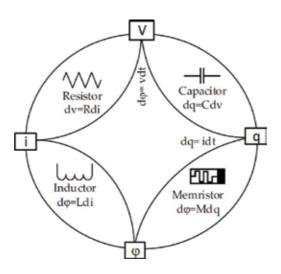

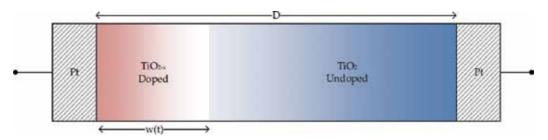

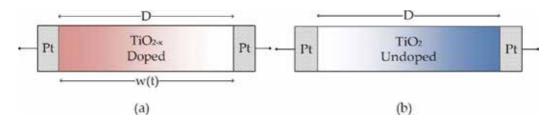

The memristor (contraction for memory resistor) acclaimed as the fourth fundamental circuit element together with already known the capacitor, the inductor and the resistor was theoretically predicted by Chua in 1971 [1]. But it attracted much attention in 2008, when a

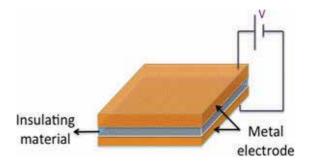

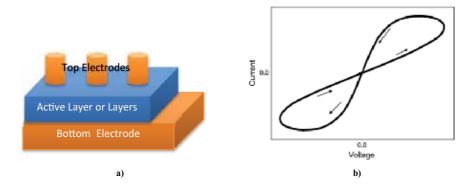

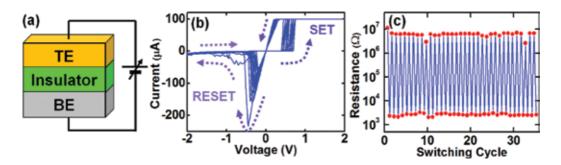

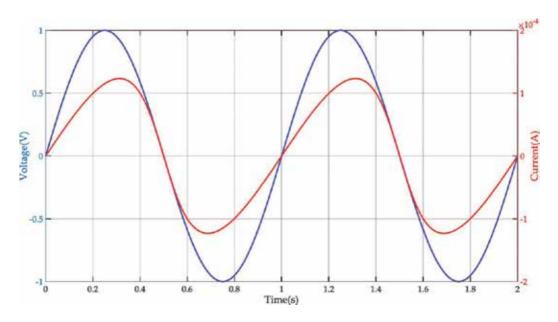

TiO<sub>2</sub>-based crossbar memory array was developed by the HP Labs, and the cross-point storage element was recognized as the memristor [2]. Recently, a rather deep analysis has been provided concerning memristors [3], which shows conclusively that the memristor is not the longsought fourth circuit element but the memory extension to the concept of resistor. With unique superior properties, memristors have promising applications in non-volatile memory (NVM), artificial neural networks, programmable logic devices, signal processing and pattern recognition circuits. Random access memory (RAM) is an important form of computer data storage. However, due to the technological and physical limitations imposed by dynamic random access memory (DRAM), static random access memory (SRAM) and flash memory towards low power, small size, fast speed, high density and non-volatility, there is an urgent need of upcoming NVM technologies with low power, high density, high read/write endurance and scalability. In a memristor, a new memory device to solve these problems, a resistive random access memory (RRAM) is a good direction for the development of future memory technology. RRAM is a memory using a material whose resistance changes under electrical stimulus and can be seen as the most promising candidate for next generation memory both as embedded memory and a stand-alone memory due to its high speed, long retention time, low power consumption, scalability and simple structure [4]. Typically, RRAM is a two-terminal device that the switching medium is sandwiched between top and bottom electrodes (Figure 1) and the resistance of the switching medium can be modulated by applying electrical signal (current or voltage) to the electrodes. Appropriate value of programming voltage pulse can set the device from high-resistance state (HRS) to low-resistance state (LRS) known as SET or writing process. Similarly, switching back of the device from LRS to HRS using a voltage pulse known as RESET or erase process. Based on the voltage polarity used, RRAM can be categorized into two types: unipolar and bipolar resistive switching [5]. The switching operation is called unipolar, if the SET and RESET processes occur at the same voltage polarity. In the SET process, the current is usually constrained by current compliance. Whereas, the switching is bipolar if the SET and RESET processes occur at reversed polarity of voltages. In both switching modes, two resistance states are distinguished from each other at a small read-out voltage, therefore read operation has no influence on the resistance state. However, the attractive properties of RRAM are low fabrication costs, scalability into the nanometre regime, fast write and read access, low power consumption and low threshold voltages.

Figure 1. Schematic and electrical configuration of a two-terminal RRAM cell.

The resistive switching effect has been explored until now in several materials including transition metal oxides, perovskite oxides, organic materials and carbon-based materials. Carbonbased materials have been researched extensively as an important class of materials for many years to defeat the technological barriers of conventional semiconductor electronics [6-8]. Previously, the efforts have been made to fabricate the field effect transistor (FET) devices [9, 10] based on carbon materials. Therefore, it is highly demandable to fabricate carbon-based memory devices to integrate logic and memory devices based on same material. This chapter introduces RRAM properties of the carbon compound known as graphene oxide (GO). It is basically a wrinkled two-dimensional carbon sheet with various oxygenated functional groups attached to its basal plane and peripheries, with the thickness of around 1 nm and lateral dimensions varying between a few nanometres and several microns. Graphene oxide has been synthesized by various chemical methods, such as Hummers' method and its modification, Brodie method and Staudenmaier method. In contrast to the metallic nature of graphene, the graphene oxide is good insulating/semiconducting material, which can be readily obtained by oxidizing graphite with strong oxidants.GO sheets are heavily oxygenated, bearing hydroxyl and epoxide functional groups on their basal planes, in addition to carbonyl and carboxyl groups located at the sheet edges. Furthermore, the ability of these sheets to form covalent as well as non-covalent (based on interactions) bonds encourages the fabrication of a wide variety of hybrid structures such as transistors, sensors, optoelectronic and memory devices etc. [11, 12]. The two dimensionality of GO permits scaling beyond the current limits of semiconductor technology, which is a key aspect for high-density fabrication. Out of tremendous applications of graphene oxide, this chapter focuses on the memory device application. Graphene oxide (GO) with an ultrathin thickness is attractive due to its unique physical-chemical properties. GO can be readily obtained through oxidizing graphite in mixtures of strong oxidants, followed by an exfoliation process. The presence of these functional groups makes GO sheets electrically insulating, with characteristics comparable to other thin-layered oxide materials, with the advantage of being atomically thin, which makes GO the perfect candidate for the fabrication of memristive devices [13, 14]. As GO is water soluble which makes it facile to transfer onto any substrate in thin film form by simple methods of spin coating, drop-casting, Langmuir-Blodgett (LB) and vacuum filtration. The as-deposited GO thin films can be further processed into functional devices using standard lithography processes without degrading the film properties [15, 16]. Furthermore, the band structure and electronic properties of GO can be modulated by changing the quantity of chemical functionalities attached to the surface. Therefore, GO is potentially useful for microelectronics production.

### 2. Status of graphene oxide-based RRAM devices

Graphene oxide-based resistive memory devices have several advantages, such as easy synthesis and cost-effective device fabrication, scaling down to few nanometres and compatibility for flexible device applications. Reliable and reproducible resistive switching behaviour was first reported in graphene oxide thin films prepared by the vacuum filtration method by He et al. in 2009 [17]. They observed very low switching voltages and low on/off ratio of about 20 in Cu/GO/Pt structure. Soon after that there were many reports published showing high on/off ratios in GO-based RRAM devices [18, 19]. Mechanism for the resistive switching characteristics in GO-based RRAM was found to be due to the oxygen migration, oxygen vacancies and the electrode diffusion [20, 21]. Furthermore, Jeong et al. presented a GO-based memory that can be easily fabricated using a room temperature spin-casting method on flexible substrates and has reliable memory performance in terms of retention and endurance [22]. Resistive switching effect was shown in Ni-doped graphene oxide by Pinto et al. [23]. Transparent nonvolatile memory device based on SiOx and graphene was also reported which features high transparency, long retention time and low programming currents [24]. Zhuge et al. reported the forming voltage dependence on GO film thickness and on different top electrodes [20]. Forming process is the application of initial high voltages to the devices to initiate the switching process, which is detrimental to the device structure and operation. Forming-free GO RRAM devices having high on/off ratio with good retention and endurance properties are potential candidates for non-volatile RRAM. Therefore, in this chapter, we will be discussing RRAM properties of the GO-based devices, which are forming free, thermally stable, multi-bit storage, flexible, having high on/off ratio at low operating voltages that boost up the research and development to accelerate the GO-based RRAM devices for future memory applications.

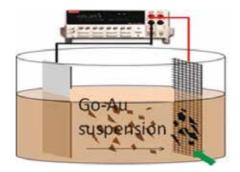

#### 2.1. Graphene oxide-based RRAM devices

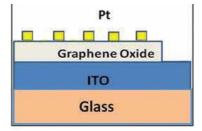

Synthesis of graphene oxide presented in this chapter has been carried out by modified Hummers method [25, 26]. In brief, highly oriented pyrolytic graphite (HOPG, 2 g) was oxidized using potassium permanganate (KMnO<sub>4</sub>, 7 g) in the presence of concentrated H<sub>2</sub>SO<sub>4</sub> (50 ml) in ice bath. After the reaction, excess distilled water was added to the solution. With continuous stirring a 30 wt.% of hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) was added slowly until the gas evolution had stopped. Further 15 more-minute stirring was done to the resultant mixture, and then it was filtered through nylon membrane. Repeated washing was done by distilled water and 5% HCl solution until the filtrate was neutral. Finally, the obtained dark brown slurry was dried for 24 hour in a vacuum oven at 60°C. A colloidal suspension of GO was prepared in distilled water by sonicating graphite oxide in water for 2 hour. Such a solution of GO was used to fabricate the thin films by spin coating process on ITO/Glass substrate. To construct metal-insulator-metal (MIM) devices, platinum top electrodes with an area of 40 × 40  $\mu$ m<sup>2</sup> were deposited by DC sputtering utilizing a shadow mask. The schematic representation of fabricated Pt/graphene oxide/imdium-tin oxide (GO/ITO) is shown in **Figure 2**.

Figure 2. Schematic representation of GO-based MIM devices [26].

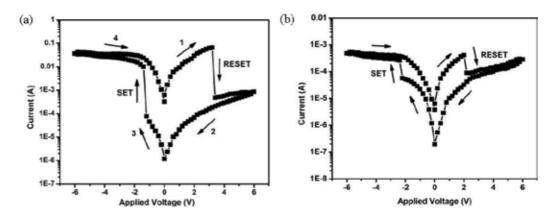

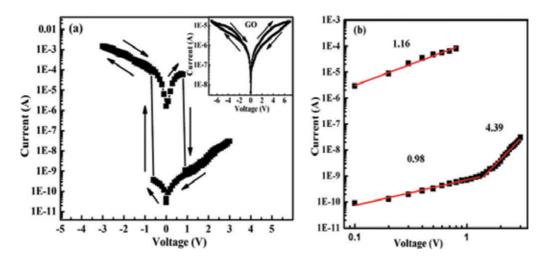

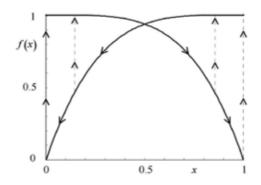

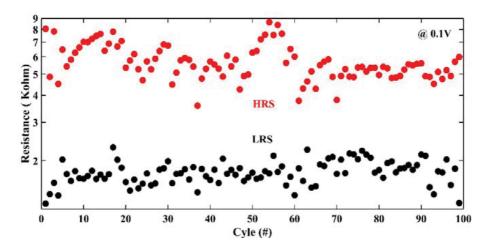

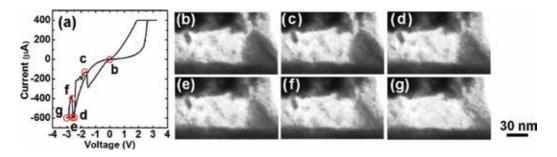

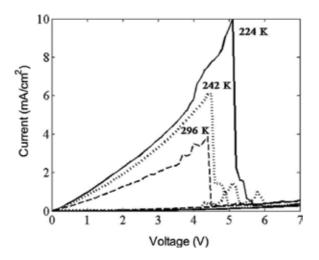

To observe the switching characteristics of the device, I-V measurements for the Pt/GO/ITO device at 300 and 500 K were performed as shown in **Figure 3a** and **b**). The Pt/GO/ITO device was found initially in low-resistance state having resistance value of ~40 ohm. **Figure 3** shows that as the positive voltage was increased, a sudden fall in current was observed at a voltage of ~3.2 V indicating abrupt increase in the resistance of the device. This is known as RESET process and device transformed from its initial low-resistance state (LRS) to high-resistance state (HRS) also known as OFF state.

The low-resistance state of GO-based MIM devices once obtained persisted even when the applied voltage was reduced to zero indicating non-volatility. In high-resistance state, when the voltage was swept a sudden increase in current was observed at a voltage of approximately -1.2 V indicating abrupt decrease in the resistance of device and switching from highresistance state to low-resistance state as shown in Figure 3a. This is known as the SET process which switched the MIM device in LRS or ON state. The LRS of device remained preserved even when the applied bias voltage was removed. During this set process, current compliance was kept fixed at 100 mA to avoid the breakdown of GO film due to high current flow in lowresistance state. By repeating the set and reset processes over 100 cycles, it was observed that the reset voltage was larger than the set voltage and spread over a small window of voltage between ~3 and 3.4 V, whereas the set voltage had a spread between approximately -1.2 and -1.8 V. Thus, the device showed a typical bipolar resistive switching (BRS) behaviour with an on/off current ratio of 10<sup>4</sup> over 100 test cycles. Switching characteristics of the device were also studied at elevated temperature of 500 K (as shown in Figure 3b). Reduction in the value of reset voltage at 500 K was observed which could be attributed to enhanced diffusivity of oxygen ions at elevated temperature compared to that of room temperature. However, contrary to that we found increment in the set voltage at elevated temperature. Further at high temperature of 500 K, the on/off ratio of the device was found to decrease up to  $\sim 10^2$  compared to its value at 300 K which was  $\sim 10^4$ ; however, this ratio of high- and low-resistance states is sufficient for operation of memory devices. Low- and high-resistance states were stable up to 10<sup>4</sup> seconds and up to 100 cycles indicating good retention and endurance characteristics of the device at elevated temperature of 500 K.

Figure 3. Current-voltage characteristics of the Pt/GO/ITO device at (a) 300 K and (b) 500 K [26].

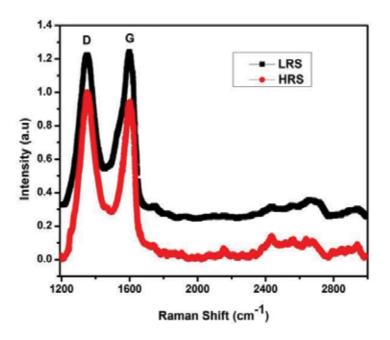

Based on the conduction mechanism, it was observed that GO device contains conducting paths between top and bottom electrode perhaps due to the presence of oxygen vacancies and electron traps in graphene oxide layer forming electron hopping path [27]. Presence of oxygen vacancies in graphene oxide indicates partial reduction of GO and dominance of sp<sup>2</sup> character over sp<sup>3</sup> character providing high conducting channel in GO film and initial low-resistance state without any forming process. In Pt/GO/ITO devices, the bottom electrode ITO acts as a source/reservoir of oxygen ions [28]. To ascertain the presence of sp<sup>2</sup> and sp<sup>3</sup> characters of carbon, Raman spectroscopy measurements were carried out on the Pt/GO/ITO devices both in LRS and HRS and are shown in **Figure 4**. As can be seen in **Figure 4** that in case of as-grown device and the device in LRS, the presence of G peak signifying the sp<sup>2</sup> character is larger in intensity compared to the same peak when the device was switched into HRS by the application of suitable bias voltage. This indicates that the sp<sup>2</sup> character dominates in LRS. While in case of HRS, the sp<sup>2</sup> character is suppressed. These RRAM devices based on GO layer fabricated by a simple process of spin coating show a forming free bipolar resistive switching (BRS) in Pt/GO/ITO structure with high on/off ratio of 10<sup>4</sup> exhibiting good retention and endurance properties at room and elevated temperatures.

#### 2.2. Graphene oxide-based multi-layer structures for high-density data storage

Organic memory devices have gained much attention as future information and storage components owing to their low weight, flexibility, inexpensive and facile fabrication methods [29, 30]. Recent reports have shown that organic memory devices have been developed through layer stacking [31] and using advanced memory architectures [32–35]. However, the most organic memory devices are suffering with slow switching [36] and low storage capacity [37, 38]. RRAM

Figure 4. Raman spectra for Pt/GO/ITO device in LRS (upper curve) and HRS (lower curve) [26].

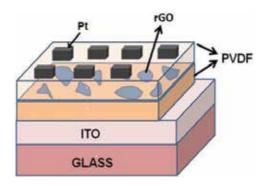

performance of the organic memories can be greatly enhanced by forming hybrid organic structures [39], organic/inorganic composites [40] or by dispersing nanomaterials [41, 42]. Among all other organic polymers, polyvinylidene fluoride (PVDF) was used due to its non-reactive nature, better heat resistance, flexibility and low weight. As mentioned above, hybrid structures of organic memory devices provide enhanced memory characteristics; therefore, heterostructure of PVDF was fabricated using a charge trapping element in it. In this study, reduced graphene oxide nanoflakes (GR) were used as a charge trapping layer owing to their unique chemical structure and exceptional properties [6, 43–47] that make it ideal for charge trapping [48] and storage [49] for memory applications. Also, the defects (vacancy, interstitial sites, etc.) present in GR also work as the charge trapping nodes [50]. Tri-layer structure was fabricated by assembling graphene nanoflakes (GR) between PVDF polymer layers [51] through spin coating process on ITO/glass substrate as shown in **Figure 5**. DC sputtering was used to deposit platinum top electrode having area (100  $\mu$ m × 100  $\mu$ m) through shadow mask to obtain devices from the stacked structure.

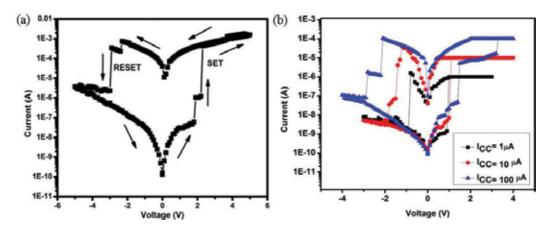

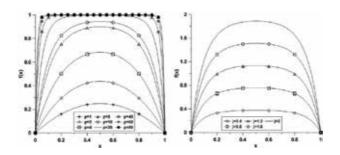

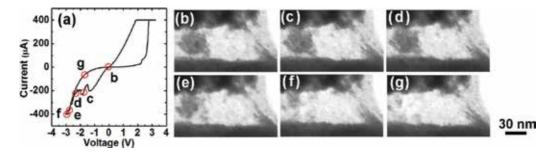

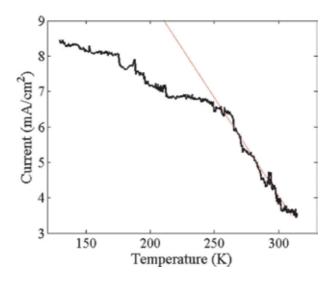

As the voltage was increased, multi-stage SET and RESET were observed in positive and negative polarities, respectively, as shown in Figure 6a. This process was repeatable for a number of cycles, which established the device as a non-volatile memory with multilevel conductance states. The multilevel SET process occurring in the device can be due to multi-channels formation as trapping sites in graphene bear different threshold potentials. Electrons occupied these trapping sites even if the applied voltage is removed, thus preserving the non-volatile nature of the device in ON state. When negative voltage is applied to the device, current firstly increases with voltage due to the presence of trapped charges in the nodes. At a particular negative bias, current jumps to low value due to the de-trapping of electrons from the trapping nodes which initiates the breaking of conducting channels. Further at a particular negative bias, when most of the electrons de-trapped and ejected back to ITO, the conducting path completely disrupts and the device transits to OFF state bearing high resistance. The multi-channel RESET process occurring in the device is also due to the same mechanism as discussed in the SET process. In brief, it may be due to the breaking of multi-channels at different potentials. Reports have shown that the intermediate stage present in the device revealing multi-level switching is due to the formation of multi-filaments [52] having different threshold potentials [53]. The device

**Figure 5.** Schematic diagram of the layer-by-layer fabricated Pt/PVDF/rGO/PVDF/ITO memory devices. Top electrode of platinum (Pt) having area 100 × 100 μm<sup>2</sup> was deposited using DC sputtering [51].

**Figure 6.** Typical I-V characteristic curves plotted in semi-logarithmic scale of Pt/PVDF/rGO/PVDF/ITO device (a) showing the presence of intermediate state. (b) Under different compliance currents of 1, 10 and 100  $\mu$ A showing different low-resistance states corresponding to the compliance current applied [51].

was further subjected to different compliance currents of 1, 10 and 100  $\mu$ A during the SET process and correspondingly obtained different low-resistance states as shown in **Figure 6b**.

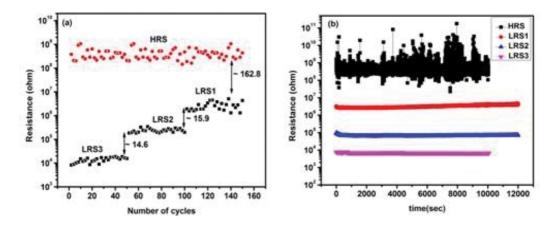

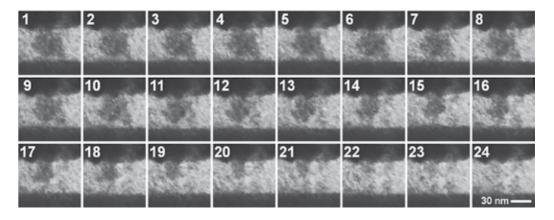

When the highest value of ICC was imposed, the device was observed in lowest resistance state. However, the HRS value for different ICC was almost the same. All four different states including one HRS and three LRS were observed in the device. It was proposed that with the highest compliance current applied during SET process, maximum number of trapping nodes are filled and hence maximum number of conductive channels are formed resulting in the lowest resistance state, while with the application of the lowest compliance current, small number of trapping nodes are filled having less number of conducting channels, leading to higher resistance state. To observe the performance and stability of the memory device, its endurance and retention properties were studied. Figure 7a represents the endurance characteristics of the device for all the four resistance states tested against number of cycles. As can be seen from Figure 7a, the four different states including one HRS and three LRS (LRS1, LRS2 and LRS3) were stable with no overlapping of resistances tested over the 150 number of cycles. Figure 7b shows the retention properties observed in the device where the resistance of all four states were measured using a read voltage of 0.1 V over a period of 10<sup>4</sup> seconds. The graph shows well-differentiated resistance states of HRS and three LRS with no degradation in resistance values over the long time. These measurements for retention and endurance for the device showed that it has well performance and good stability. This tri-layer structure fabricated by simple spin coating method can be seen as a potential candidate for future memory devices qualifying the need for high-density storage media.

#### 2.3. Graphene oxide composite with ZnO nanorods for flexible memory devices

Flexible RRAM devices have shown good potential for bendable memory systems [54–58]. These memories are in much demand due to the qualities of inexpensive, low weight, portability and user-friendly interfaces over conventional rigid silicon technology [59]. The substrates for flexible memories could not bear high temperatures used in growth techniques, this limitation

Figure 7. Resistances of the device in all LRS and HRS under different compliance currents of 1, 10 and 100  $\mu$ A with read voltage of 0.1 V. (a) Endurance properties over 150 cycles with enough margin between the states. (b) Retention characteristics over 10<sup>4</sup> seconds for all four states [51].

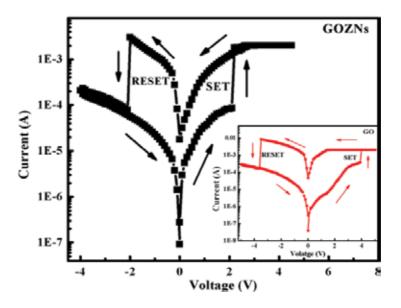

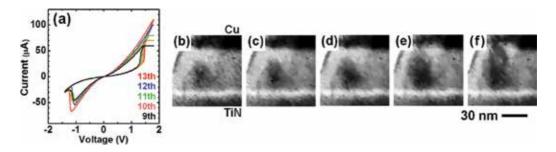

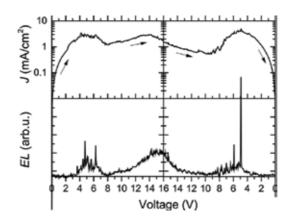

demands for the need for materials which can be grown on these substrates at room temperature. Obeying this condition, GO is readily oxidizable and water soluble, which qualifies to be fabricated in thin films on flexible substrates at room/moderate temperatures. There are reports which have shown that integration of nanomaterials into oxides is helpful in enhancing the resistive switching properties of the devices [60-62]. In this work [63], ZnO nanorods (ZNs) were grown in horizontal direction on GO sheets to maximize the contact area between the nanorods and GO sheets [64, 65]. The consequence of this was observed in significant reduction in switching voltages in comparison to GO alone. The solution of GOZNs was spin coated to ITO-coated polyethylene terephthalate (indium-tin oxide on polyester film (ITOPET)) substrates to fabricate the films. Initially, the Al/GOZNs/ITOPET devices were in high-resistance state (HRS). In the very first cycle, a forming voltage around 5 V with current compliance of 2 mA was applied to activate these devices. Device showed SET and RESET processes on positive and negative voltages having non-volatile nature. To investigate the effect of ZNs addition into the GO matrix, another device Al/GO/ITOPET was fabricated following the same process except the incorporation of ZNs in it, and this device showed comparatively higher values of SET and RESET voltages.

I-V measurements performed on both devices, shown in **Figure 8**, have clearly shown that SET and RESET voltages in the device containing ZNs were severely reduced to approximately half in comparison to the device containing no ZNs. To further understand the effect of changing ZNs ratio in GO matrix on resistive switching, the I-V characteristics of different compositions (10:1, 5:1, 3:1 and 2:1) were studied and found that 3:1 was the best among all. In Al/GOZNs/ITOPET devices, we propose that the conducting filament formation during the SET process is due to the oxygen vacancies. Oxygen concentration gradient exists at the interface of GO, and Al has high oxidation tendency. Therefore, oxygen ions from GO move towards and react with Al forming a new interfacial Al oxide layer [66]; also this process induces the oxygen vacancies into the GO region. With the positive bias is applied to the top electrode, these induced oxygen vacancies are deeply inserted into the GO matrix and providing the conductive paths during the SET process. With the negative polarity these oxygen vacancies are pushed back resulting

Figure 8. Typical I-V switching characteristics in Al/GOZNs/ITOPET devices. Inset shows the I-V characteristics for Al/GO/ITOPET device [63].

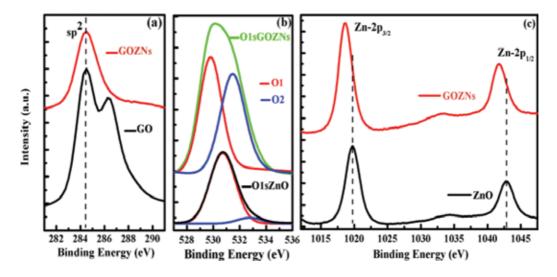

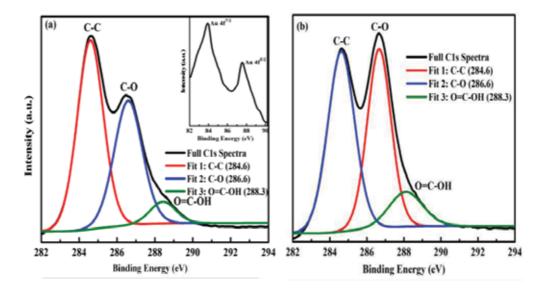

in rupture of the conducting channel during the RESET process. But with the incorporation of ZNs into the GO matrix, significant reduction in the switching voltages was observed and this is due to the desorption/adsorption of oxygen at the interface of GO and ZNs, which stimulates the formation/rupture of conducting paths on the application of suitable polarity voltages. This mechanism based on oxygen vacancies is well supported by the X-ray photoemission spectroscopy (XPS) measurements of these samples shown in **Figure 9**.

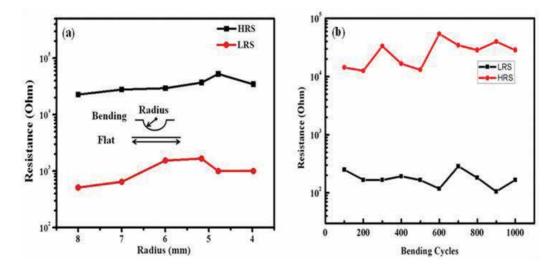

Figure 9a is the XPS graph for C1s peak in GO and GOZNs samples. The C1s graph of GO contains sp<sup>2</sup> and C–O–C peaks, whereas for the GOZNs sample, the C–O–C peak has disappeared having only sp<sup>2</sup> peak in the spectra. The XPS study showed the reduction in oxygen content with the disappeared C–O–C peak for the GO matrix having ZNs, which demonstrates that GO has become comparatively less resistive having sp<sup>2</sup> character dominant. However, ZNs are well known for chemisorption of oxygen at its periphery and it can be evidenced by the fitted O2 peak for O1s spectra in Figure 9b. Also, the peak positions for these O1 and O2 in GOZNs sample were found to be little shifted towards lower energy. Furthermore, a noticeable increment in the intensity of O2 peak was also observed in GOZNs in comparison to ZNs. The O1s peak was also found to be shifted to lower binding energy due to the additional oxygen absorbed by ZNs as shown in Figure 9b [67]. Further, the presence of excess oxygen can also be clearly observed in Figure 9c which shows the shift in the Zn 2p peak towards lower energy in GOZNs sample in comparison to ZNs sample [67]. The performance of flexible electronic devices can be tested through flexibility and mechanical endurance measurements. The flexibility measurements were done on the Al/GOZNs/ITOPET devices and the value of resistance was plotted as a function of bending radii as shown in Figure 10a. The resistance was measured up to the maximum bending radius of 4 mm and amazingly found that the LRS and HRS were widely separated and can be well distinguished. The mechanical

Figure 9. (a) Comparative XPS spectra of GO and GOZNs for C1S peak. (b) XPS spectra of ZNs and GOZNs showing O1S peak resolved into two components O1 and O2. (c) Zn2p spectra of ZNs and GOZNs samples [63].

reliability test was also performed by constantly flexing the device many times to the bending radius of 6 mm and the resistance was plotted against number of bending cycles as shown in **Figure 10b**. The HRS and LRS resistances show no noticeable degradation even up to 1000 times of repeated bending. The measurements performed on the Al/GOZNs/ITOPET device show excellent flexibility and mechanical endurance results and provide the data which show that the devices are capable for flexible memory applications. This study shows that the devices based on ZNs embedded in GO are potential candidate for future flexible non-volatile memory applications.

Figure 10. (a) Flexibility test for various bending radius on Al/GOZNs/ITOPET RRAM device. (b) Mechanical bending endurance of device at bending radius of 6 mm on Al/GOZNs/ITOPET RRAM device [63].

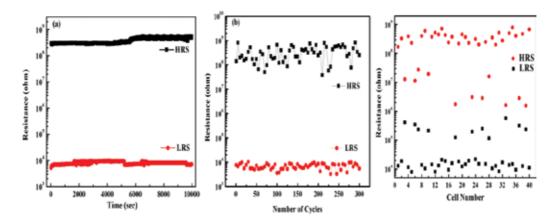

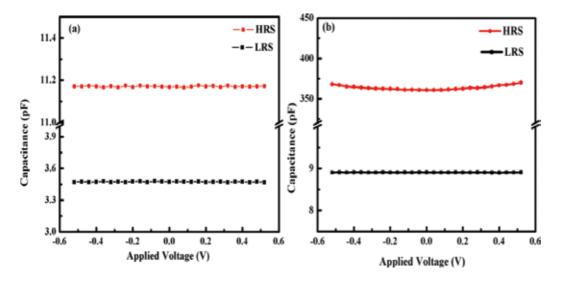

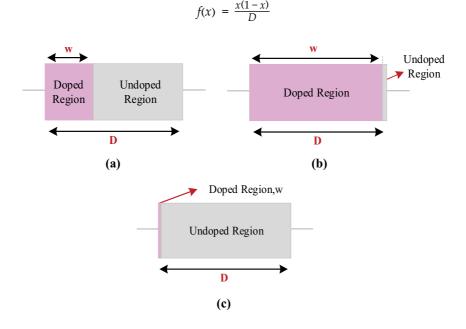

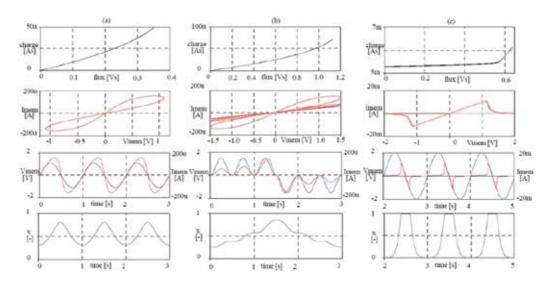

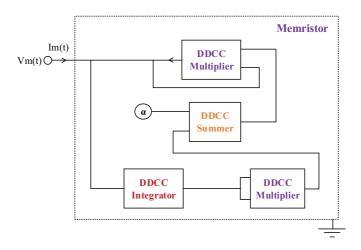

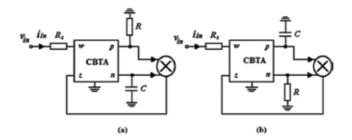

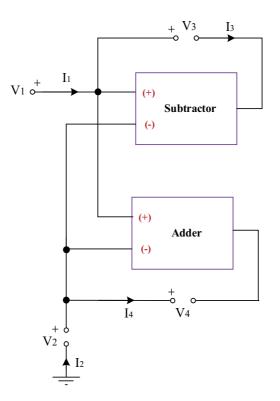

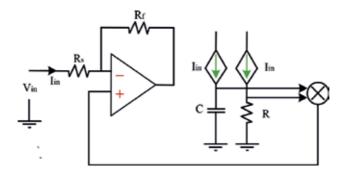

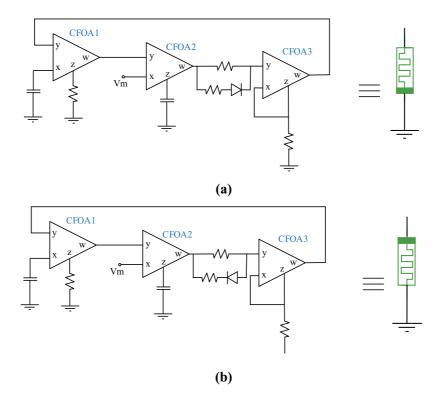

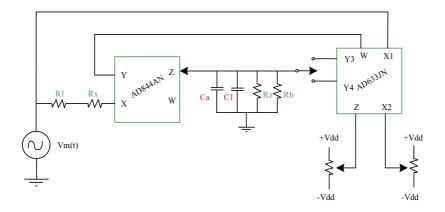

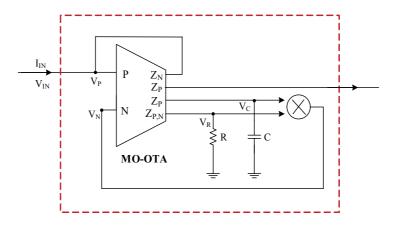

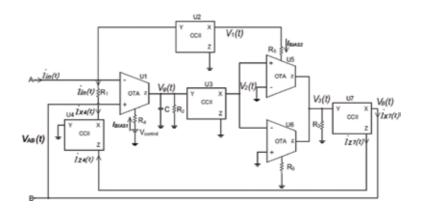

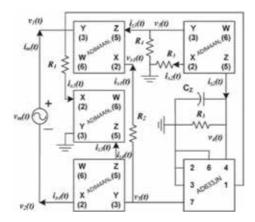

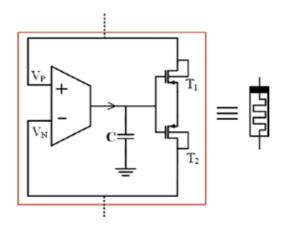

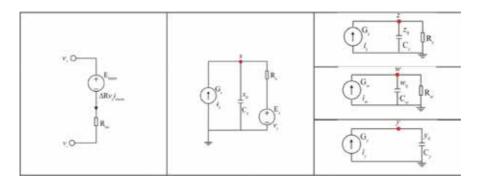

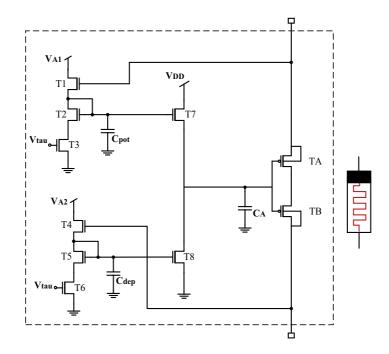

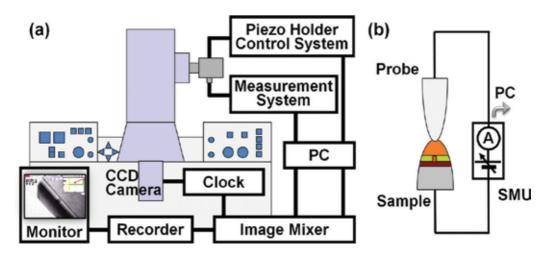

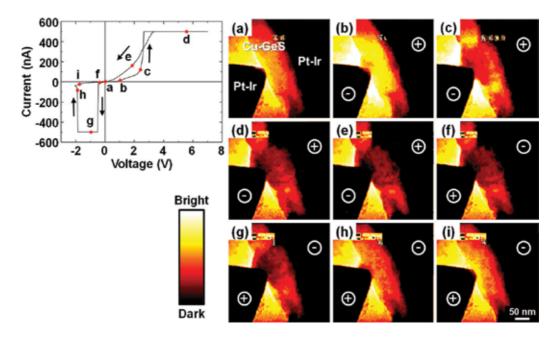

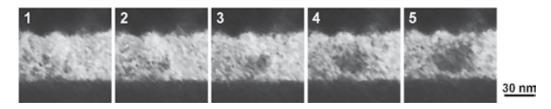

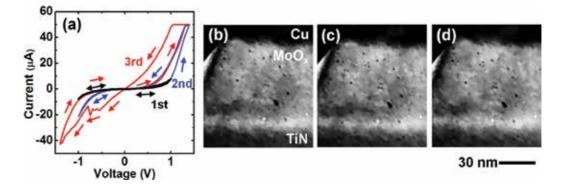

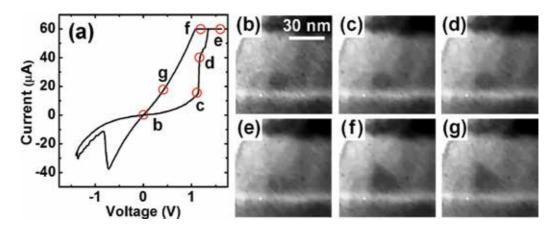

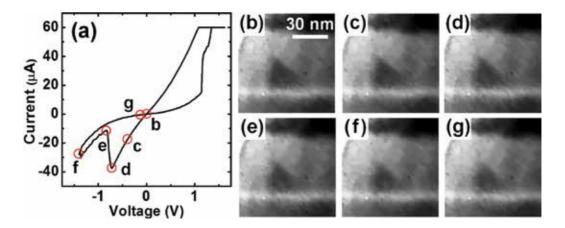

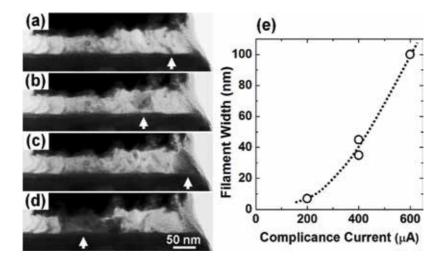

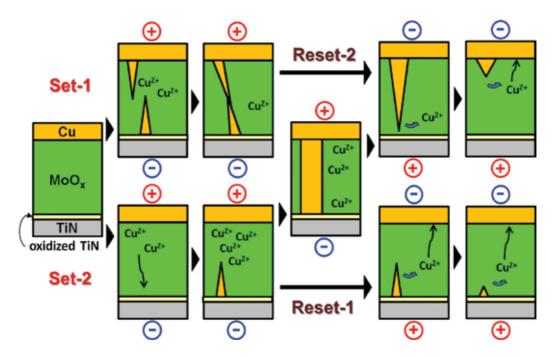

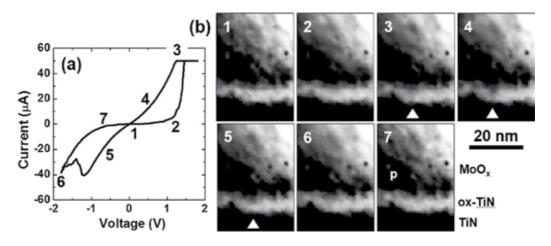

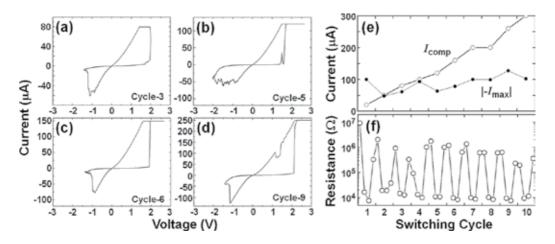

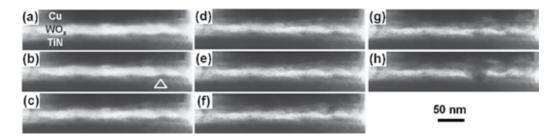

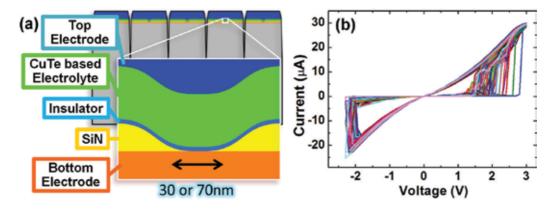

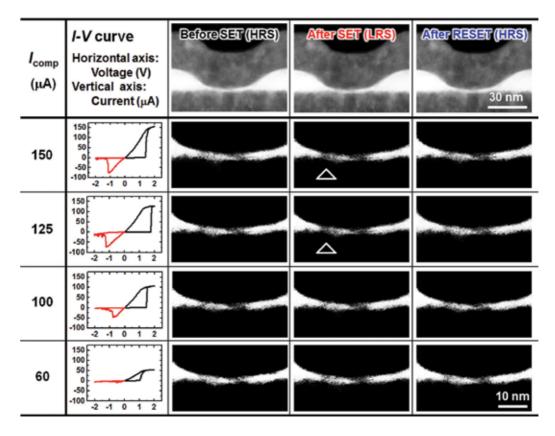

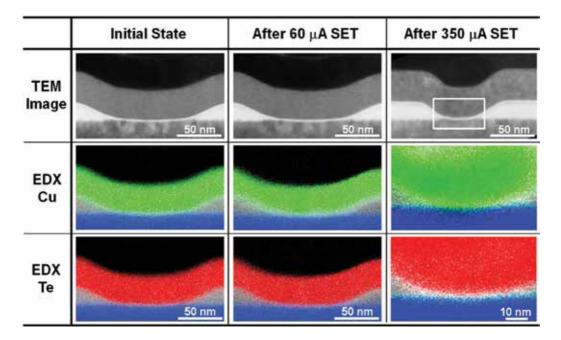

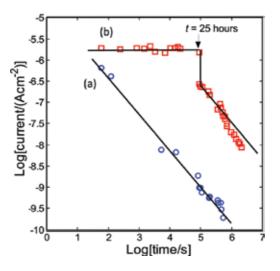

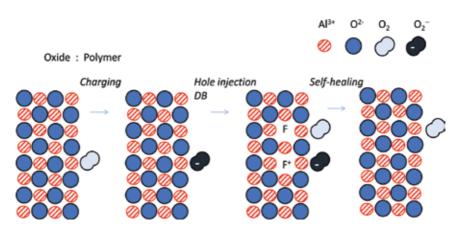

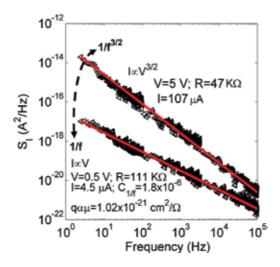

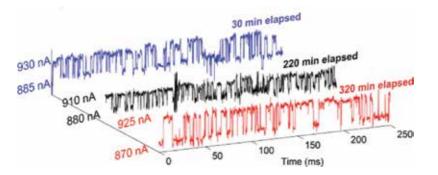

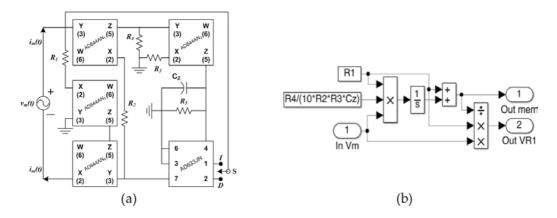

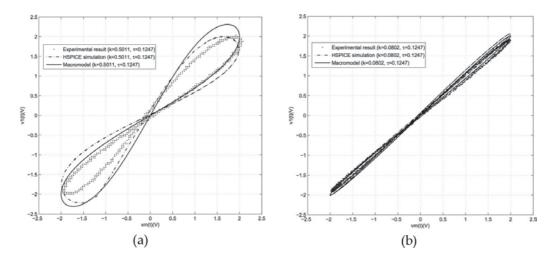

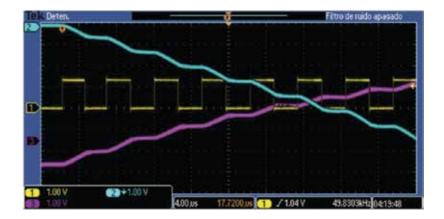

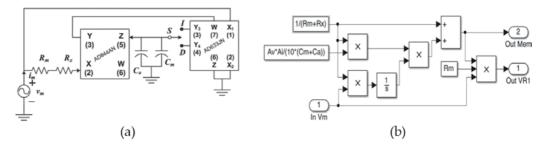

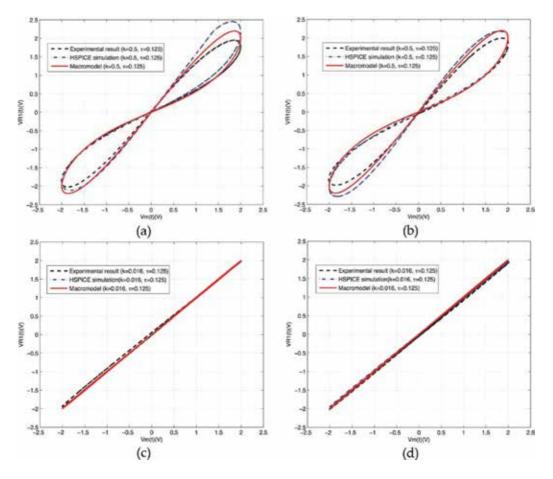

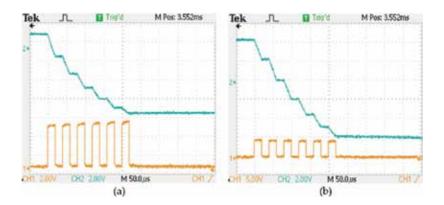

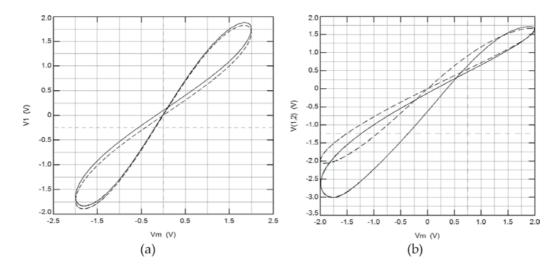

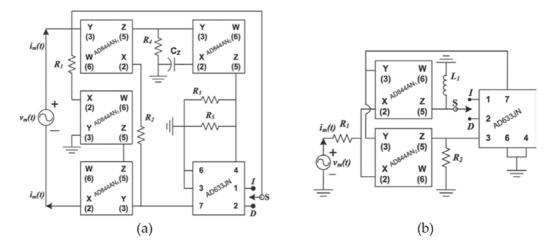

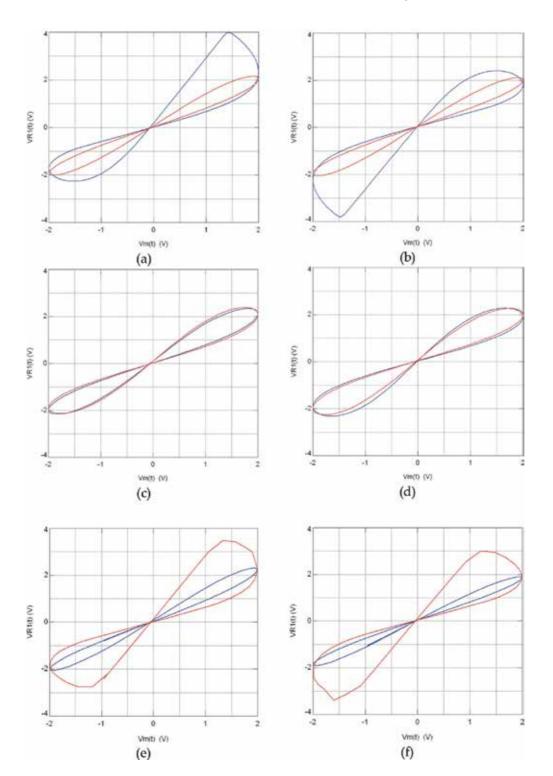

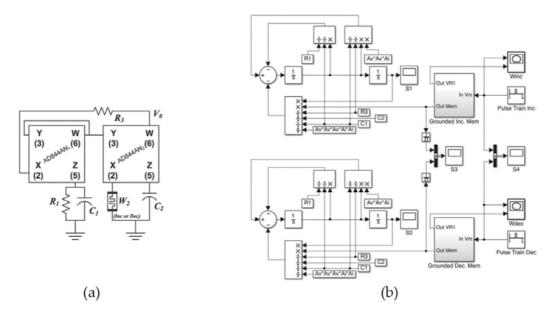

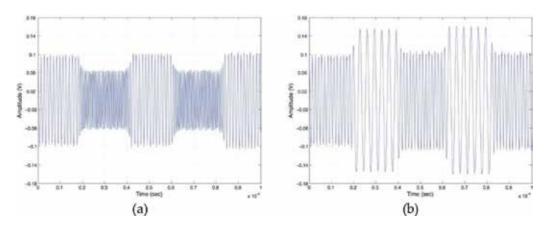

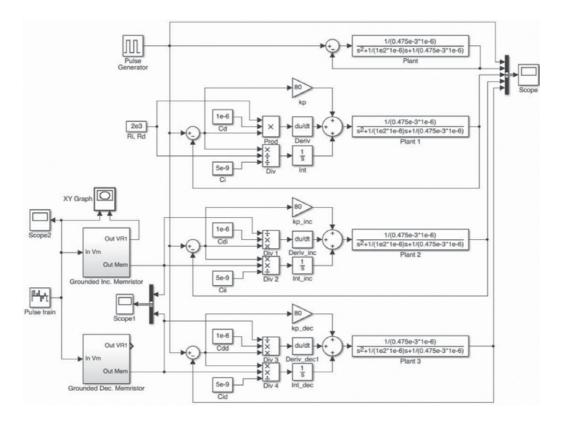

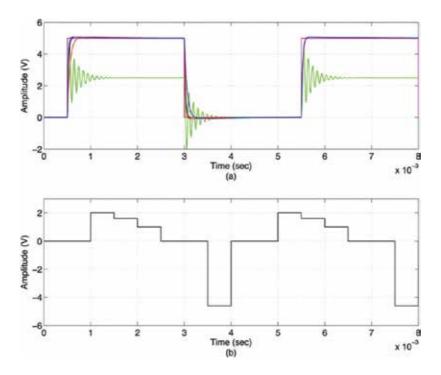

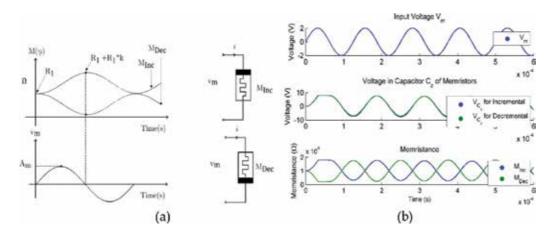

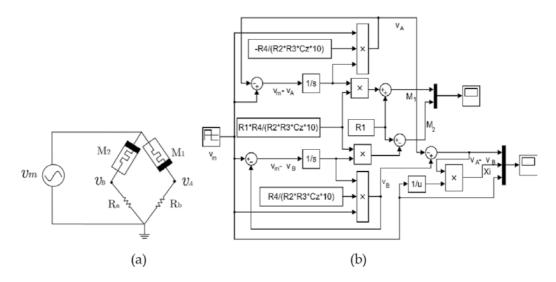

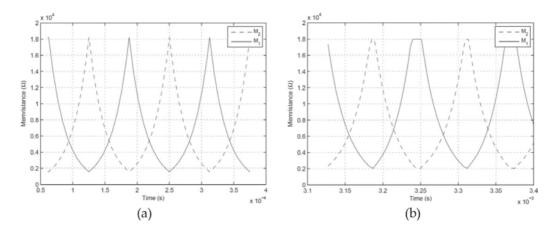

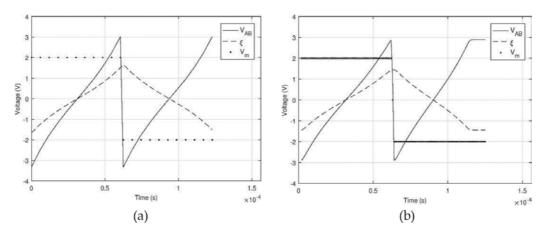

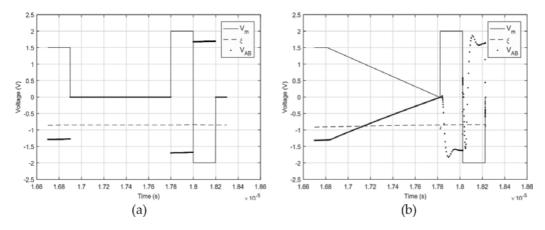

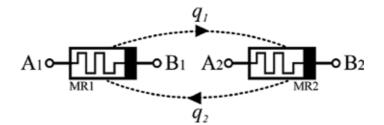

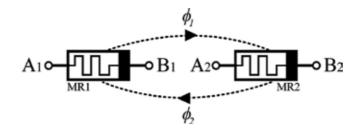

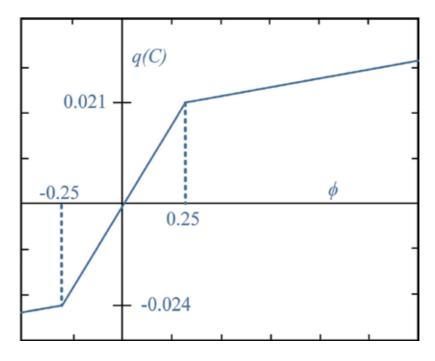

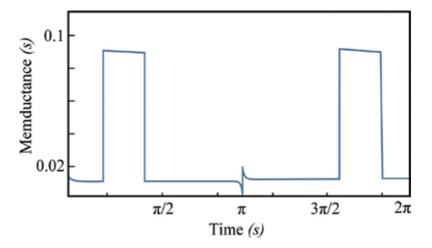

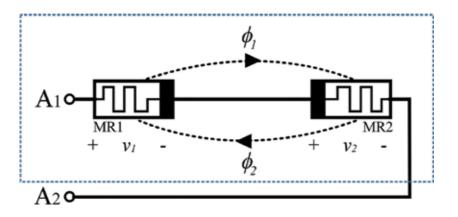

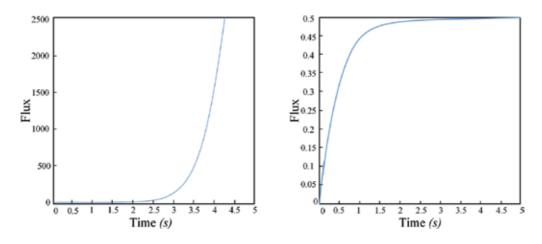

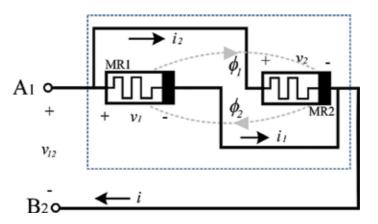

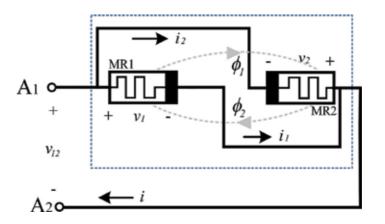

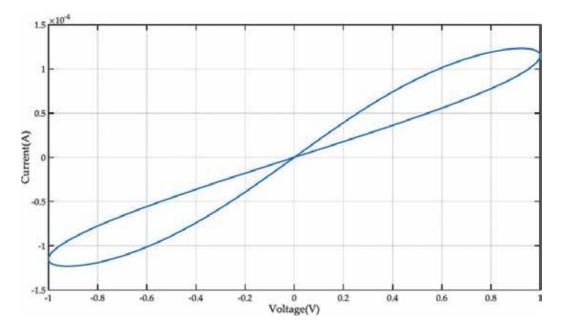

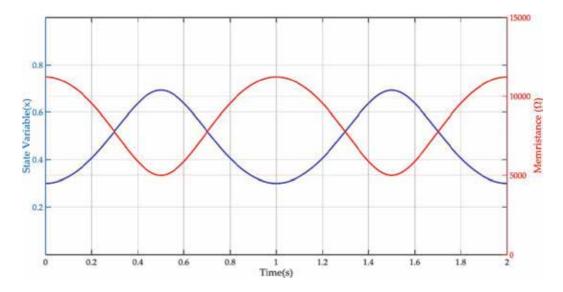

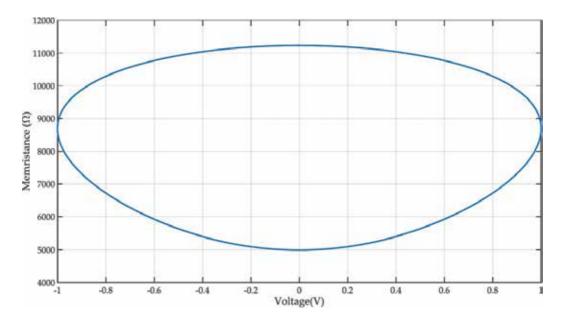

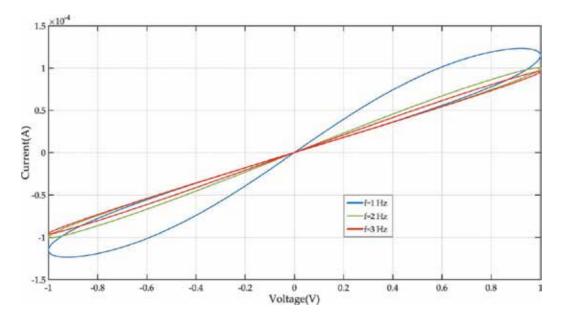

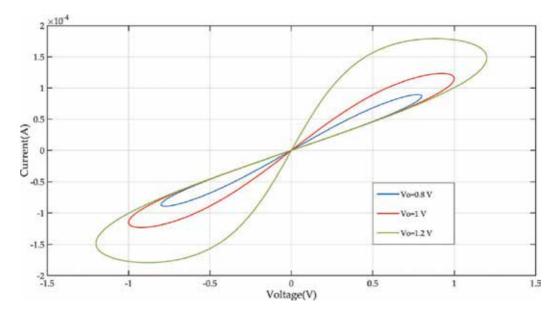

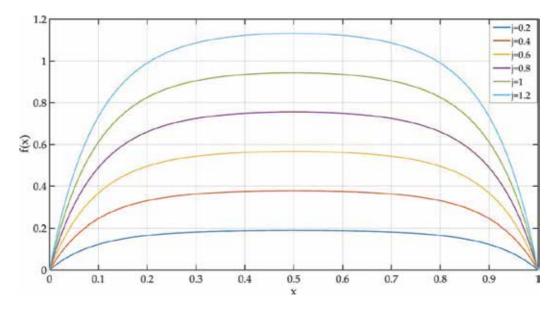

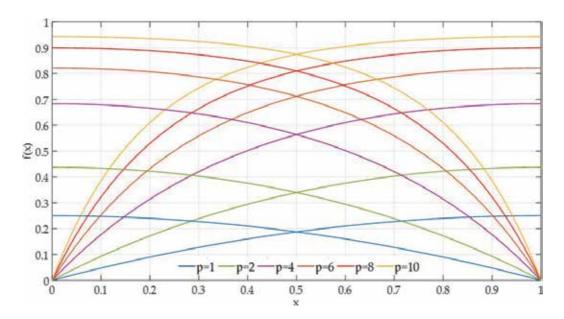

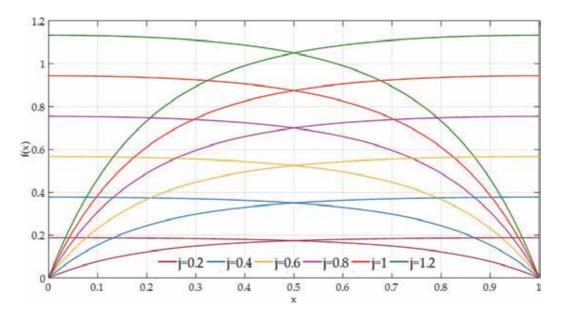

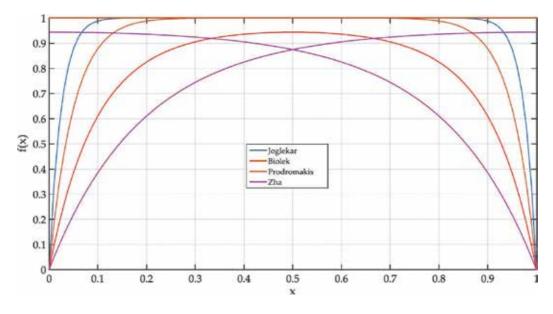

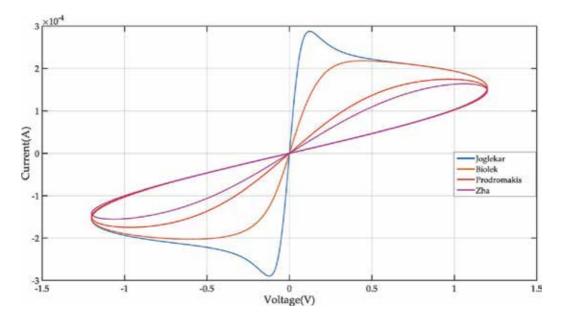

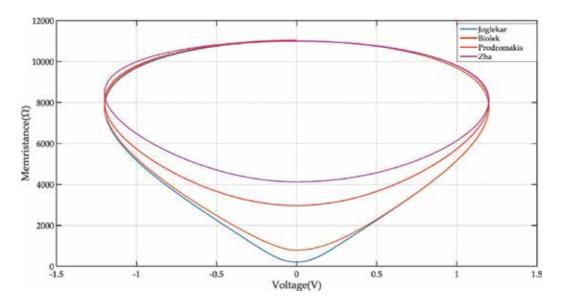

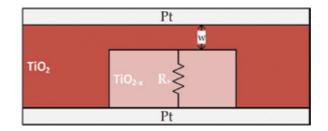

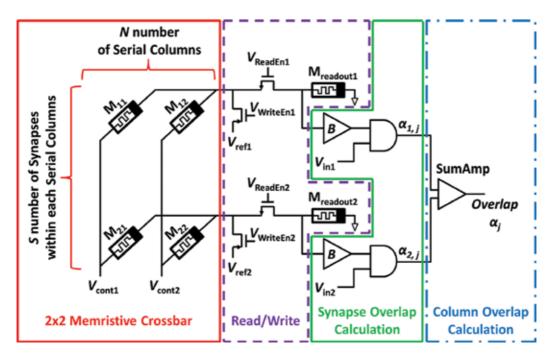

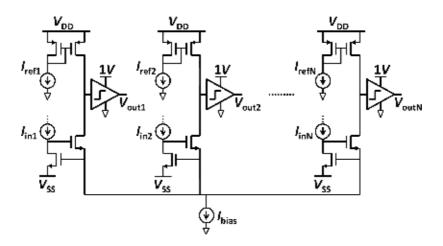

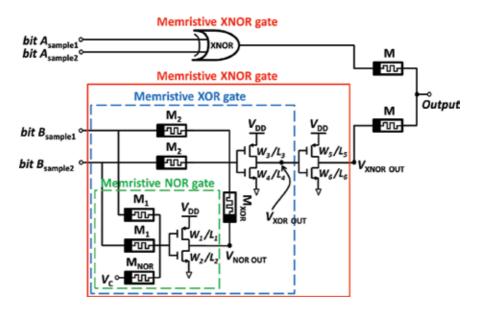

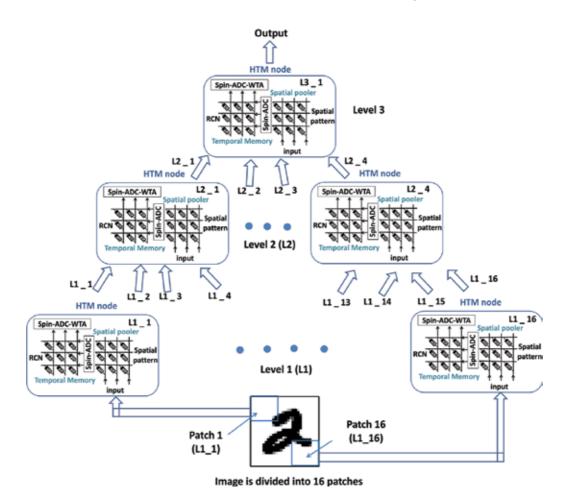

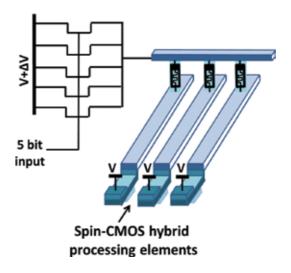

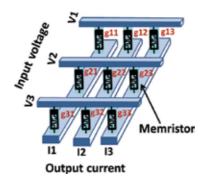

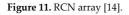

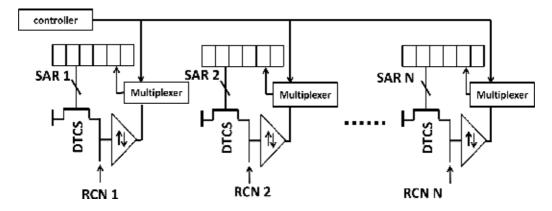

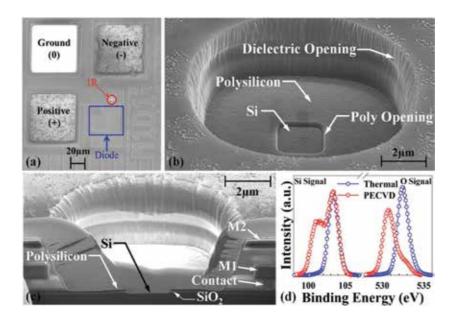

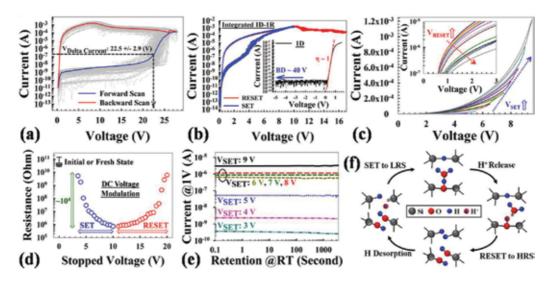

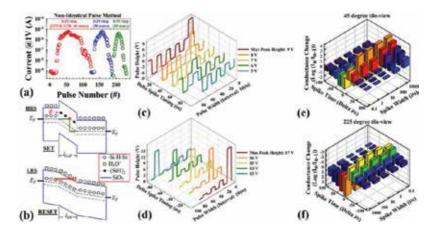

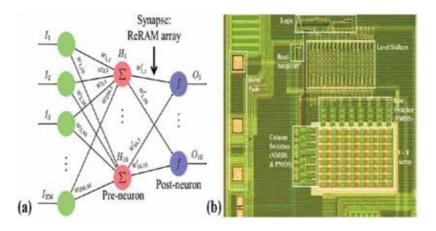

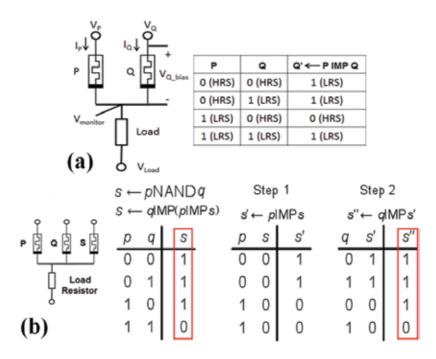

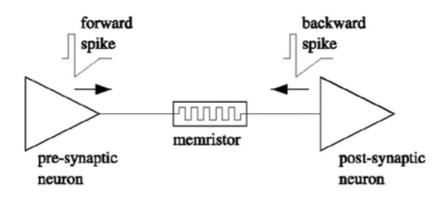

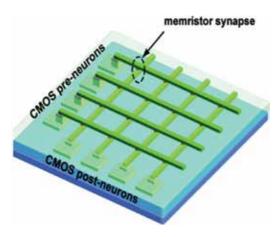

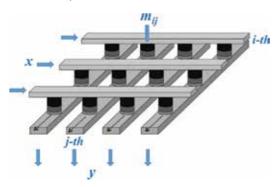

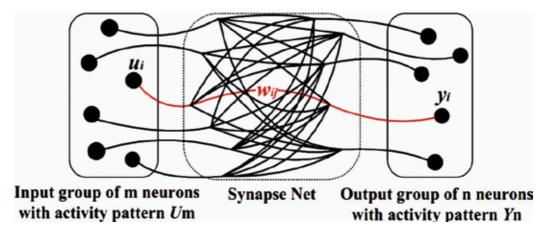

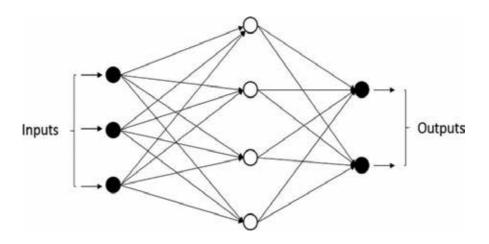

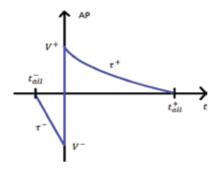

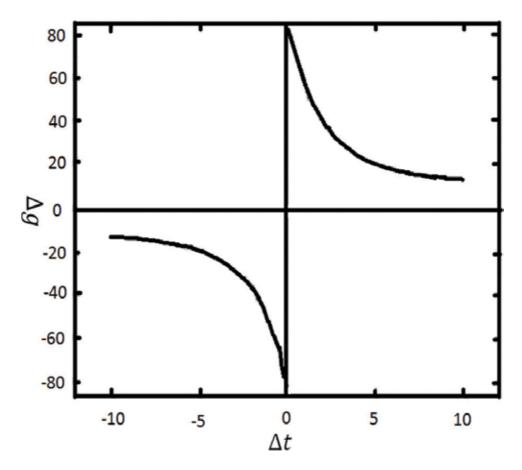

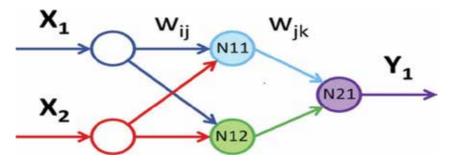

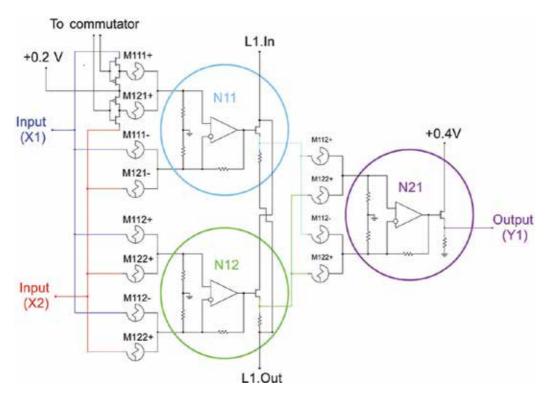

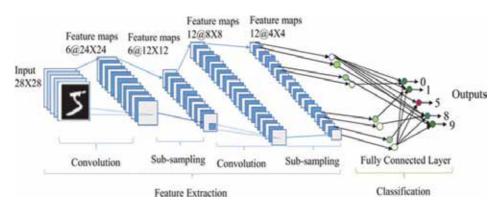

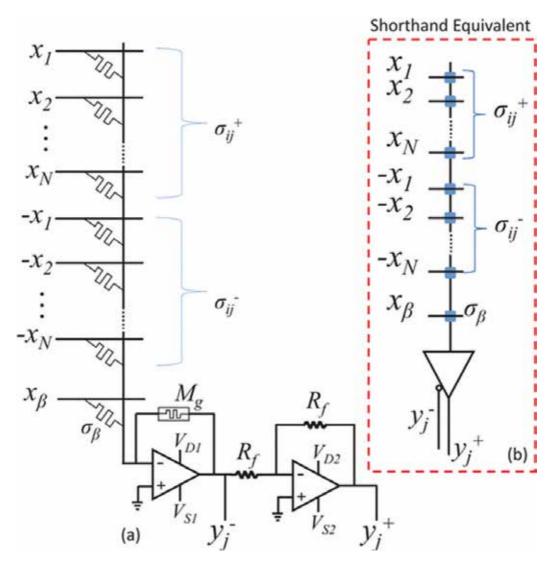

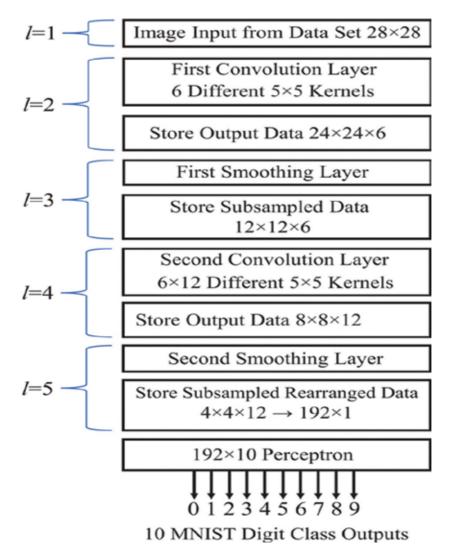

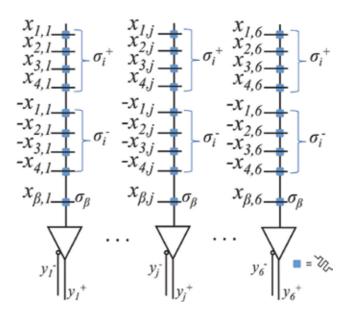

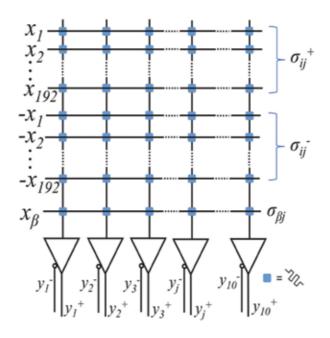

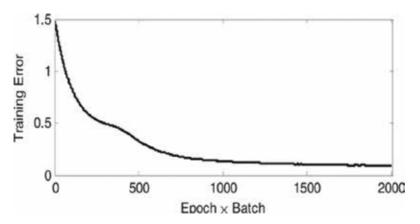

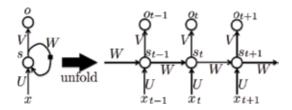

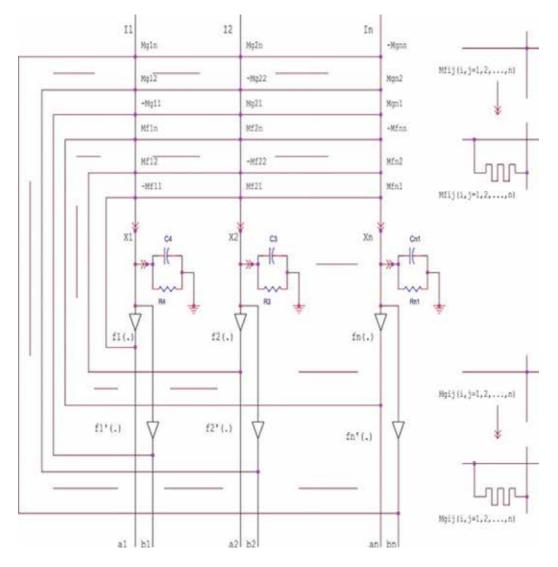

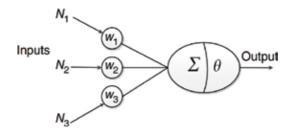

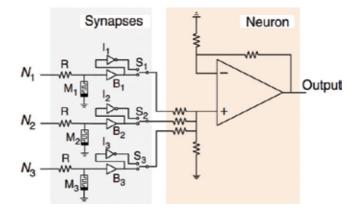

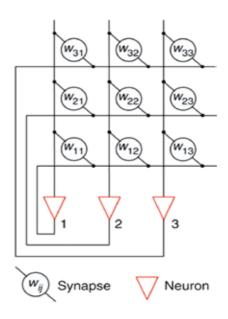

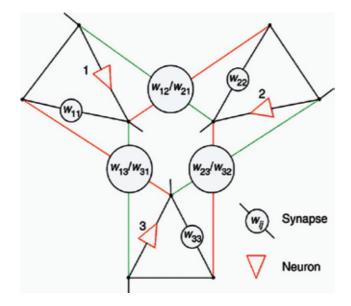

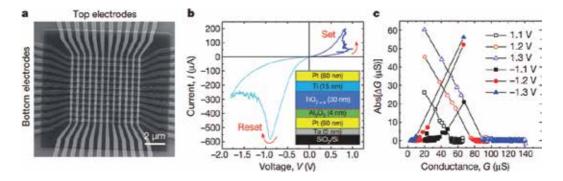

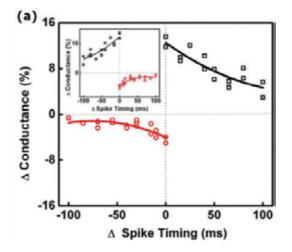

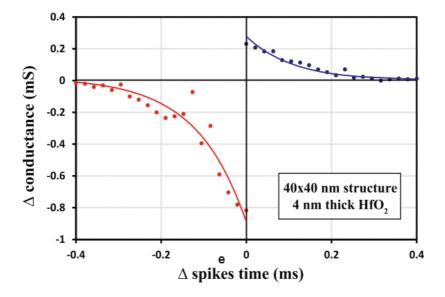

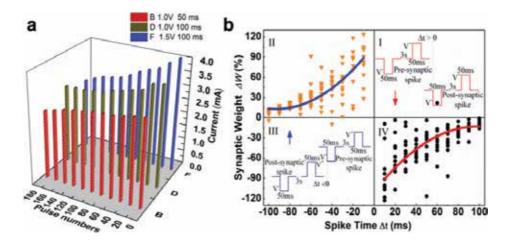

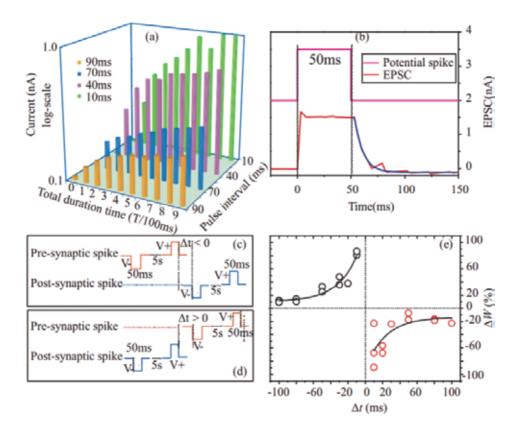

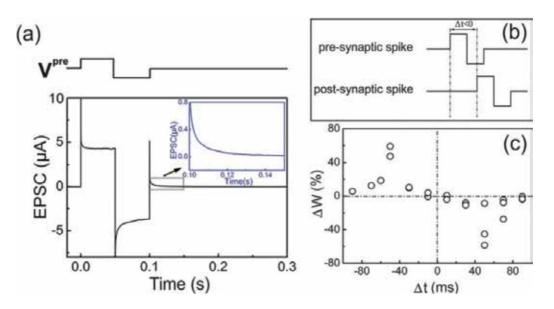

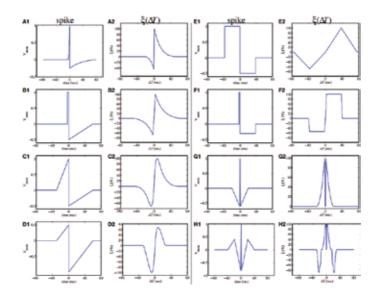

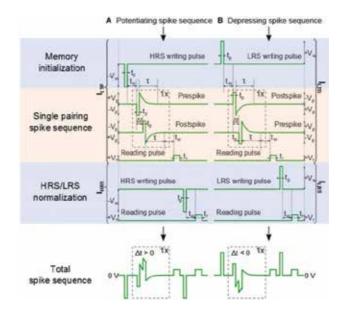

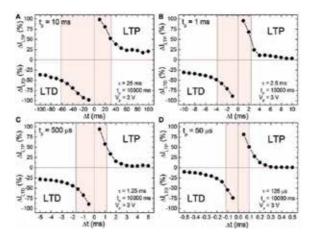

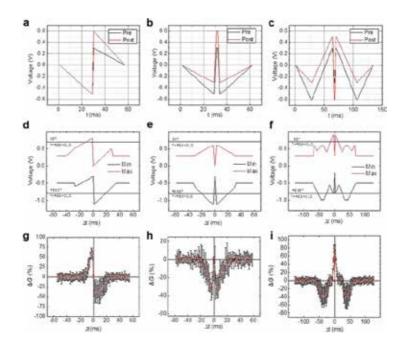

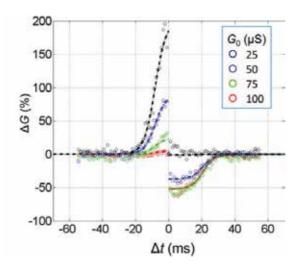

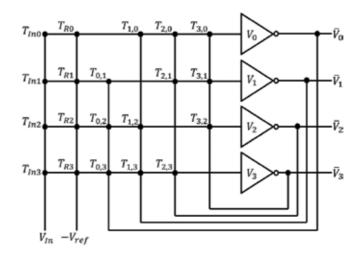

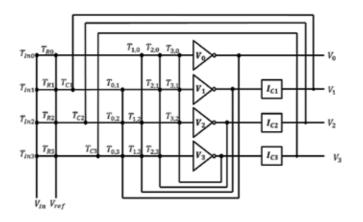

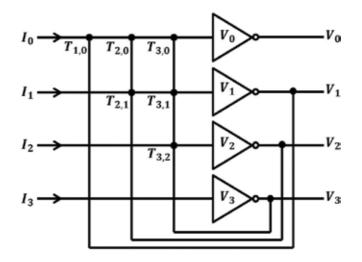

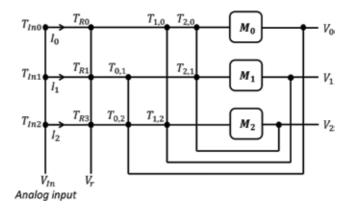

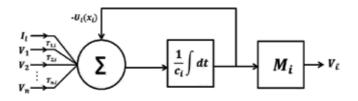

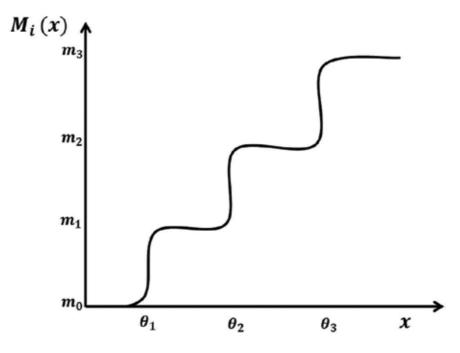

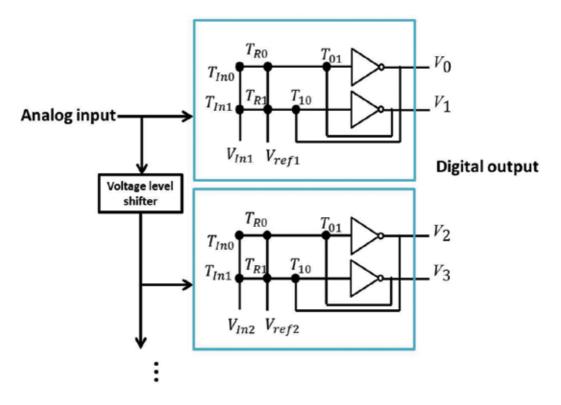

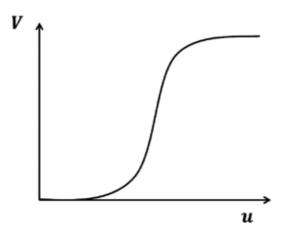

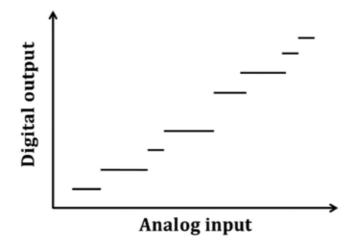

# 2.4. Nanoparticles embedded graphene oxide RRAM devices for low operating voltages and high on/off ratio