# IntechOpen

# Very-Large-Scale Integration

Edited by Kim Ho Yeap and Humaira Nisar

# VERY-LARGE-SCALE INTEGRATION

Edited by Kim Ho Yeap and Humaira Nisar

#### Very-Large-Scale Integration

http://dx.doi.org/10.5772/65525 Edited by Kim Ho Yeap and Humaira Nisar

#### Contributors

Kim Ho Yeap, Ian Andrew Grout, Muhaned Zaidi, Abu Khari A'Ain, Vadim Glebovsky, Kittipong Tripetch, Changyeol Lee, Vithyalakshmi N, Ashok Kumar N, Nagarajan P, Vinoth G.S

#### © The Editor(s) and the Author(s) 2018

The moral rights of the and the author(s) have been asserted.

All rights to the book as a whole are reserved by INTECH. The book as a whole (compilation) cannot be reproduced, distributed or used for commercial or non-commercial purposes without INTECH's written permission. Enquiries concerning the use of the book should be directed to INTECH rights and permissions department (permissions@intechopen.com).

Violations are liable to prosecution under the governing Copyright Law.

### CC BY

Individual chapters of this publication are distributed under the terms of the Creative Commons Attribution 3.0 Unported License which permits commercial use, distribution and reproduction of the individual chapters, provided the original author(s) and source publication are appropriately acknowledged. If so indicated, certain images may not be included under the Creative Commons license. In such cases users will need to obtain permission from the license holder to reproduce the material. More details and guidelines concerning content reuse and adaptation can be foundat http://www.intechopen.com/copyright-policy.html.

#### Notice

Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published chapters. The publisher assumes no responsibility for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained in the book.

First published in Croatia, 2018 by INTECH d.o.o. eBook (PDF) Published by IN TECH d.o.o. Place and year of publication of eBook (PDF): Rijeka, 2019. IntechOpen is the global imprint of IN TECH d.o.o. Printed in Croatia

Legal deposit, Croatia: National and University Library in Zagreb

Additional hard and PDF copies can be obtained from orders@intechopen.com

Very-Large-Scale Integration Edited by Kim Ho Yeap and Humaira Nisar p. cm. Print ISBN 978-953-51-3863-1 Online ISBN 978-953-51-3864-8 eBook (PDF) ISBN 978-953-51-3978-2

# We are IntechOpen, the first native scientific publisher of Open Access books

<u>3.300</u>+ Open access books available <u>107,000+</u> 114M+

International authors and editors

Downloads

15Countries delivered to Our authors are among the

lop 1% most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science<sup>™</sup> Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# Meet the editors

Kim Ho Yeap is an Associate Professor at Universiti Tunku Abdul Rahman, Malaysia. He is an IEEE senior member and a chartered engineer registered with the UK Engineering Council. He received his MSc degree in microelectronics from Universiti Kebangsaan Malaysia in 2005 and his PhD degree from Universiti Tunku Abdul Rahman in 2011. In 2008 and 2015, respectively,

he underwent research attachment in the University of Oxford (UK) and Nippon Institute of Technology (Japan). He is the external examiner of Wawasan Open University. He is also the editor in chief of the i-manager's Journal on Digital Signal Processing. He has also been a guest editor for the Journal of Applied Environmental and Biological Sciences and Journal of Fundamental and Applied Sciences. When working in Intel Corporation, he was involved in the design of the Pentium IV PSC and Celeron NWD-V microprocessors. This earned him four Kudos awards from Intel Microelectronics. He has also been given the university teaching excellence award and 16 research grants. He has published close to 100 scientific articles, which include refereed journal and conference papers, books and book chapters.

Humaira Nisar has a BS degree in Electrical Engineering from the University of Engineering and Technology, Lahore, Pakistan; MS degree in Nuclear Engineering from Quaid-i-Azam University, Islamabad, Pakistan; and another MS degree in Mechatronics and PhD degree in Information and Mechatronics from Gwangju Institute of Science and Technology, Gwangju, South Korea. She

has more than 15 years of research experience. Currently, she is working as an Associate Professor in the Department of Electronic Engineering, Universiti Tunku Abdul Rahman, Malaysia. She is also the head of Programme for the Master of Engineering Science Programme. She is a senior member of IEEE. Her research interests include signal and image processing, biomedical imaging, brain signal and image analysis and image analysis for wastewater treatment. She has published a number of international journal and conference papers. She has also served on technical committees of various conferences and journals.

# Contents

## **Preface XI**

- Introduction 1 Section 1 Chapter 1 Introductory Chapter: VLSI 3 Kim Ho Yeap and Humaira Nisar Section 2 Physics of MOSFET's 13 Chapter 2 Transistor Degradations in Very Large-Scale-Integrated CMOS **Technologies 15** Chang Yeol Lee Section 3 IC Design and Fabrication 45 Chapter 3 Low Power Design Methodology 47 Vithyalakshmi Natarajan, Ashok Kumar Nagarajan, Nagarajan Pandian and Vinoth Gopi Savithri Chapter 4 **High-purity Refractory Metals for Thin Film** Metallization of VLSI 67 Vadim Glebovsky Section 4 Applications 111

- Chapter 5 Operational Amplifier Design in CMOS at Low-Voltage for Sensor Input Front-End Circuits in VLSI Devices 113 Muhaned Zaidi, Ian Grout and Abu Khari A'ain

- Chapter 6 Design of High-Order CMOS Analog Notch Filter with 0.18 μm CMOS Technology 135 Kittipong Tripetch

# Preface

In this book, a variety of topics related to Very-Large-Scale Integration (VLSI) is extensively discussed. The topics encompass the physics of VLSI transistors, the process of integrated circuit (IC) design and fabrication and the applications of VLSI devices. The book is intended to provide information on the latest advancement of VLSI technology to researchers, physicists as well as engineers working in the field of semiconductor manufacturing and VLSI design.

Chapter 1 gives an overview of VLSI-integrated circuit devices. A brief historical development of the transistor and integrated circuits is first presented. This is then followed by an introduction of the field effect transistors and of the technology progression driven by Moore's law, which necessitates the evolution of MOSFETs to FinFETs. A concise walkthrough of the VLSI manufacturing process—from design to fabrication and finally to packaging—is also illustrated at the end of the chapter.

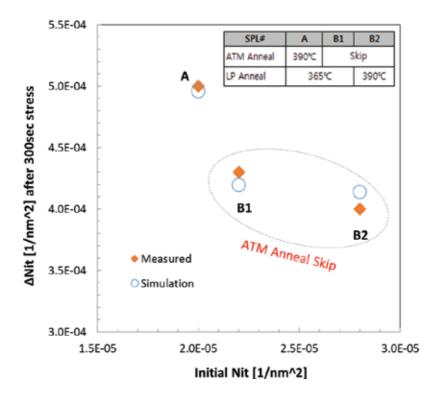

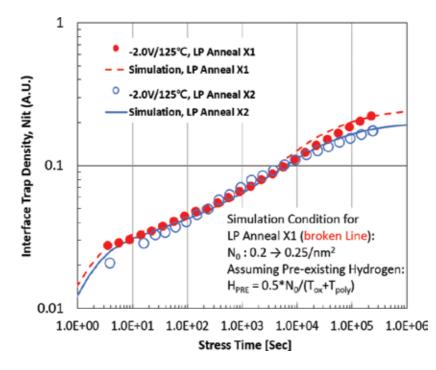

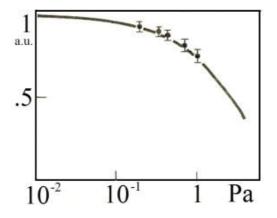

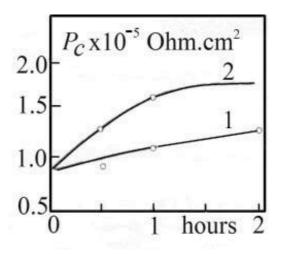

In Chapter 2, the historical evolution of the hot carrier degradation mechanisms and their physical models are reviewed. An energy-driven hot carrier ageing model that can reproduce the 62-nm-gate-long hot carrier degradation of the transistor is verified. A long-term hot carrier-resistant circuit design can be realized via optimal driver strength controls. The central role of the  $V_{GS}$  ratio is emphasized during practical case studies on CMOS inverter chains and a DRAM word line circuit. Negative bias temperature instability (NBTI) mechanisms are also reviewed and implemented in a hydrogen reaction-diffusion (R-D) framework. The R-D simulation reproduces time-dependent NBTI degradations interpreted into interface trap generation, , with a proper power-law dependency on time. The experimental evidence of pre-existing hydrogen-induced Si-H bond breakage is also proven by the quantifying R-D simulation. The analysis shows that a low-pressure EOL anneal can reduce the saturation level of NBTI degradation, which is believed to be caused by the outward diffusion of hydrogen from the gate regions. It therefore prevents further breakage of Si-H bonds in the silicon-oxide interfaces.

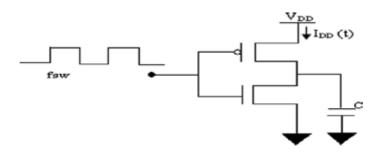

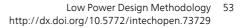

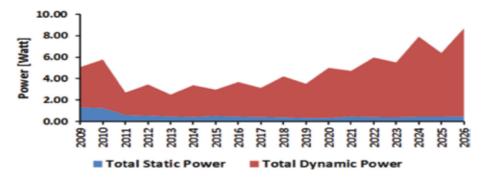

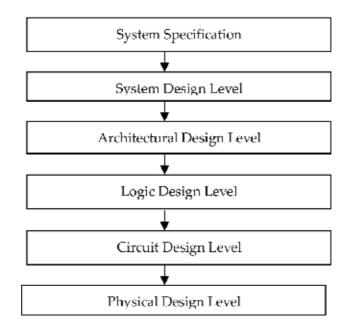

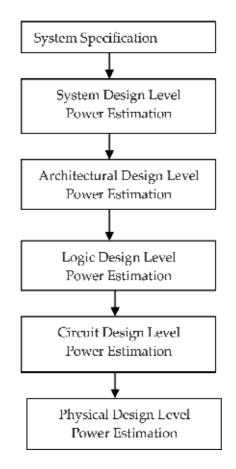

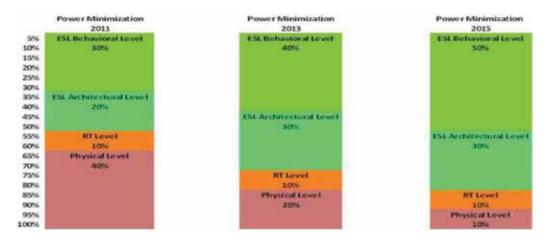

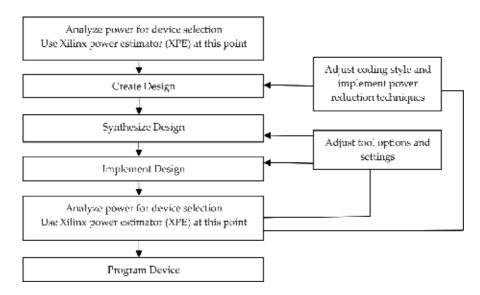

As VLSI technology advances, power consumption in a chip becomes an essential factor, which must be accounted for during IC design. Hence, power optimization is necessary at all levels of the design process. Chapter 3 looks into various design methodologies that could be applied to achieve the concept of low-power designs.

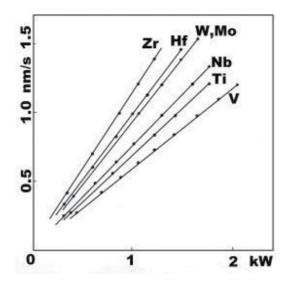

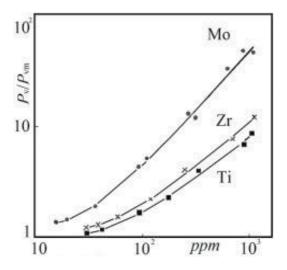

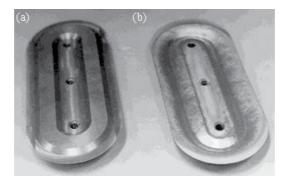

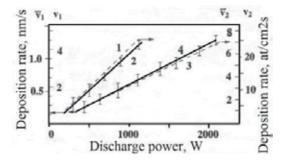

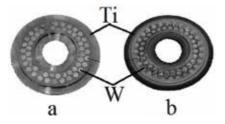

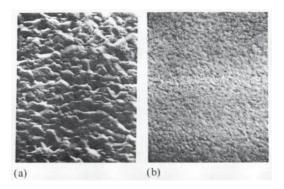

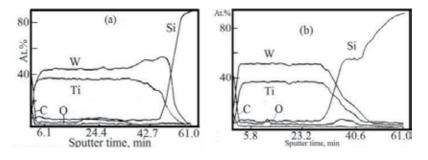

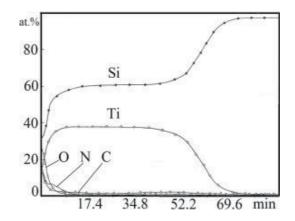

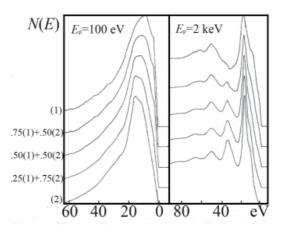

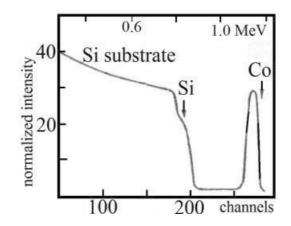

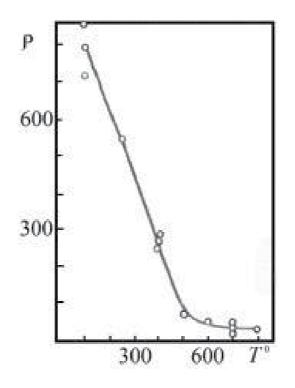

Chapter 4 discusses in detail highly pure refractory metals, which are used in VLSI thin-film metallization. Cast targets of highly pure refractory metals, such as W, Mo, Ti, Ta, Co, etc., and their compounds can be produced by means of a set of vacuum metallurgical techniques, i.e., vacuum high-frequency levitation, EB floating zone melting, EB melting and electric arc vacuum melting, as well as chemical purifying by ion exchange and halides. The cast

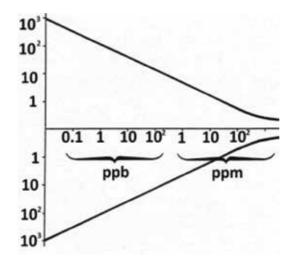

refractory metal targets are extremely pure and chemically homogeneous. For magnetron sputtering and laser ablation, the cast silicide targets are produced. The study reveals the possibilities and conditions of depositing the silicides and titanium-tungsten barrier layers by both laser evaporation and magnetron sputtering. The physical and structural parameters as well as a trace impurity composition of sputtered metals and deposited thin films are studied by grazing-beam incidence X-ray diffraction, Auger electron spectroscopy, Rutherford backscattering of helium ions, mass spectrometry with inductively coupled plasma, etc.

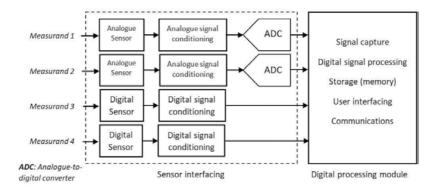

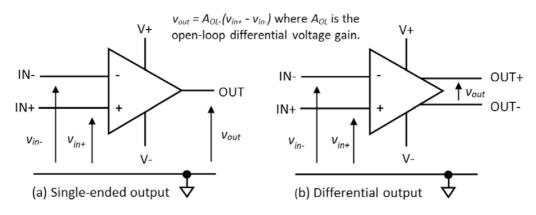

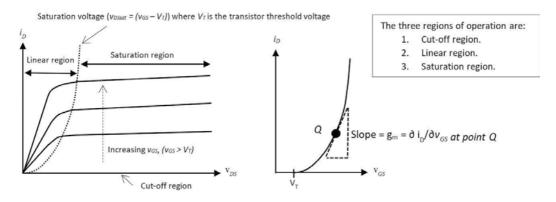

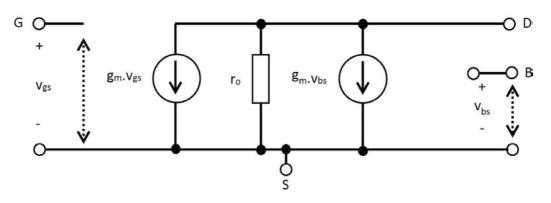

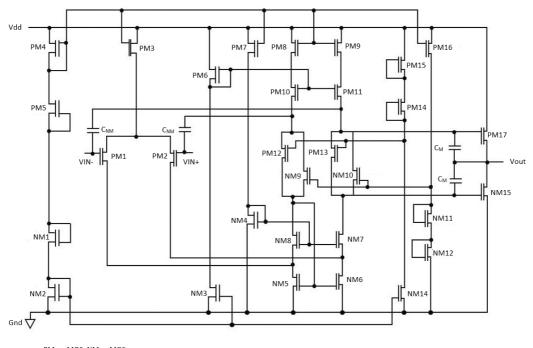

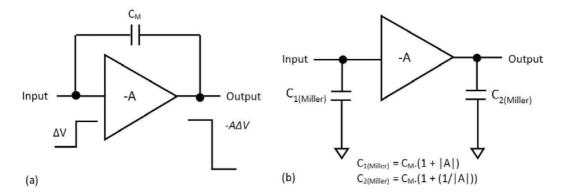

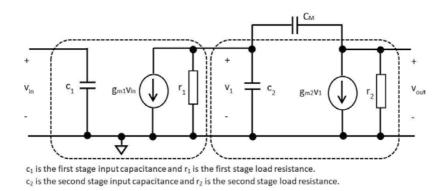

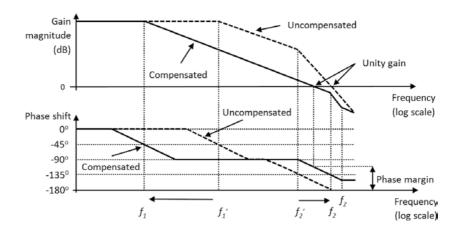

In Chapter 5, the design of the operational amplifier (op-amp) and its application at the front-end circuitry of a mixed-signal IC are illustrated. The chapter focuses on the design of the op-amp based on different compensation schemes and by incorporating negative Miller compensation. The op-amps are designed to operate at low voltage levels. The  $g_m/I_D$  ratio design approach is used to determine the transistor sizes. The op-amp performance is simulated using Cadence Spectre. Open-loop frequency responses are given emphasis during validation.

Chapter 6 presents the design of second-order analogue notch filters based on floating active inductors and conventional second-order notch LCR prototypes. The designs are validated using Cadence Spectre, 0.18 micron library. High-order notch filters are also reviewed. The simulation results of a sixth-order notch filter is shown to have ideal polynomial and ideal pole and zero position.

Kim Ho Yeap Associate Professor Department of Electronic Engineering Faculty of Engineering and Green Technology Universiti Tunku Abdul Rahman, Malaysia

Humaira Nisar

Associate Professor Department of Electronic Engineering Universiti Tunku Abdul Rahman, Malaysia

Section 1

# Introduction

Chapter 1

# **Introductory Chapter: VLSI**

Kim Ho Yeap and Humaira Nisar

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.69188

1. Introduction

Back in the old days about 40 years ago, the number of transistors found in a chip was, even at its highest count, less than 10,000. Take, for example, the once popular Motorola 6800 micro-processor developed in the mid 1970s. Fabricated based on the 6.0-µm feature size, the 6800 consisted of merely 4100 transistors in it. Nowadays, the number of transistors in a very large-scale integration (VLSI) [or some refer to it as the super large-scale integration (SLSI)] chip may possibly reach 10 billion, with a feature size smaller than 15 nm.

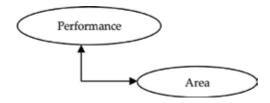

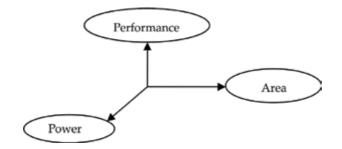

There is little doubt that the electronics world has experienced a significant advancement for the past 50 years or so and this, to a large extent, is due to the rapid technology improvement in the performance, power, area, cost and 'time to market' of an integrated circuit (IC) chip. To provide readers with an overall view of VLSI, this chapter gives a concise but complete illustration on the historical evolution, design and development of VLSI-integrated circuit devices.

# 2. A brief history

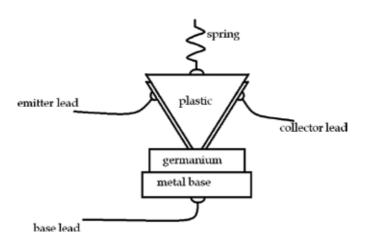

When transistors were first introduced in early 1900s, they were actually made of vacuum tubes. These transistors were relatively large in size and cumbersome to be used. In December 1947, however, three physicists working in the AT&T Bell laboratory attained a remarkable breakthrough in their design, changing the perception one used to have on transistors. Dr. John Bardeen, Dr. Walter Houser Brattain and Dr. William Bradford Shockley, Jr., invented the first point-contact semiconductor transistor using germanium. As shown in **Figure 1**, the point-contact transistor comprised an n-type germanium block and two gold contacts (i.e. the emitter and collector leads) placed in close proximity. When a small current was applied to one of the contacts, the output current at the other contacts was amplified.

Being much smaller in size, consuming much lower power, operating at relatively lower temperature and giving quicker response time, the semiconductor transistor is clearly more

Figure 1. An early model of the point-contact transistor.

superior to its conventional vacuum tubes brethren. It was these advantages and its viability that resulted in the replacement of vacuum tubes by the solid-state electronic devices. The rapid widespread usage of the semiconductor transistors in electronic circuits has triggered a dramatic revolution in the electronic industries, kicking off the era of semiconductor. Because of this significant contribution, Bardeen, Brattain and Shockley shared the Nobel Prize in Physics in 1956.

It may be worth noting that when this germanium solid-state device was initially introduced, it was not coined the term 'transistor'. Instead, it was generally referred to as the 'semiconductor triode'. According to the 'Memorandum For File' of Bell Telephone Laboratories [1], six names had been proposed for the device, namely 'semiconductor triode', 'surface states triode', 'crystal triode', 'solid triode', 'iotatron' and 'transistor'. Although the device had initially been referred to as the 'semiconductor triode', the word 'transistor' (which originates from the abbreviated combinations of the words 'transconductance' and 'varistor') had ultimately turned out to be the winner of the internal poll [1].

The first commercially available silicon transistors were manufactured by Dr. Gordon Kidd Teal in 1954. Since silicon gives much better performance than germanium transistors, the substrate material for transistors was gradually changed to silicon. In 1955, the first diffused silicon transistor made its appearance. To reduce the resistivity of the collector, the transistor with an epitaxial layer added onto it was developed in 1960. It was also in the same year the planar transistor was proposed by Dr. Jean Amedee Hoerni [2].

In 1958, Jack St. Clair Kilby who was then an engineer in Texas Instruments successfully developed the first integrated circuit. The device was just a simple 0.5-inch germanium bar, with a transistor, a capacitor and three resistors connected together using fine platinum wires. About a year later in 1959, Dr. Robert Norton Noyce from Fairchild Camera (also one of the co-founders of Intel Corporation) invented independently his own integrated circuit chip. The interconnection in Noyce's 4-inch silicon wafer was realized by means of etching the aluminium film which was first deposited onto a layer of oxide [2]. Both Kilby and Noyce shared

the patent right for the invention of the integrated circuit. In 2000, Kilby was awarded the Nobel Prize in Physics 'for his part in the invention of the integrated circuit'.

Since the advent of the semiconductor transistor and the demonstration on the workability of the integrated circuit chip about some 70 years ago, the electronic industries have been prospering hitherto. Electronic devices are now closely interwoven with human's life. They have, in many aspects, become indispensable to mankind. Indeed, one can easily find traces of electronic circuitries integrated into areas which intertwine seamlessly with the fabric of mankind's living hood. Some of these areas include transportation, telecommunication, security, medicine and entertainment, just to name a few.

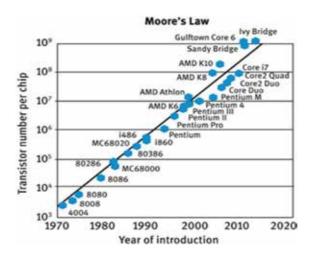

## 3. Moore's law

In April 1965, one of the co-founders of Intel Corporation, Dr. Gordon Earle Moore, predicted that the number of components (i.e. any electronic components which include not just transistors but capacitors, resistors, inductors, diodes, etc. as well) in an integrated circuit would double every year [3]. Ten years later in 1975, he revised his prediction to a doubling of every 2 years. Moore's prediction, which is more commonly known as Moore's law nowadays, has been widely used in the semiconductor and microelectronic industries as a tool to predict the increase of components in a chip for the coming generations [4]. To date, Moore's law has been proven to have held valid for more than half a century. Table 1 depicts the progressive trend of the integration level for the semiconductor industry. It can be observed from the table that the number of transistors that can be fabricated in a chip has been growing continuously over the years. In fact, this growth has complied closely with Moore's law. To distinguish the increase of transistors in every 10 years, each era is designated a name, that is, the SSI, MSI, LSI, VLSI, ULSI and SLSI eras. During the VLSI era, a microprocessor was fabricated for the first time into a single integrated circuit chip. Although this era has now long passed, the VLSI term is still being widely used today. This is partly due to the absence of an obvious qualitative leap between VLSI and its subsequent ULSI and SLSI eras, and partly, it is also because IC engineers and experts working in this field have been so used to this term that they decided to continue adopting it.

| Integration level                    | Year | Number of transistors in a chip |  |  |

|--------------------------------------|------|---------------------------------|--|--|

| Small-scale integration (SSI)        | 1950 | Less than 100                   |  |  |

| Medium-scale integration (MSI)       | 1960 | Between 100 and 1000            |  |  |

| Large-scale integration (LSI)        | 1970 | Between 1000 and 10,000         |  |  |

| Very large-scale integration (VLSI)  | 1980 | Between 10,000 and 100,000      |  |  |

| Ultra large-scale Integration (ULSI) | 1990 | Between 100,000 and 10,000,000  |  |  |

| Super large-scale integration (SLSI) | 2000 | More than 10,000,000            |  |  |

Table 1. Integration level of an integrated circuit chip.

## 4. The field effect transistors

Today, the transistors fabricated in an IC device are mostly metal oxide semiconductor field effect transistors (MOSFETs). The earliest paper describing the operation principle of a MOSFET can be traced back to that reported in Julius Edgar Lilienfeld's patent in 1933 [5]. In 1959, Dr. Dawon Kahng and Dr. Martin M. (John) Atalla at the Bell Telephone Laboratories successfully invented the MOSFET [6]. In 1963, two engineers from the Radio Corporation of America (RCA) Princeton laboratory, Dr. Steven R. Hofstein and Dr. Frederic P. Heiman, presented the theoretical description on the fundamental nature of the silicon planar MOSFET [7]. In the same year, Dr. Frank Marion Wanlass of Fairchild Semiconductor invented the first complementary metal oxide semiconductor (CMOS) logic circuit [8].

### 4.1. The MOSFET

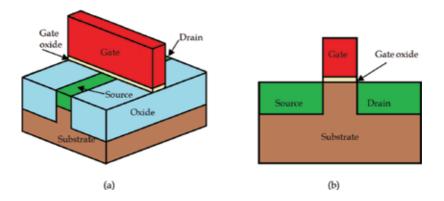

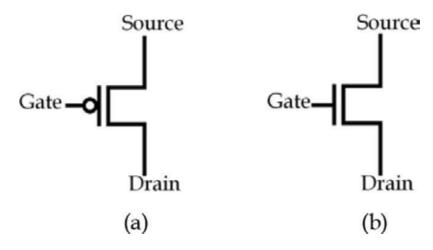

The MOSFET is basically a device that operates like a switch or an amplifier in electronic circuits. **Figure 2** depicts the basic structure of the MOSFET. The device consists of four terminals, namely the drain (*D*), source (*S*), gate (*G*) and substrate or bulk (*B*) terminals. Basically, the device is composed of three layers—a poly-silicon layer (i.e. the gate terminal), an oxide layer (i.e. the gate oxide) and a single-crystal semiconductor layer (i.e. the substrate). In the early days, the gate terminal was made of aluminium. It is from these three layers of materials that the FET device derived its name. In mid 1970s, however, the gate material was replaced with polysilicon. The high-temperature stability of the polysilicon gate is used as a mask to form the self-aligned source and drain terminals via ion implantation, rendering higher accuracy for the formation of these two terminals. Although the gate today is no longer made of aluminium, the term MOSFET has been so widely accepted that it stays until today.

The operation principle of a MOSFET is actually quite simple. When a voltage is applied in between the drain and source terminals, a conducting channel is required to be formed between the two terminals to close the circuit (i.e. to allow current to flow). A voltage connected to the gate terminal acts like a switch. Given sufficient magnitude (and the correct

Figure 2. The (a) basic structure and (b) cross section of a MOSFET.

polarity), the gate voltage is able to attract carriers to the gate oxide-substrate interface, forming a channel which connects the source and drain terminals.

A MOSFET can be categorized into two types, depending on the dopants of the drain and source terminals, as well as the substrate. When both the drain and source terminals, in a p-type substrate, are heavily doped with donator ions (such as phosphorous or arsenic), a negative channel is to be formed in between them to conduct current. On the other hand, when both terminals, in an n-type substrate, are heavily doped with acceptor ions (such as boron), a positive channel is to be formed. The former device is therefore known as a negative-channel MOSFET or an NMOS transistor, while the latter is known as a positive-channel MOSFET or a PMOS transistor. **Figure 3** shows the circuit symbols of both PMOS and NMOS transistors.

The size of a MOSFET transistor is measured by the gate length, which is also commonly known as the feature size or feature length *L*. The feature size *L* has been shrinking tremendously over the years. Transistors with the size of 50  $\mu$ m in the 1960s have been scaled down to less than 15 nm in 2017. The reduction of size allows a higher density of transistors to be fabricated in a single die. Overseen by the Taiwan Semiconductor Industry Association (TSIA), the United States Semiconductor Association (SIA), the European Semiconductor Industry Association (JEITA) and the Korean Semiconductor Industry Association (KSIA), the International Technology Roadmap of Semiconductor (ITRS) is produced to forecast how the technology is expected to evolve. The purpose of the ITRS is to ensure healthy growth of the IC industries. **Table 2** lists the progressive reduction of the feature size published in ITRS 2.0 [9].

### 4.2. The FinFET

As the feature size reduces to the submicron regimes, fields at the source and drain regions may become comparatively high, and this may give certain adverse effects to the charge

Figure 3. The symbol of (a) a PMOS transistor and (b) an NMOS transistor.

| Physical gate length        | Year |      |      |      |      |      |      |  |  |

|-----------------------------|------|------|------|------|------|------|------|--|--|

|                             | 2015 | 2017 | 2019 | 2021 | 2024 | 2027 | 2030 |  |  |

| High-performance logic (nm) | 24   | 18   | 14   | 10   | 10   | 10   | 10   |  |  |

| Low-performance logic (nm)  | 24   | 20   | 16   | 12   | 12   | 12   | 12   |  |  |

Table 2. Forecast of gate length by ITRS.

distribution. Some of the examples of these short-channel effects are the threshold voltage roll-off in the linear region, drain-induced barrier lowering (DIBL) and bulk punch-through [10]. To suppress these effects, additional steps, such as the introduction of retrograde well, lightly doped drain, halo implantation, and so on, have been introduced to the IC fabrication process [11]. As the device continues to shrink, however, curbing the short-channel effects turns out to be a strenuous task. When the feature size approaches the sub-nanometre range (i.e. 90 nm and below), static leakage current due to the short-channel effects has become a serious problem.

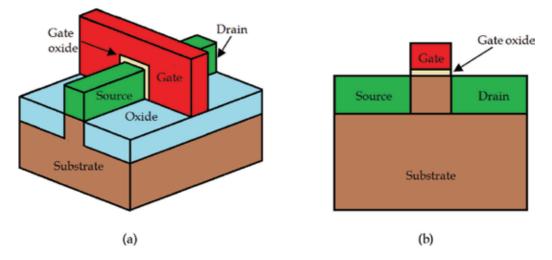

When the technology node reached 22 nm in 2011, Intel Corporation announced the fabrication of the tri-gate transistor, replacing the conventional planar MOSFET. More commonly known as the FinFET, this device has a three-dimensional transistor structure, as shown in **Figure 4**. From the figure, it is clear that a FinFET is named so because of the protruding source/drain terminals from its substrate surface, which closely resemble the fins of a fish. Since the gate wraps around the inversion layer, FinFETs provide higher current flow from source to drain. This feature also allows better control of the current flow—it reduces current leakage considerably when the device is at its 'off-state' and minimizes short-channel effects at its 'on-state'. Since the device has lower threshold voltage than the planar MOSFET, a FinFET can also operate at a lower voltage. In other words, the new device shows less leakage, faster switching and lower power consumption. However, certainly, the efficiency improvement

Figure 4. The (a) basic structure and (b) cross section of a FinFET.

found in the FinFET comes at the expense of increased fabrication complexity. The introduction of additional fabrication steps is inevitable in order to form the fin-like structure.

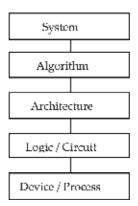

# 5. VLSI design flow

Generally, the design process of a VLSI chip involves three stages namely the (i) behavioural, (ii) logic circuit and (iii) layout representations. At each of this stage, verification is to be performed at the end before proceeding to the next. Hence, it is common to have repetitions and iterations in the processes [12].

## 5.1. Behavioural representation

Behavioural representation is the first step of the entire VLSI design flow. At this stage, it is important to specify the functionalities of the device and how it is going to communicate with the exterior. The design architecture is to be drawn panned out. A hardware description language (HDL) such as Verilog HDL or VHDL is used to define the behaviour of the device.

## 5.2. Logic circuit representation

After the HDL codes are successfully simulated, functional blocks from standard cell libraries are used to synthesize the behavioural representation of the design into logic circuit representation. Once the design is verified, the gate level netlist is generated. The netlist is necessary in order to develop the layout of the design.

## 5.3. Layout representation

At the final stage, the physical layout of the design is created. The process starts with floor planning which defines the core and routing areas of the chip. In order to optimize the design, the building blocks are arranged and orientated at their best locations. This process is known as placement. Once this is completed, a routing process is performed to interconnect the building blocks.

# 6. IC fabrication

To fabricate the chip, the layout is sent to a fab or a foundry. In a fab, a single-crystal semiconductor ingot is first grown. Wafers are then sliced from the ingot. The layout is printed onto the dice in each wafer. In the initial step of chip fabrication, the active regions or wells for the NMOS and PMOS transistors are first formed at the substrate. In order to separate the transistors, an oxide layer is subsequently deposited in between each neighbouring well. Transistors are then built at each active region. The primary processes to form a transistor include the growth of the gate oxide layer, the deposition of the poly-gate, and the doping of the source and drain regions. In the final fabrication step, the transistors are interconnected in accordance to the layout of the design. In a nutshell, the process of chip fabrication can be broadly separated into four stages: (i) well formation, (ii) device isolation, (iii) transistor making and (iv) interconnection [13]. Although the walkthrough may appear straight forward, it is, in practical, complicated and laborious. To fabricate a VLSI chip, the die has to undergo repetitive thermal processes (such as oxidation, diffusion, annealing, etc.), lithography, ion implantation, etch, dielectric film deposition (such as chemical vapour deposition or CVD), chemical mechanical polishing (CMP) and metallization [13].

# 7. IC packaging

To protect the chip from harsh external environment (e.g. being exposed to UV light or moisture or being scratched), it is essential to encapsulate the chip in a package. The three most commonly used techniques for packaging are (i) wirebonding, (ii) flip-chip and (iii) tapeautomated bonding (TAB) [4]. Once the chip is carefully packaged, it is then ready to be released to the market.

# Author details

Kim Ho Yeap\* and Humaira Nisar

\*Address all correspondence to: yeapkimho@gmail.com

Tunku Abdul Rahman University, Jalan Universiti, Bandar Barat, Kampar, Perak, Malaysia

# References

- [1] Arsov GL. Celebrating 65th anniversary of the transistor. Electronics. 2013;17:63-70. DOI: 10.7251/ELS1317063A

- [2] Lukasiak L, Jakubowski A. History of semiconductors. Journal of Telecommunications and Information Technology. 2010;1:3-9. DOI: 10.1088/0031-9120/40/5/002

- [3] Moore GE. Cramming more components onto integrated circuits. Electronics. 1965;38:14-117. DOI: 10.1109/N-SSC.2006.4785860

- [4] Yeap KH. Fundamentals of Digital Integrated Circuit Design. 1st ed. Central Milton Keynes: Authorhouse; 2011

- [5] Lilienfeld JA. Method and apparatus for controlling electric currents. U. S. Patent No. 1745175A (Filed October 8, 1926, issued January 28, 1930)

- [6] Kahng D. Electric field controlled semiconductor device. U. S. Patent No. 3, 102, 230 (Filed 31 May 31, 1960, issued August 27, 1963)

- [7] Hofstein S R, Heiman, FP. Silicon insulated-gate field-effect-transistor. Proceedings of IEEE. 1963;51:1190-1202

- [8] Wanlass SM, Sah CT. Nanowatt logic using field-effect metal-oxide semiconductor triodes. In: Proceedings of the IEEE Conference on Solid-state Circuits Conference. Digest of Technical Papers; 1963; Philadelphia, PA, US. p. 32-33

- [9] International Technology Roadmap for Semiconductors 2.0 [Internet]. 2015. Available from: https://www.semiconductors.org [Accessed: 3 April 2017]

- [10] Sze SM. Semiconductor Devices: Physics and Technology. 2nd ed. New York, NY: John Wiley and Sons; 2002

- [11] Ahmad I, Ho YK, Majlis BY. Fabrication and characterization of a 0.14 µm CMOS device using ATHENA and ATLAS simulators. International Scientific Journal of Semiconductor, Physics, Quantum Electronics, and Optoelectronics. 2006;9: 40-44. DOI: https://doi.org/10.15407/spqeo

- [12] Kang S–M, Leblebici Y. CMOS Digital Integrated Circuits: Analysis and Design. Singapore: McGraw-Hill; 2005

- [13] Xiao H. Introduction to Semiconductor Manufacturing Technology. Upper Saddle River, New Jersey: Prentice Hall; 2001

Section 2

# Physics of MOSFET's

# Transistor Degradations in Very Large-Scale-Integrated CMOS Technologies

Chang Yeol Lee

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.68825

#### Abstract

The historical evolution of hot carrier degradation mechanisms and their physical models are reviewed and an energy-driven hot carrier aging model is verified that can reproduce 62-nm-gate-long hot carrier degradation of transistors through consistent aging-parameter extractions for circuit simulation. A long-term hot carrier-resistant circuit design can be realized via optimal driver strength controls. The central role of the  $V_{\rm CS}$  ratio is emphasized during practical case studies on CMOS inverter chains and a dynamic random access memory (DRAM) word-line circuit. Negative bias temperature instability (NBTI) mechanisms are also reviewed and implemented in a hydrogen reaction-diffusion (R-D) framework. The R-D simulation reproduces time-dependent NBTI degradations interpreted into interface trap generation,  $\Delta N_{\rm it}$  with a proper power-law dependency on time. The experimental evidence of pre-existing hydrogen-induced Si–H bond breakage is also proven by the quantifying R-D simulation. From this analysis, a low-pressure end-of-line (EOL) anneal can reduce the saturation level of NBTI degradation, which is believed to be caused by the outward diffusion of hydrogen from the gate regions and therefore prevents further breakage of Si–H bonds in the silicon-oxide interfaces.

**Keywords:** hot carrier injection (HCI), hot carrier degradation (HCD), hot carrier-resistant design, negative bias temperature instability (NBTI), reaction-diffusion (R-D) of hydrogen

# 1. Introduction

Since the concept of an integrated circuit was first proposed by Jack Kilby in 1958, and a first version of a self-aligned poly-silicon gate CMOS-integrated circuit was fabricated at Fairchild® in 1968, integrated circuit technology has led to unprecedented thriving and prosperity in the electronic industry for the last half century. The initial integration of a number of transistors started with only a few tens in a circuit, which we call small-scale integration (SSI) has today

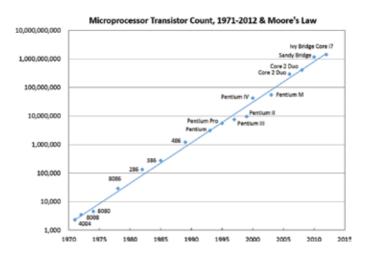

© 2018 The Author(s). Licensee InTech. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. expanded to a few billions, called very large-scale integration (VLSI) or ultra large-scale integration (ULSI). The annual growth rate of the number of transistors per IC has followed a well-known formula, Moore's Law, which indicates that the density of devices per chip doubles every 18 months, that is, the population of transistors in a chip increases by 1000 times every 15 years. Although in the beginning it was a merely an observation, it evolved into a de facto mandatory target for cutting-edge technology developers. For example, the Intel® CPU transistor count has faithfully followed Moore's Law for four decades (1971–2012) (**Figure 1**). Specifically, their newest microprocessor, Ivy Bridge Core i7<sup>TM</sup>, possesses 1,400,000,000 transistors [1]. It is a 609,000× increase in transistor count from its 1971 version. Such an exponential increase in integration number is attributed to a series of successes in shrinking feature size. The benefit of scaling is obvious: more integrated transistors enable more sophisticated datadriven operations and less switching delays per logic gate, thereby enhancing data transaction bandwidth. More data with enhanced speed play a decisive role in the rapid growth of the information and communication industry.

During the continuous pursuit of scaling, the following inherent issues have arisen:

- The challenge to sustain photolithographic pattern fidelity and critical dimension (CD) uniformity becomes profound as dimension scaling and integration levels increase.

- As transistor gate length is shrunk, electric field strength inside of a transistor increases and more degradation may occur in devices. Vertical and lateral e-fields can be mitigated by reduction of bias voltage, V<sub>DD</sub>. Its minimum level tends to be limited by the minimum threshold voltage of logic gates defined by distinguishable high states against thermal noise and permissible off-leakage currents. Since the V<sub>DD</sub> limit of around 1.0 V is already achieved in state-of-the-art technologies, inevitable increases of internal e-fields inside of devices may define the practical limit of technology scaling.

**Figure 1.** Intel® microprocessor transistor count evolution between 1971 and 2012. For the last 40 years, it has consistently behaved as predicted by Moore's Law. (Source: Intel Corp, Web Page [1]. Figure 1 is a graphical translated version, which was originally expressed in a tabular form in [1].)

The first issue is directly related to how short are the wavelengths of photolithographic light sources we employ. A 193-nm ArF light source with immersion ambience is known to have 40-nm patterning capability as its best performance. Since a feasible solution for a new light source with a lesser wavelength than ArF has not yet been found, a complicated combination of photolithography and etching processes, for example, a double-spacer pattern technology (D-SPT), is employed to enable the latest 10-nm range patterns. Such a complicated combination of critical steps may cause a sizable variation of CDs. As a consequence, much expertise and extensive trials and corrections are required to achieve pattern optimization, which becomes the confidential property of cutting-edge companies.

So solving the first issue relies in large part on skill and trial-and-error correction processes. By contrast, the second issue is related largely to scientific analysis. When bias is applied to a scaled MOSFET, a localized e-field is established in the drain side, which can accelerate mobile carriers (electrons or holes) passing this region. Some of the accelerated carriers can trigger an avalanche multiplication process, which increases the possibility of generating energetic carriers that can surmount the energy barrier between silicon/silicon dioxide or cause damage in Si/SiO<sub>2</sub> interface. Energetic carriers or "hot carriers" can also be generated by energy exchange during carrier-carrier-scattering processes. This kind of device degradation mechanism is called "hot carrier injection (HCI)," or "hot carrier degradation (HCD)" and is regarded as a typical degradation mechanism driven by high lateral e-fields or  $V_{\rm DD}$ . The most efficient prevention of this kind of degradation is reducing  $V_{\rm DD}$ . Large efforts have been devoted in device and circuit research to develop power-efficient and degradation-aware low  $V_{\rm DD}$  transistors and circuit solutions. Despite this effort, there still inevitably remain high voltage needs in some specific applications, like word-line decoders in dynamic random access memory (DRAM) circuits.

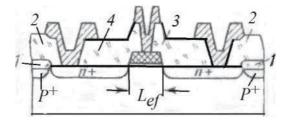

Dynamic Random Access Memory (DRAM) is one of the most popular memory devices featuring high data read/write speed with low bit cost. Compact placement of a single-bit storage capacitor and its switch transistor composes a DRAM cell. To avoid large off-leakage caused by high e-fields and thereby insufficient data retention capability, a three-dimensional (3-D) recess-channel scheme has recently been developed to reduce the e-field strength by extending the channel length. Although sufficient data retention time can be achieved by the 3-D recess-channel structures, reduction of the channel conductance of the long channel length expensively undermines the access speed. Non-scaled gate voltage can compensate for this loss. Such a decoupling from scaling rules (planar dimensions scale down, whereas gate voltages do not) may cause HCD issues in cell gate bias-pumping voltage ( $V_{PP}$ ) circuits. Since HCD is ascribed to the high electric field and/or high gate voltage, the mitigation strategy largely relies not only on device internal structure and doping profiles but also on the circuit and layout strategy. More detailed descriptions based on practical case studies and some general guidelines for the HCI-resistant circuit design can be found in the next section.

Lateral (channel length) shrinkage should be indispensably coupled with vertical (gate oxide thickness) shrinkage to maintain "long channel-like" transistor characteristics. The key enabler of vertical scaling is the superb electrical and material properties of silicon dioxide. As to silicon dioxide, only about 10 stacks of molecules can provide good isolation under 5.5–6.0 MV/cm of

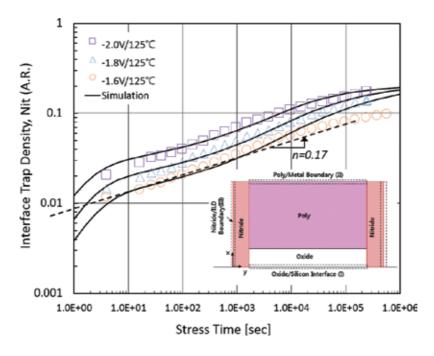

electric field intensity or can sustain "off-characteristics" of the few tens of nanometer-scaled MOSFET. Despite its stability, modern plasma-intensive fabrication processes can induce multiple charging in the gate electrodes, which can generate a number of silicon-oxide bond breakages. Most bond breakages can be passivated by end-of-line (EOL) hydrogen or deuterium passivation steps in order to electrically deactivate the dangling bonds. In this circumstance, another kind of device degradation mechanism can be triggered: negative bias temperature instability (NBTI) can be activated by moderated gate bias and temperatures applied in p-channels where abundant inverted holes and hydrogen-passivated silicon-dangling bonds exist. Although its mechanism is still not completely understood, atomic and/or molecular hydrogen reactions and diffusions associated with passivated Si/SiO<sub>2</sub> interfaces are widely accepted to define how and how much degradation takes place. In Section 3, a quantitative analysis is provided based on the reaction-diffusion of hydrogen simulation. A mitigation strategy for the long-term NBTI degradation is also suggested during the analysis.

In this chapter, studies on the most typical scaled-down-related device reliability issues, HCD in NMOS and NBTI in PMOS, are presented with practical case studies to attempt to broaden the reader's knowledge of device degradation and its impact on advanced CMOS scaling.

## 2. Hot carrier degradation

#### 2.1. Historical review

Hot carrier degradation (HCD) is one of the typical wear-out degradation mechanisms that causes catastrophic failures in systems. This kind of failure may implosively trigger irreversible and unrecoverable damage in systems. Readers can find typical cases of HCD failure syndromes and their impacts on complete products in Ref [2]. Many investigations have been conducted to reveal the transistor degrading hot carrier generation mechanism. The first successful theory structure was announced as the lucky electron model (LEM) suggested by Hu et al. in 1985 [3]. The LEM is regarded as a classic theory and has been widely used so far because it allows the depiction of a clear image for hot carrier generation and its role in creating interface traps. It focuses on e-field-driven hot carrier generation. A quasi two-dimensional analysis of Poisson's equation derives the exponential shape of e-fields in the velocity saturation region (VSR) and a sharp peak of e-fields built in front of the neutral drain region [4]. All the energy gain processes are assumed to be concentrated in the peak e-field spot where lucky electrons can surmount the Si/SiO<sub>2</sub> energy barrier (3.2 eV) and generate the Si interfacial traps,  $N_{it}$  [3]. On this basis, the following interface generation rate,  $r_{it}$ , was derived:

$$r_{it,LEM} = C_1 \cdot I_D \cdot \left(\frac{I_B}{I_D}\right)^{\Phi_{it}/\Phi_{ii}}$$

=  $C_1 \cdot I_D \cdot \left[A \cdot (V_D - V_{DSAT}) \cdot \exp\left(\frac{-B\ell}{V_D - V_{DSAT}}\right)\right]^{\Phi_{it}/\Phi_{ii}}$  (1)

where  $I_B$  and  $I_D$  are substrate current and drain current, respectively,  $\Phi_{ii}$  is the impact ionization threshold energy (1.3 eV for electrons) and  $\Phi_{it}$  is the interface state generation threshold

energy (3.7 eV for electrons),  $\ell$  is the characteristic length of VSR, and A, B, and C are constants, respectively. The power-law exponent,  $\Phi_{it}/\Phi_{ii}$ , is calculated to be 2.8 and this approximately matches experimental results that guarantee that the formula captures the correct image of HCD.

Transistor degradations mean that threshold voltages shift, mobility decreases, and drain-extrinsic resistances increase, all of which are ascribed to the interface trap generation. An isotope effect found by the scanning tunneling microscope (STM) method [5] and HCD experiments using hydrogen and deuterium-annealed samples [6] reveals that the dissociation of hydrogen from the interfacial Si–H bonds by injected energetic electrons can lead to unrecoverable degradations. The interface trap generation rate is empirically expressed as

$$\Delta N_{\rm it}(t) \propto (r_{\rm it} \cdot t)^n \tag{2}$$

where *n* is a time exponent that has been known to be around 0.5, which can be derived from a hydrogen diffusion-limited process [3]. An assumption of high diffusivities of hydrogen in silicon dioxide and in polysilicon gate regions is required to describe the 0.5 dependency. More specifically quickly removing the hydrogen from the interface and therefore also the repassivation process cannot dominantly influence the whole hydrogen reaction-diffusion process. Contradictable findings have been also reported in PMOS-negative bias temperature instability (NBTI) research [7]. Fast-diffused hydrogen in the SiO<sub>2</sub> region slows down in the silicon-nitride interface and in the polysilicon region due to small diffusion constants in those regions. This results in an accumulation of hydrogen in the SiO<sub>2</sub> region, which strikes a balance between dissociation and repassivation of silicon-dangling bonds. As a consequence, the interface state generation rate decreases to produce a smaller n (1/4–1/6). The discrepancy of time exponents between NMOS HCI and PMOS NBTI can be ascribed to the difference in the stressed area (only localized to the peak e-field spot in HCI vs. the whole gate oxide area in NBTI) and its influence on hydrogen diffusion profiles: an increasingly wider diffusion front of hydrogen in NMOS HCD enhances the  $\Delta N_{\rm it}$  rate more than that of PMOS NBTI where consistent one-dimensional diffusion of hydrogen occurs [8]. Furthermore, asymmetric behaviors between NMOS and PMOS (a large amount of degradation is quickly recovered when the stress biases are removed in PMOS, while no substantial recovery takes place in NMOS) imply the different nature of the Si-H dissociation produced by cold holes injected during NBTI stress and by hot electrons injected during HCI stress. The existence of deeplevel hole traps (DLHT) [9, 10] was proposed to draw a plausible picture of the asymmetric behavior. In the author's opinion, more studies are still needed to reveal the underlying physics for a comprehensive understanding.

As the e-field-driven (and consequently the applied voltage-driven) LEM reveals the HCD mechanism to be successful, it also instigates a voltage scale-down from 3.3–5.0 to 1.8–2.5 V in the shrunk gate length transistors in an effort to avoid HCD risk. However, HCD still remains against expectation in the 1.8–2.5-V regime. Neither hot electron injections into gate oxide (requires 3.2 eV at least) nor interface trap generations (requires 3.7 eV) may take place according to LEM because of insufficient driving voltage. A new hypothesis for the HCI generation mechanism, electron-electron scattering (EES), has been proposed to explain the

hot carrier generation in medium  $V_{DD}$  conditions. This hypothesis has been accepted through numerous experimental verifications [11]. It involves an energy-exchanging electron-scattering process to generate hot electrons under moderate bias conditions. A doubling of its energy can be achieved when a perfect elastic collision between the excited electrons, 1.8–2.5 V, is sufficient to generate the interface-degrading hot electrons. The mathematical expression of EES implies these aspects as follows:

$$r_{\rm it,EES} = C_2 \cdot I_D^2 \cdot \left(\frac{I_B}{I_D}\right)^m. \tag{3}$$

Note that the power-law exponent of  $I_D$  changes from 1 as in Eq. (1) to 2 as in Eq. (3) reflecting a statistical interaction of two independent sources for EES. This secondly found hot carrier generation mechanism dominates in the sub-micrometer range-scaled MOSFETs whose drain currents have a range between 40 and 500  $\mu$ A/ $\mu$ m with high  $V_{GS}$  drive [11, 12].

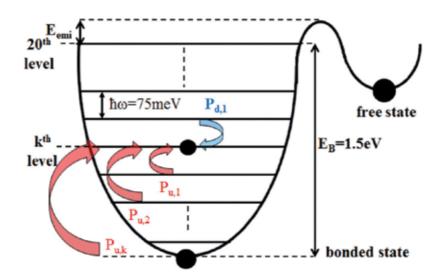

Further voltage scale-down to 1.0–1.2 V might extinguish any possibility of hot carrier generation via LEM or EES mechanisms. A newly developed Si–H bond breakage model has been proposed and demonstrated in deca-nanometer-scaled transistors [13]. Multivibrational hydrogen release (MVHR) is the third kind of mechanism, which is activated through high current injection (the minimum threshold is known to be 1.5 mA/µm), with weak voltage dependency. Since an electron can transfer its kinetic energy to the silicon lattice via optical phonon resonance, the multiple striking of electrons into Si–H bond can lead hydrogen to multiple jumps in its energy state to approach the bond-breaking threshold energy,  $E_B$ . This kind of hydrogen-dissociated process, namely multiple vibrational hydrogen release (MVHR), can be triggered by low-energy cold carriers in a sub-1-V-biased channel [13]. The quantum mechanical picture of the process is illustrated in **Figure 2**, and the mathematical expression was proposed to fit the experimental data as

$$r_{\rm it,MVP} = C_3 \cdot \left[ V_{\rm DS}^{1/2} \left( \frac{I_D}{W} \right) \right]^{E_B/\hbar\omega} \cdot \exp\left( \frac{-E_{\rm emi}}{k_B T} \right) \tag{4}$$

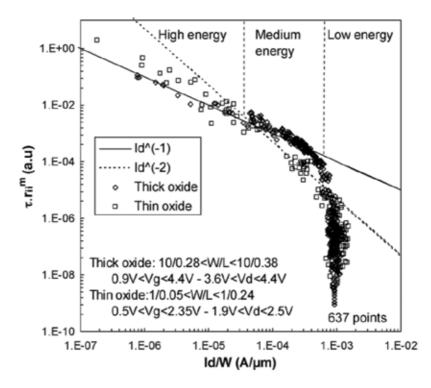

where  $E_{\text{emi}}$  (~0.26 eV) is the barrier height of  $E_B$  from the highest energy state of bonded hydrogen. The unit resonance energy per single phonon excitation,  $\hbar\omega$  (~0.075 eV), and threshold energy,  $E_B$  (~1.5 eV), defines the required number of the phonon excitation to be  $\frac{E_B}{\hbar\omega} = 20$ . Due to its tremendously strong power-law dependency on the drain current, a special caution should be paid not to let the transistor's drain current exceed the threshold of the third kind of HCD in any type of transistor operations including burn-in tests; otherwise, very quick wearout failures may take place. The three kinds of hot carrier generation mechanisms are illustrated in **Figure 3** compared with a large set of experimental data.

To summarize the history of HCD mechanism finding, LEM dominates when  $V_{\text{DS}} \ge 3.0 \text{ V}$ . Energy-driven or current-driven multiple-particle (MP) mechanisms, EES for 40–500- $\mu$ A/ $\mu$ m driving range and MVHR for even higher ranges, are subsequently developed. The maximum applied voltage and the minimum duty cycle of CMOS logic design guidelines have been

**Figure 2.** Schematic of Si-H potential well showing the processes increasing the occupancy of the  $k^{th}$  level, coming from direct excitation, giving any number of energy quanta between 1 and k, and from the de-excitation of the  $(k+1)^{th}$  level.  $P_{u,i}$  and  $P_{d,i}$  are, respectively, the probability of excitation and de-excitation, giving or losing *i* energy quanta. Reprinted with permission from Ref. [11], © 2013 IEEE.

**Figure 3.**  $\tau \cdot r_{ii}^m$  normalized lifetimes versus drain current showing three regimes of hot carriers. Reprinted with permission from Ref. [14], © 2007 IEEE.

made in strong awareness of the e-field-driven HCD. The maximum current-limiting constraints to prevent the current-driven HCD have not yet been made according to the author's knowledge. It might not be required since the ultimately scaled 3.8-nm-gate-long planar transistor demonstrates less than an (?) 1-mA/ $\mu$ m performance [15]. It is appreciably below the third limit. However, it can be exceeded by current boosting three-dimensional fin-gate structures.

Since the newest developed 3-D FinFETs have been announced reaching 1.0–1.5 mA/ $\mu$ m at V<sub>GS</sub> of 0.75–0.8 V [16, 17], research work should concentrate on clarifying the risk of HCD in FinFET [18-20]. Inherent HCD risks in the FinFETs occur due to three reasons. First, the number of inversion electrons is increased by the surrounding three-dimensional gate overdriving  $(V_{\rm GS}-V_{\rm TH})$ , which supplies more electrons into the Si–H bond-breaking procedure through the multi-vibration mode. Second, the three-dimensional-surrounding gate introduces additional side interfaces between Si/SiO<sub>2</sub> by the fins, where additional Si–H bond breakage can occur. Furthermore, it can be enhanced when the gate is aligned to the (110) direction, the surface direction of the fin should also be (110) and the silicon surface density of the (110) plane is  $1.4 \times$ larger than that of (100) plane [21]. Third, the three-dimensional surrounding of gate structures confines the heat dissipation only through the bottom-directional narrow body, thereby increasing the thermal resistance of the heat dissipation path. The lattice-carrier scattering generates heat that is referred to as "self-heating" and this increase of the lattice temperature is proportional to the thermal resistance. The temperature activation of HCD therefore becomes a critical reliability issue especially in high-current driving and poor heat dissipation devices like FinFETs [18]. A more detailed description of temperature dependency on hot carrier generations is found in the following section.

### 2.2. Temperature dependency on hot carrier generations

According to the LEM mechanism, carriers gain kinetic energy from the e-field, *F*, through free accelerated motion. The energy distribution of electrons is affected by the mean free path,  $\lambda$ , through,

$$f(E) = e^{-E/q\lambda F}.$$

(5)

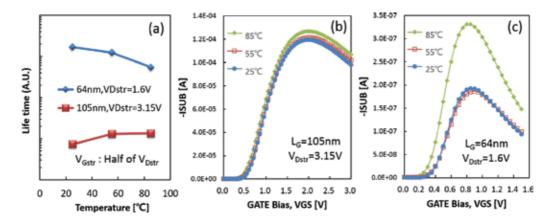

Self-heating and/or ambient heating induces lattice vibrations that scatter the electrons to prevent gaining sufficient kinetic energy from triggering impact ionization. It can be assumed that  $\lambda$  decreases as the lattice temperature increases. As a result, higher energetic carriers can be generated at lower temperatures. **Figure 4** compares the long and high-biased (LH) transistors' and the short and low-biased (SL) transistors' HCI properties depending on temperature. That temperature dependency of the HCI lifetime and the substrate current follow the LEM picture in LH but not in SL suggesting that the LEM prediction is valid only in LH ranges but not in SL.

Monte Carlo simulation-based studies reveal that electron energy distribution function is composed of an e-field-driven main region and thermal tail [22, 23]. The knee voltage,  $V_{\text{EFF}} = V_{\text{DS}} - V_{\text{DSAT}} + V_{o}$ , separates two regions, where  $V_{o}$  is the voltage drop in the halo

Transistor Degradations in Very Large-Scale-Integrated CMOS Technologies 23 http://dx.doi.org/10.5772/intechopen.68825

**Figure 4.** Hot carrier characteristics of 64-nm-gate-long, 1.6-V  $V_{DS}$  driving NMOSFET (SL) compares with that of 105-nmgate-long, 3.15-V  $V_{DS}$  driving NMOSFET (LH). (a) Hot carrier lifetimes of SL and LH show different thermal dependencies: HC Lifetime of LH increases with temperature in accordance with the LEM framework, but does not for SL. (b)  $V_{CS}$ dependent substrate currents of LH slightly enhance with temperature. (c) A remarkable increase at high temperature (85°C) found in SL suggests a temperature activation of HCD, which cannot be explained through the LEM framework.

region of the drain side. In LH transistors, hot carriers generated in the main region are dominant because of the large value of  $V_{\text{DS}}$ , which shows the negative dependency on temperature through  $\lambda$ . The scaled-down drain biases in short channel transistors reduce the  $V_{\text{EFF}}$  and the dominant hot carrier generation region is shifted from the main to the thermal tail via EES or MVHR. Since both are temperature-activating processes, the overall HCD shows a positive dependency on temperature that is detrimental especially in high-current-driving self-heating transistors like FinFETs.

#### 2.3. PMOS hot carrier degradations

Traditionally, HCDs in PMOSFETs have not been taken seriously because a large energy barrier between Si and SiO<sub>2</sub> (~4.8 eV [24]) and a high-impact ionization threshold ( $\Phi_{ii}$  = 1.43–1.92 eV [25]) of holes make difficult a LEM-like HCD in normal operational voltage ranges. The drainavalanche hot-electron (DAHE) generates favorable electron injections into SiO<sub>2</sub> in low  $V_{GS}$  (1/3-1/4 of  $V_{DS}$ ), which were known to be the dominant mechanism of HCD in PMOSFETs. The injected electrons fill the preexisting traps in the vicinity of the drain, which may cause effective gate length shortening, as  $L_{\text{eff}} = L_o - \Delta L(N_{\text{ox},e})$ , and therefore punchthrough and breakdown may occur. However, this is a self-limiting procedure due to the exponential decrease of the electron injection current as a function of distance to the drain and hence yields a logarithmic dependency of  $\Delta L(N_{ox,e})$  on time [26]. As PMOS gate oxide scales down, a turn-around of drain current degradation is observed, which is due to the charge re-emission and donor-like interface trap,  $\Delta N_{\rm it,d}$ , generation under the high vertical field [25]. The dominant degradation driver has also been changed from the hot electron injection to the hot hole injection as Tox scales down. These transitions rely on (1) nitridation of gate oxide to suppress boron penetration, which enhances the generation of the positive charge (PC), (2) as oxide e-field,  $F_{ox}$  exceeds 5MV/cm, NBTI degradation is triggered by cold hole injections at the source region, which are combined with hot hole injections at the drain region.

Abnormally large degradations of PMOS were reported in hot electron injection stress experiments at the cryogenic temperature of 77 K and subsequent anneal at elevated temperatures (300 K or higher) [27]. It is believed that the increase of carrier mobility and mean free path at 77 K creates additional damage sites in the oxide, which are initially inactivated at 77 K, and eventually convert to positive donor-type interface states as the de-trapped electrons leave vacancies in the annealing stage.

To summarize the hot carrier degradations in PMOSFETs, both electrons and holes created by impact ionization are responsible via their own natures for creating and/or changing the state of the oxide bulk traps and the interfacial traps. Since hot carrier generations in PMOSFETs are still negligible due to their low efficiency compared with those in NMOSFETs, cold hole injections to the SiO<sub>2</sub> can activate an appreciable number of interfacial and oxide bulk traps in the normal operational voltage range because holes are more efficient in trap generation processes than electrons are [28]. Cold hole injection is regarded as the most serious degradation mechanism of modern PMOSFETs. This subject is dealt with in Section 3 more precisely.

## 2.4. An energy-driven HCD modeling of NMOSFETs for circuit simulations

## 2.4.1. Aging model parameters

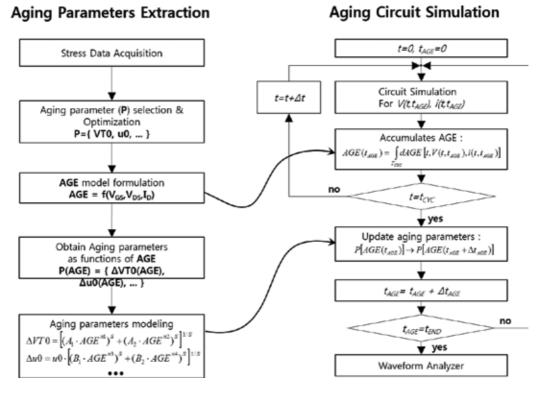

Transistors' degradation and the circuit performance degradation can be quantitatively analyzed through the circuit simulations by using the specific spice model parameter set, which we call "aging parameters." Properly chosen aging parameters among the whole spice model parameters should be accurate over the full  $V_{\rm DD}$  range varying  $V_{\rm GS}$  and  $V_{\rm DS}$  as a function of the "age," which is an amount of "degradation." In summary, an age is accumulated during a prescribed operation time per transistor, the age shifts the aging parameters, and finally aging parameters reproduce the degraded transistors' characteristics. All the calculations are fulfilled during aging circuit simulations with self-consistent aging-parameter updates. A recursive process (age determines the degradation of transistor and vice versa) executes during the simulation. The complete sequence of the aging-parameters extraction and aging circuit simulations is schematically illustrated in Figure 5. Since the aging-parameters extraction is carried out under DC-stress conditions, some assumptions must be made regarding the validity of accumulated age and aging parameters updated during the AC circuit simulation, which include the following: (1) the static degradation rate and bias dependencies under DC stress conditions are assumed to be the same under AC stress conditions. This quasi-static approximation is generally accepted in HCD because the recovery after stress degradation is negligible and the total amount of degradation can be regarded as a singular function of AGE without any path dependencies; (2) the degradation is assumed to be a very slow process within the conventional time span of circuit simulation. It is an indispensable assumption for the sake of convenience and for the efficiency of the aging circuit simulation. It enables a decoupling of the aging accumulation from the aging-parameter update. One can accumulate age by using the voltage and current waveform, which is simulated with "constant" aging parameters during a prescribed time period,  $t_{CYC}$ . To control these non-overlapped sequences, aging circuit simulations can use two time variables, t and  $t_{AGE}$ . Age accumulation during  $t_{CYC}$  with timeinvariant aging parameters is controlled by t. Aging parameters are subsequently updated by

**Figure 5.** Schematics for aging-parameters extraction and aging circuit simulation procedures: Aging parameters (P) are selected from the transistor model parameters set to represent the experimental degradation with relevant physical mechanisms (*see left*). A unified degradation is modelled by an AGE and in turn aging parameters are extracted as a functionality of AGE. The aging circuit simulation is comprised of two non-overlapping loops, which are controlled by *t* and  $t_{AGE}$ , respectively (*see right*). The inner loop accumulates AGE with varying  $V_{GS}(t)$  and  $V_{DS}(t)$  for each transistor, and the outer loop updates the aging parameters using the accumulated AGE.

using the accumulated age as functions of  $t_{AGE}$ . A flowchart depicted in Figure 5 (right) illustrates the sequence of the aging circuit simulation in detail.

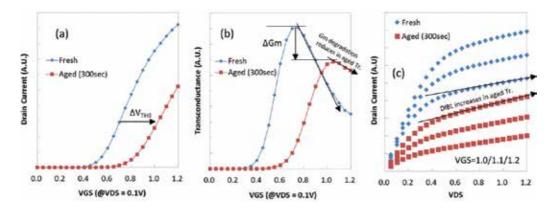

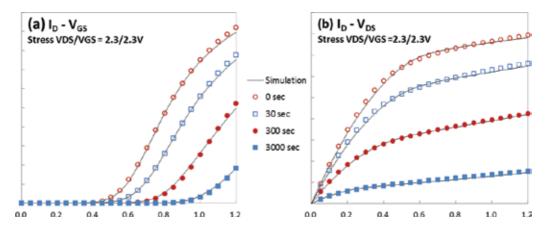

The proper sequence for the aging-parameter extraction can be exemplified in the following example: a 62-nm-gate-long NMOSFET is DC stressed with a  $V_{DS}$  within the range of 2.1–2.3 V and a  $V_{GS}$  within the range of 1.5–2.3 V. After a 300-s stress, transistors  $I_D - V_{GS}$ , and  $I_D - V_{DS}$  are typically compared to a fresh one as in **Figure 6**.

A threshold voltage shift and transconductance, Gm reduction, are found in stressed  $I_{\rm D} - V_{\rm GS}$  and Gm –  $V_{\rm GS}$  as shown in **Figure 6(a)**, and **(b)**. Selecting the spice model parameters **VTH0** for threshold voltage shift and **u0** for Gm reduction is the obvious choice for the aging parameters since  $Gm = \frac{W}{L}C_{\rm ox}V_{\rm DS}\frac{\partial\mu}{\partial V_{\rm GS}}$  in low  $V_{\rm DS}$  and only  $\frac{\partial\mu}{\partial V_{\rm GS}}$  term can be degraded by hot carriers. As a coefficient of the mobility model, **u0** can scale both  $\mu$  and  $\frac{\partial\mu}{\partial V_{\rm GS}}$  as shown in Eq. (6). One can find another important feature of degradation in **Figure 6(b)**; the reduction of the Gm-declining rate with  $V_{\rm GS}$  is distinct. It is related to the increase of interface trap charges. They do screen more e-fields from the gate, hence the influence of the gate is reduced and the

**Figure 6.** Comparisons of  $I_{\rm D}$ - $V_{\rm GS}$ , Gm- $V_{\rm GS}$ , and  $I_{\rm D}$ - $V_{\rm DS}$  showing the fresh and 300-s stressed with  $V_{\rm GS} = V_{\rm DS} = 2.3$  V of 62-nm-gate-long transistors. (a) A comparison of fresh and aged transistors'  $I_{\rm D}$ - $V_{\rm CS}$  clearly shows a stress induced **VTH0** shift. (b) Both the Gm and the Gm-declining rate on  $V_{\rm GS}$  are reduced after being stressed. (c) A growing slope for the drain current on the  $V_{\rm DS}$  is clearly shown in stressed  $I_{\rm D}$ - $V_{\rm DS}$ 's, which can be interpreted as a DIBL increase due to HC stress.

surface-roughness-scattering-controlled Gm is less decreased in high  $V_{GS}$ . According to the spice model parameter equations, the Gm-declining rate can be modeled in the effective mobility,  $\mu_{eff}$ , expressed in Ref. [29] as

$$\mu_{\text{eff}} = \frac{\mu 0 \cdot f(L_{\text{eff}})}{1 + UA\left(\frac{V_{\text{gsteff}} + 2V_{\text{th}}}{TOXE}\right) + UB\left(\frac{V_{\text{gsteff}} + 2V_{\text{th}}}{TOXE}\right)^2 + UD\left(\frac{V_{\text{th}} \cdot TOXE}{V_{\text{gsteff}} + 2\sqrt{V_{\text{th}}^2 + 0.0001}}\right)^2 \quad . \tag{6}$$

UA or UB may adjust the declining rate on  $V_{GS}$  ( $V_{gsteff}$  in Eq. (6)). But it is not preferable as both u0 and UA (or UB) appear in the same model equation, which makes it difficult to extract their optimum values independently. In other words, a lack of orthogonality may affect the quality of the parameter extractions. Thus, an alternative choice can be **rdsw**, which is a spice model parameter expressing the extrinsic resistance of drain and source regions. The drain resistance is increased by the accumulation of trapped electrons in the drain region. The Gm-declining rate is also affected by the accumulation of trapped electrons, which screen the gate electric field. Thus, choosing **rdsw** can include both a drain resistance increase and a Gm-declining rate decrease of degraded transistors without any ambiguity among parameters. The last parameter can be determined by observing **Figure 5(c)**. As the drain current-increasing slope along the  $V_{DS}$  is clearly shown in the aged transistors, one can choose a DIBL (drain-induced barrier-lowering) control parameter. An increase of DIBL originates from the same mechanism, which causes the increase of **rdsw**; the vertical e-field is screened by trapped charges and hence the channel inversion charges become more susceptible to the lateral e-field or  $V_{DS}$ . The DIBL formulation in the spice modeling [29] is

$$\Delta V_{\rm th}(DIBL) = -\theta_{\rm th}(DIBL) \cdot (ETA0 + ETAB \cdot V_{\rm BS}) \cdot V_{\rm DS} . \tag{7}$$

In Eq. (7), **ETA0** is a suitable parameter to describe the hot carrier-induced DIBL increase. Note that even though **VTH0** and **ETA0** may appear in the same threshold voltage model, they can

be distinguished from each other since **VTH0** is extracted from HC degradation data without any dependency on  $V_{DS}$ , but **ETA0** is the coefficient of  $V_{DS}$  in  $\Delta V_{th}$  that implies that one can extract both **VTH0** and **ETA0** independently. Selected aging parameters, **VTH0**, **u0**, **rdsw**, and **ETA0**, are optimized via appropriate numerical processes to best fit the experimental data. **Figure 7** compares the results where points mark the experimental data and lines are spice simulation results using optimized aging parameters.

#### 2.4.2. An energy-driven AGE model

The AGE is a commonly used parameter to accumulate the amount of degradation under various bias conditions in aging circuit simulation. Appropriate AGE model reflects underlying physics with a relevant functional form for the bias and time. According to field-driven HCD, one can define the AGE function as

$$AGE_{\rm FD} = \frac{I_D}{W \cdot H} \left(\frac{I_{\rm SUB}}{I_D}\right)^m \cdot t_{\rm STR} \tag{8}$$

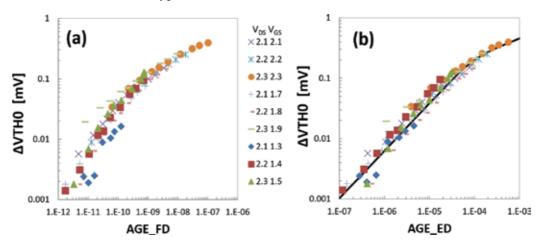

where *m* is known to be around 3 and *H* is a constant according to the field-driven HCD framework. **Table 1** checks the validity of this assumption. In this table, we can find that the largest VTH0 degradation occurs when  $V_{DS} = V_{GS}$ , among the various  $V_{DS}/V_{GS}$  bias sets, while the maximum substrate currents and AGEs do not coincide with that of VTH0 degradation. This mismatch implies that the field-driven mechanism is no longer valid for the 62-nm-scaled NMOS transistor.

In order to adjust the discrepancy of the field-driven AGE, one can modify H to be a function of  $V_{\text{DG}}$ , as a commonly used relief in the field. The fitting results will be compared with newly developed energy-driven AGE's results later. A simplified version of the energy-driven AGE model is proposed in Ref. [30] as

**Figure 7.** The aging-parameters optimization results fit the HCD measurements (points) with simulations (line) in (a)  $I_{D}$ - $V_{GS}$  and (b)  $I_{D}$ - $V_{DS}$  curves.

| $V_{\rm DS}/V_{\rm GS}$ | V <sub>DG</sub> | $I_{\rm SUB}/I_{\rm D}~({\rm x10^{-3}})$ | $AGE\_FD (H = 1, m = 3)$ | Measured ΔVTH0 [mV] |

|-------------------------|-----------------|------------------------------------------|--------------------------|---------------------|

| 2.1/2.1                 | 0.0             | 0.491                                    | 3.32E-09                 | 151                 |

| 2.2/2.2                 |                 | 0.861                                    | 1.72E-08                 | 252                 |

| 2.3/2.3                 |                 | 1.572                                    | 9.97E-08                 | 395                 |

| 2.1/1.7                 | 0.4             | 0.730                                    | 8.76E-09                 | 76                  |

| 2.2/1.8                 |                 | 1.210                                    | 3.97E-08                 | 146                 |

| 2.3/1.9                 |                 | 1.727                                    | 1.01E-07                 | 257                 |

| 2.1/1.3                 | 0.8             | 1.034                                    | 1.48E-08                 | 16                  |

| 2.2/1.4                 |                 | 1.754                                    | 8.44E-08                 | 95                  |

| 2.3/1.5                 |                 | 1.894                                    | 8.61E-08                 | 129                 |

The maximum  $\Delta$ VTH0 occurs at  $V_{\text{DS}} = V_{\text{GS}}$  ( $V_{\text{DG}} = 0$ V) for each  $V_{\text{DS}}$ . While  $I_{\text{SUB}}/I_{\text{D}}$  and AGEs do not follow  $\Delta$ VTH0 tendencies on bias.

**Table 1.** Field-driven ages (Eq. (8)) are calculated from the measured  $I_{SUB}$ ,  $I_{D}$ , and **VTH0** degradation ( $\Delta$ **VTH0**).

$$R_{\text{age}} = a(V_G - V_{\text{th}})^P \cdot e^{B(V_D - V_{\text{DSAT}})} + b(V_G)^C$$

(9)

where  $R_{age}$  is the accumulation rate of the age, which is expressed by the multiplication of carrier density,  $a(V_G - V_{\text{th}})^P$ , carrier energy,  $e^{B(V_D - V_{\text{DSAT}})}$  and  $b(V_G)^C$  term for a high  $V_G$  dependency. Compared with Eq. (8), the linear carrier density dependency of  $I_{\rm D}$  is generalized in Eq. (9) as having a power-law dependency with exponent P, which reflects the relevant mechanism of HC generation: one for field-driven, two for EES, and 20 for MVHR for a wide range of gate lengths of MOSFETs' and drain bias. The exponential term for carrier energy reflects the energy distribution of the electrons as a function of drain overdriving voltage,  $V_{\rm D}$  –  $V_{\rm DSAT}$ . The last term is negligible since it becomes significant only if the  $V_{\rm G}$  is larger than 3.0, which is beyond the normal operation range in modern technology. The saturation voltage,  $V_{\rm DSAT}$  is originally defined by the drain current saturation point in MOSFETs'  $I_{\rm D} - V_{\rm DS}$ relations. The velocity saturation of mobile carriers causes the drain current saturation of the scaled MOSFETs. At the same time,  $V_{\text{DSAT}}$  in the carrier energy distribution function defines the threshold energy to HCD. Although the notation  $V_{\text{DSAT}}$  is commonly used to denote the two different mechanisms, the values of  $V_{\text{DSAT}}$  for both mechanisms need not be the same. This is shown in Ref. [31] that the substrate current starts from a smaller  $V_{\text{DSAT}}$  but is still proportional to  $V_{\text{DSAT}}$ ; thus the drain voltage dependency has the form of  $V_D - \eta V_{\text{DSAT}}$ , where  $\eta$  is a fitting constant defined within 0-1. From this observation,  $V_{\text{DSAT}}$ , as the threshold of HCD, should be extracted from both drain current and substrate current measurements, as a form of  $V_{\text{DSAT}}$ , or alternatively a new energy-driven AGE can be modified as

$$AGE_{\rm ED} = \left(V_G - V_{\rm th}\right)^{n_G} \cdot \left(\frac{K}{\ln(I_D/I_{\rm SUB})}\right)^{n_D} \cdot t_{\rm STR}$$

(10)

where the well-known  $I_{SUB}/I_D = C(V_D - \eta V_{DSAT})e^{-V_o/(V_D - \eta V_{DSAT})}$  form is used to replace  $V_D - \eta V_{DSAT}$  by its simplified expression:  $V_D - \eta V_{DSAT} \approx K/ln(I_D/I_{SUB})$  and the exponential function for the energy dependency is replaced by a power-law function because it has a better

degree of freedom to fit to the experimental data. The last term of Eq. (9) is omitted as stated above. **Figure 8** compares the fitting results of the  $\Delta$ **VTH0** by using the conventional e-fielddriven AGE, Eq. (8), and the newly defined energy-driven AGE, Eq. (10). The *H* parameter in Eq. (8) is modified to have an exponential functional dependency of V<sub>GD</sub> to fit the measurement data. As shown in the figure, the **\DeltaVTH0** tends to slow down as AGE increases. The saturation phenomenon is commonly found in the aging-parameter measurements. The interpretation for the saturation is that the current is pushed down by the interface electrons at the lightly doped drain region, which reduces the interface trap influence on the drain current reduction [32], or a saturation of preexisting charge trapping [33] results in a two-slope shape on the aging parameters dependent on the AGE. A behavioral expression of this effect can be generalized in the following expression:

$$\Delta P(AGE) = [(P_1 \cdot AGE^{n1})^S + (P_2 \cdot AGE^{n2})^S]^{1/S}$$

(11)

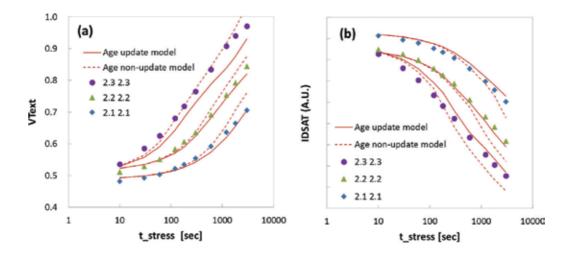

where S is the shape factor and has a negative digit. The two-slope combination of Eq. (11) is used to fit the **\DeltaVTH0** dependence on the AGE as shown in **Figure 8(b)**. As shown in the figure, the overall consistency is improved by using the energy-driven AGE defined by Eq. (10). **Figure 9** illustrates the aging-parameters extraction results by comparing the measurement and the aging simulation results. Two kinds of extraction methods are compared in the graph, which are as follows: (1) AGEs are extracted by using only fresh measurement values of  $V_{th\nu}$   $I_{D\nu}$  and  $I_{SUB}$  and (2) AGEs are extracted by degraded  $V_{th\nu}$   $I_{D\nu}$  and  $I_{SUB}$  in order to reflect "degradation of age" recursively. The overall matching property is improved by this update as shown in the figure.

# 2.5. A hot carrier-resistant design technique through $V_{GS}$ ratio controls

#### 2.5.1. V<sub>GS</sub> ratio and ADF

The last example is to demonstrate a hot carrier-resistant design technique. HC-resistant design techniques have been attracting more attention as technology gets smaller. A strong demand can be found in typical DRAM word-line driver circuits where the inherent risk of

Figure 8. Optimized  $\Delta$ VTH0s as a function of (a) the conventional field-driven age model (AGE\_FD) and (b) the newly developed energy-driven age model (AGE\_ED) are illustrated.

**Figure 9.** Aging-parameters' model extraction results are compared with the measurement data. As the age accumulation tends to slow down with the degrading ingredients (drain current and substrate current), the age update model parameter simulation results in (a) VText and (b)  $I_{DSAT}$  (solid lines) are less than those of the age non-update model (broken line). The age non-update model simulation results show an over-estimation especially in the deep degradation regime ( $t_{STRESS} > 1000$  s). From this aspect, one can conclude that the overall accuracy of the simulation is improved by age update feedback.

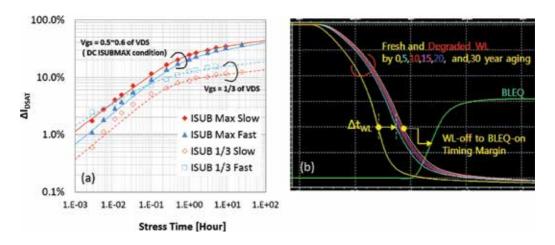

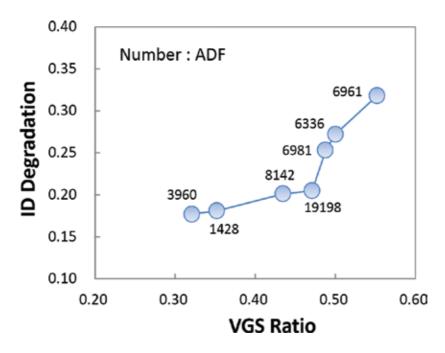

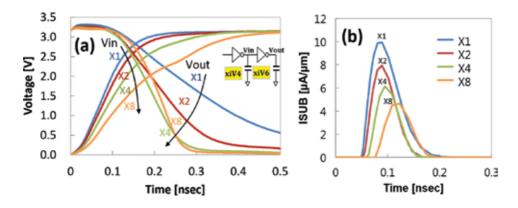

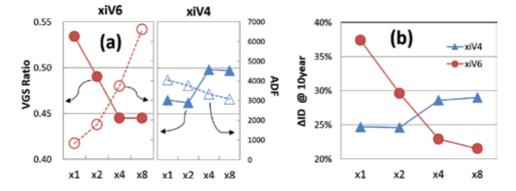

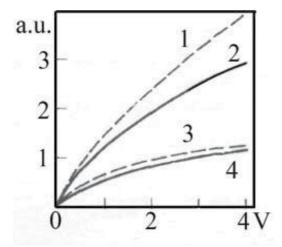

HCD exists due to non-scale-down word-line-pumping voltage ( $V_{PP}$ ). As stated above, the necessity for sustaining channel conductance in scaled cell transistors forces the  $V_{PP}$  to fix around 3 V. The field-driven mode can be a dominant HCD mechanism in such a high  $V_{PP}$ -biased 100-nm-long gate length transistors. According to the LEM, the maximum degradation occurs at the peak substrate current ( $I_{SUB}$ ) generating  $V_{GS}$  condition. The peak  $I_{SUB}$  generation  $V_{GS}$  defines the " $V_{GS}$  ratio",  $\gamma$ , which is  $V_{GS, peak}/V_{DD}$ . If the constant  $V_{DS}$  is applied under DC bias conditions,  $\gamma$  has its maximum value of around 0.5–0.6. The minimum value might be 1/3 since most CMOS transistors have their threshold voltage of 1/3 of  $V_{DD}$  and the drain voltage is assumed to pull down immediately as the gate turns on in the CMOS inverter operation. **Figure 10(a)** shows the HCD measurements with different  $V_{GS}$  ratios. The DC HCD reaches up to 40% at 100-h stress with  $\gamma = 0.5$ –0.6. Such a severe degradation does not seem to guarantee the lifelong serenity of the circuits without any kind of mitigation strategies. Several significant features of HCD are found in the figure:

- 1. As two time-slope phenomena are found in the figure as stated above, a sufficient timing margin is required to survive the initial rapid degradation. The overall timing shift of the WL driver reflects the "quasi-saturation effect" of the transistors' degradations as depicted in **Figure 10(b)**. As one can find in the figure, WL-off-degradation progresses toward a saturation at 5 years and very slowly degrades during further aging. In this design, wear-out is remarkably retarded due to this quasi-saturation phenomenon.

- 2. The  $V_{\text{GS}}$  ratio determines the quasi-saturation level of degradation. Compared at 100-h stress, only 1/3–1/2 of all degradations are shown in the  $\gamma = 1/3$  stress condition as opposed to in  $\gamma = 0.5$ –0.6. Thus, the reduction of  $\gamma$  is the primary design target for long-term HCD reliability.

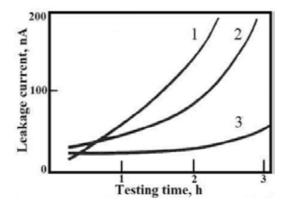

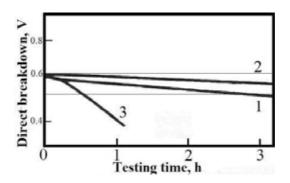

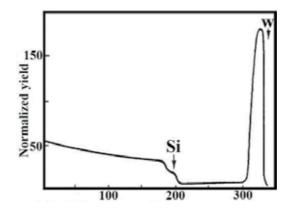

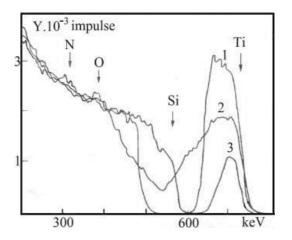

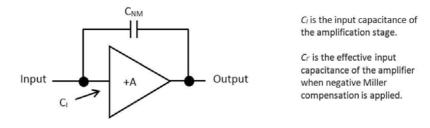

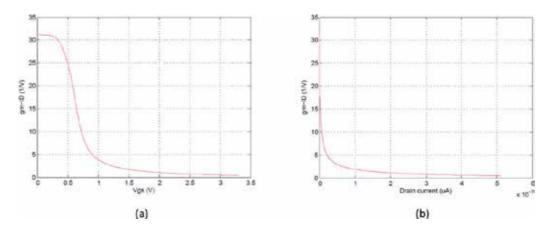

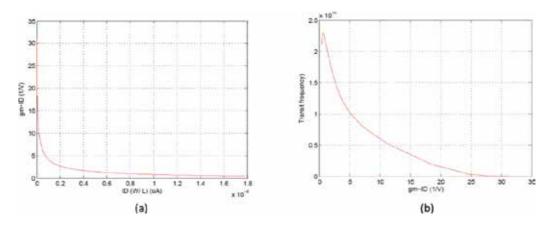

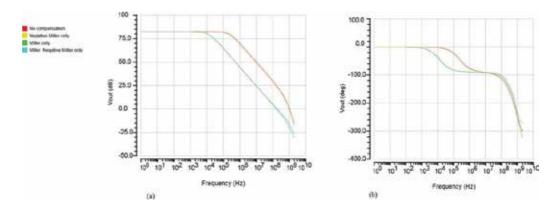

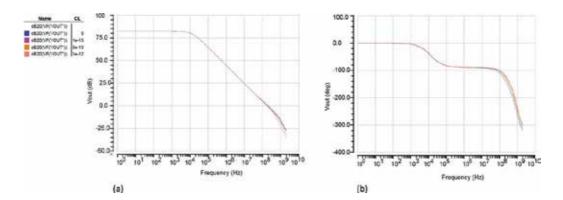

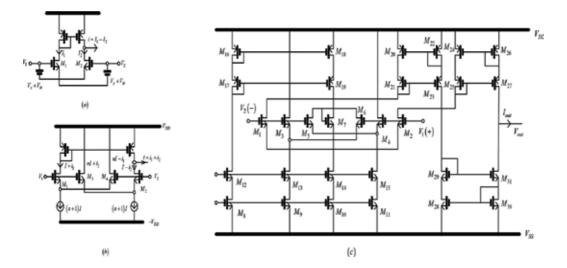

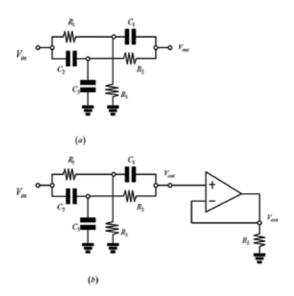

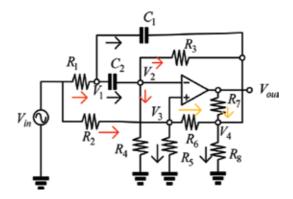

Transistor Degradations in Very Large-Scale-Integrated CMOS Technologies 31 http://dx.doi.org/10.5772/intechopen.68825