# IntechOpen

# **Field** Programmable Gate Array

Edited by George Dekoulis

# FIELD - PROGRAMMABLE GATE ARRAY

Edited by George Dekoulis

#### Field - Programmable Gate Array

http://dx.doi.org/10.5772/63664 Edited by George Dekoulis

#### Contributors

Ajay Singh, Miguel Angel Martínez Prado, Juvenal Rodríguez, Carlos Miguel Torres Hernández, Gilberto Herrera, Diana Carolina Toledo Pérez, Cristian Anghel, Cristian Stanciu, Constantin Paleologu, Alexandru Amaricai, Oana Boncalo, Nikhil Marriwala, O.P Sahu, Anil Vohra, Francesco Grancagnolo, Gianluigi CHIARELLO, Claudio CHIRI, Giuseppe COCCIOLO, Alessandro CORVAGLIA, Marco PANAREO, Aurora PEPINO, Giovanni TASSIELLI, Raffaele Giordano, Wen-Jyi Hwang, Chien-Min Ou, Steffen Mauch, Johann Reger, Jose Torres, Raimundo Garcia, Jesus Soret, Julio Martos, Nordin Aranzabal, Abraham Menendez, Pedro A. Martinez, Adrian Suarez, Gabriel Torrens

#### © The Editor(s) and the Author(s) 2017

The moral rights of the and the author(s) have been asserted.

All rights to the book as a whole are reserved by INTECH. The book as a whole (compilation) cannot be reproduced, distributed or used for commercial or non-commercial purposes without INTECH's written permission. Enquiries concerning the use of the book should be directed to INTECH rights and permissions department (permissions@intechopen.com).

Violations are liable to prosecution under the governing Copyright Law.

#### CC BY

Individual chapters of this publication are distributed under the terms of the Creative Commons Attribution 3.0 Unported License which permits commercial use, distribution and reproduction of the individual chapters, provided the original author(s) and source publication are appropriately acknowledged. If so indicated, certain images may not be included under the Creative Commons license. In such cases users will need to obtain permission from the license holder to reproduce the material. More details and guidelines concerning content reuse and adaptation can be foundat http://www.intechopen.com/copyright-policy.html.

#### Notice

Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published chapters. The publisher assumes no responsibility for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained in the book.

First published in Croatia, 2017 by INTECH d.o.o. eBook (PDF) Published by IN TECH d.o.o. Place and year of publication of eBook (PDF): Rijeka, 2019. IntechOpen is the global imprint of IN TECH d.o.o. Printed in Croatia

Legal deposit, Croatia: National and University Library in Zagreb

Additional hard and PDF copies can be obtained from orders@intechopen.com

Field - Programmable Gate Array Edited by George Dekoulis p. cm. Print ISBN 978-953-51-3207-3 Online ISBN 978-953-51-3208-0 eBook (PDF) ISBN 978-953-51-4819-7

# We are IntechOpen, the first native scientific publisher of Open Access books

3.350+ Open access books available

International authors and editors

108,000+ 115M+ Downloads

15Countries delivered to Our authors are among the

Top 1% most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science<sup>™</sup> Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# Meet the editor

Professor George Dekoulis received a first class BEng (Hons) in Communications Engineering from De Montfort University in Leicester, UK, in 2001. He joined the Space and Planetary Physics Group at Lancaster University in 2001. He has received several research awards from STFC, UK and EPSRC, UK and the "IET Hudswell International Research Scholarship". He was awarded a Ph.D in 2007 in Space Engineering and Communications. He is currently a professor in Aeronautical and Space Engineering at Aerospace Engineering Institute, Cyprus. He was a professor in Electrical and Electronics Engineering at Middle East Technical University, Turkey. He has worked as Research Associate in Space Engineering and Technical Support Engineer on Space Systems at Lancaster University, and as R & D Aerospace Systems Design Engineer for Electromech, UK. He is researching and developing Aerospace Engineering Systems using state-of-the-art all-digital technologies.

# Contents

### **Preface XI**

- Chapter 1 Efficient Hardware Architecture for Correlation-Based Spike Detection and Unsupervised Clustering 1 Chien-Min Ou and Wen-Jyi Hwang

- Chapter 2 Efficient FPGA Implementation of a CTC Turbo Decoder for WiMAX/LTE Mobile Systems 25 Cristian Anghel, Cristian Stanciu and Constantin Paleologu

- Chapter 3 **Motion Control with FPGA 57** Miguel Angel Martínez Prado, Juvenal Rodríguez Reséndiz, Diana Carolina Toledo Pérez, Carlos Miguel Torres Hernández and Gilberto Herrera Ruiz

- Chapter 4 FPGA-Based Software-Defined Radio and Its Real-Time Implementation Using NI-USRP 83 Nikhil Marriwala, Om. Prakash. Sahu and Anil Vohra

- Chapter 5 Design Trade-Offs for FPGA Implementation of LDPC Decoders 105 Alexandru Amaricai and Oana Boncalo

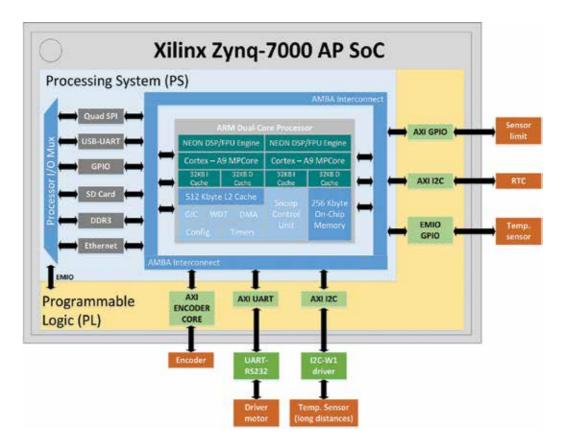

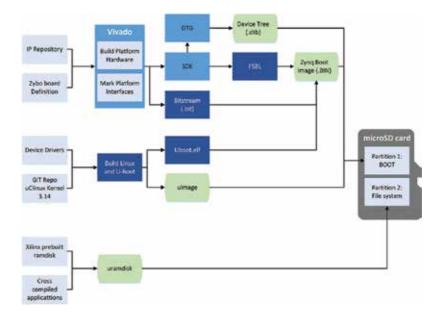

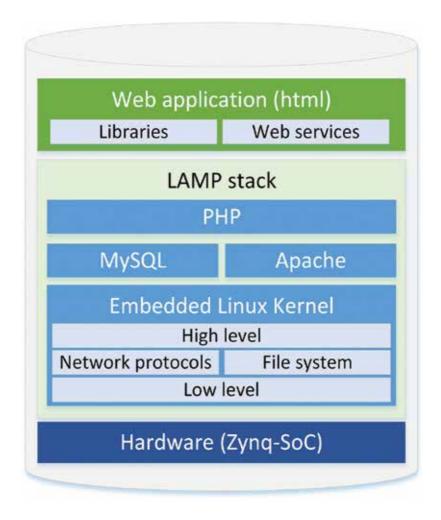

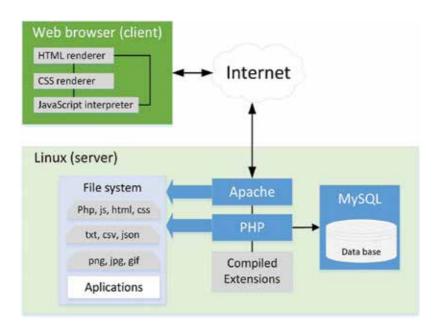

- Chapter 6 Design of Digital Advanced Systems Based on Programmable System on Chip 123

Nordin Aranzabal, Adrián Suárez, José Torres, Raimundo García-Olcina, Julio Martos, Jesús Soret, Abraham Menéndez and Pedro A. Martínez

| Chapter 7  | The Use of FPGA in Drift Chambers for High Energy Physics<br>Experiments 159<br>Gianluigi Chiarello, Claudio Chiri, Giuseppe Cocciolo, Alessandro<br>Corvaglia, Francesco Grancagnolo, Marco Panareo, Aurora Pepino<br>and Giovanni Francesco Tassielli |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 8  | <b>Real-Time Adaptive Optic System Using FPGAs 177</b><br>Steffen Mauch and Johann Reger                                                                                                                                                                |

| Chapter 9  | FPGA-SRAM Soft Error Radiation Hardening 197<br>Gabriel Torrens                                                                                                                                                                                         |

| Chapter 10 | Power Efficient Data-Aware SRAM Cell for SRAM-Based FPGA<br>Architecture 221<br>Ajay Kumar Singh                                                                                                                                                        |

| -          |                                                                                                                                                                                                                                                         |

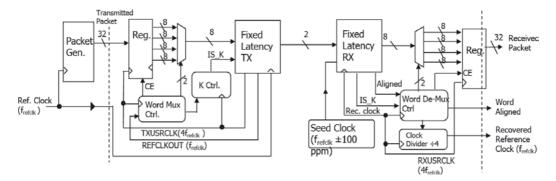

Chapter 11 High-Speed Deterministic-Latency Serial IO 249 Raffaele Giordano, Vincenzo Izzo and Alberto Aloisio

# Preface

This edited volume is a collection of reviewed and relevant research chapters, concerning the developments within the "Field-Programmable Gate Array" field of study. The book includes scholarly contributions by various authors and edited by a group of experts pertinent to semiconductors. Each contribution comes as a separate chapter completed within itself but directly related to the book's topics and objectives.

The book has 11 chapters.

The target audience comprises scholars and specialists in the field.

InTechOpen

# Efficient Hardware Architecture for Correlation-Based Spike Detection and Unsupervised Clustering

Chien-Min Ou and Wen-Jyi Hwang

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/66105

#### Abstract

This chapter presents a novel hardware architecture for correlation-based spike detection and unsupervised clustering. The architecture is able to utilize the information extracted from the results of spike clustering for efficient spike detection. The architecture supports the fast computation for the normalized correlation and OSORT operations. The normalized correlation is used for template matching for accurate spike detected spikes. The mean of spikes of each cluster produced by the OSORT algorithm is used as the templates for subsequent detection. The architecture adopts postnormalization technique for reducing the area costs. Modified OSORT operations are also proposed for facilitating unsupervised clustering by hardware. The proposed architecture is implemented by field programmable gate array (FPGA) for performance evaluation. In addition to attaining high detection and classification accuracy for spike sorting, experimental results reveal that the proposed architecture is an efficient design providing low area cost and high throughput for real-time offline spike sorting applications.

**Keywords:** spike sorting, spike detection, spike clustering, field programmable gate array, brain machine interface

# 1. Introduction

There is an increasing demand in data-acquisition systems for neurophysiology to record simultaneously from many channels over long time periods [1]. These experiments accumulate large amounts of data, which would be processed by spike sorting systems [2] for analyzing the activities of neurons. Atypical spike sorting system usually involves complicated spike detection

© 2017 The Author(s). Licensee InTech. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. and classification operations for separating spikes from background noise and clustering the detected spikes. Large amount of spike-trains would impose heavy computation load for a software spike sorting system, resulting in long processing time.

One approach to reduce the computation time is to implement a spike sorting system by hardware. A number of spike sorting systems based on field programmable gate array (FPGA) [3] have been proposed. In [4], a spike classification architecture using probabilistic neural networks [5] is proposed. Although high speed-up over its software counterpart is observed, the system does not provide spike detection. In addition, the architecture requires the user to input the number of clusters. Therefore, it does not support a fully unsupervised hardware classification. Similarly, the architecture proposed in [6] also focuses on the classification. The generalized Hebbian algorithm (GHA) [7] is implemented by FPGA in this work for feature extraction. The features produced by the architecture are then clustered by the k-means algorithm. The architecture does not include the hardware implementation of the k-means algorithm. In addition, the number of clusters still needs to be prespecified in the k-means algorithm. The architecture in [8] is able to carry out the feature extraction and clustering in hardware. In the architecture, the feature extraction and clustering are based on GHA and fuzzy c-means [9] algorithm, respectively. Therefore, similar to the architecture in [6], fully unsupervised classification is difficult for the architecture in [8] because the number of clusters still needs to be known beforehand.

An alternative FPGA-based hardware architecture [10] is to adopt OSORT algorithm [11] for spike-sorting. The OSORT algorithm is able to perform clustering without the prior knowledge of the number of clusters. Unsupervised classification therefore can be carried out. The architecture also includes a spike detection circuit based on the nonlinear energy operators (NEOs) [12], which is an energy-based detection algorithm. Similar to other energy-based algorithms [13, 14], the NEO algorithm is simple and effective. However, although the energy-based algorithms can operate in conjunction with a number of automatic threshold algorithms [12–14], proper selection of threshold values for these algorithms may still be difficult when noise becomes large. Therefore, their performance may deteriorate rapidly as noise energy increases.

The template-based spike detection algorithm may be suited for the detection of spikes from the source sequences with high noise level. A matched filter [15, 16] is a typical technique based on templates. To detect the presence of the templates, the filter correlates known templates with the input spike trains. This operation can also be viewed as a likelihood ratio detection (LRT) [17]. A drawback of the matched filter is that the templates are required. Although the adaptive generation of templates is possible [18], only a single template is produced for spike trains. However, because spike trains in general are formed from two or more neurons, a single template may not be sufficient for the detection of all the spikes generated by the neurons. The template-based algorithm presented by [19] has been found to be effective for the detection of noisy spikes. It adopts the OSORT algorithm for automatic template generation. Normalized correlation operations then carry out the spike detection using the templates produced by the OSORT algorithm. Nevertheless, in the algorithm, both the template generation and correlation computation have high computational complexities. The software implementation of the algorithm may not be suitable for fast analysis of spike trains.

The objective of this chapter is to present a novel FPGA-based hardware architecture for efficient spike detection and clustering. The architecture supports both the normalized correlation operations for spike detection and the OSORT operations for spike clustering. Moreover, the clustering results produced by the OSORT algorithm are used as the templates for spike detection. The architecture is the hardware implementation of the algorithm in [19]. It then has the advantages of accurate spike detection, fully unsupervised spike clustering, and fast computation.

We have implemented a spike sorting system on a network-on-chip (NOC) platform for the evaluation of the proposed architecture. The platform is based on FPGA. It consists of a soft-core processor [20] and the proposed architecture. The proposed spike sorting architecture is used as a hardware accelerator of the soft-core processor for spike sorting. The simulator developed in [21] is adopted to generate extracellular recordings. In this paper, comparisons with the existing software and hardware implementations are made. Experimental results show that the proposed architecture attains a high speed-up over its software counterpart for spike sorting. It also has a lower area cost over existing hardware architectures. Experimental results reveal that the proposed architecture is an effective alternative for real-time spike sorting with accurate detection and clustering.

## 2. The algorithm

Before presenting the hardware architectures for spike sorting, we first review the spike detection and clustering algorithms adopted by this work. Detailed discussions of these algorithms can be found in [19].

### 2.1. Normalized correlation

Consider a spike train **X**, where the *m*th sample of **X** is denoted by x[m]. Moreover, the *m*th segment of the spike train **X** is denoted by  $x_m = [x[m], x[m-1], ..., x[m-N+1]]^T$ , where *N* is the length of the segment. Suppose the spike train is processed by a matched filter with template  $t = [t[0], ..., t[N-1]]^T$ . Let  $\overline{\mathbf{x}}_m$  and  $\overline{\mathbf{t}}$  be the normalized version of  $\mathbf{x}_m$  and  $\mathbf{t}$ , respectively. That is,

$$\overline{\mathbf{x}}_m = \frac{\mathbf{x}_m}{\|\mathbf{x}_m\|}, \ \overline{\mathbf{t}} = \frac{\mathbf{t}}{\|\mathbf{t}\|}.$$

(1)

The normalized output at *m*, denoted by,  $\overline{y}[m]$ , is computed from

#### 4 Field - Programmable Gate Array

$$\overline{y}[m] = \sum_{k=0}^{N-1} \overline{x}[m-k]\overline{t}[k] = \overline{\mathbf{x}}_m^T \overline{\mathbf{t}}$$

(2)

This is the inner product of segment  $\overline{\mathbf{x}}_m$  and template  $\overline{\mathbf{t}}$ , which indicates the normalized correlation between these two vectors. The segment  $\mathbf{x}_m$  is detected as a spike when  $\overline{y}[m]$  is larger than a prespecified threshold  $\eta$ . Let  $d(\overline{\mathbf{x}}_m, \overline{\mathbf{t}})$  be the squared distance between  $\overline{\mathbf{x}}_m$  and  $\overline{\mathbf{t}}$ . It can be shown that

$$d(\bar{\mathbf{x}}_m, \bar{\mathbf{t}}) = 2 - 2\bar{\mathbf{x}}_m^T \bar{\mathbf{t}}.$$

(3)

Because  $d(\overline{\mathbf{x}}_m, \overline{\mathbf{t}}) \ge 0$ ,

$$\overline{\mathbf{x}}_m^T \overline{\mathbf{t}} \le 1. \tag{4}$$

Our normalized correlation operations are based on  $\overline{\mathbf{x}}_m$  and  $\overline{\mathbf{t}}$ . When  $\overline{\mathbf{x}}_m^T \overline{\mathbf{t}} \ge \eta$ , then  $\mathbf{x}_m$  is detected as a spike. From Eq. (4), it follows that

$$\eta \le 1$$

(5)

The normalized correlation operations shown in Eq. (2) may have high computational complexities. Although the template  $\overline{\mathbf{t}}$  can be computed beforehand, the computation of  $\overline{\mathbf{x}}_m$

still needs to be carried out online, involving the calculation of  $|\mathbf{x}_m|$  and  $\overline{\mathbf{x}}_m = \frac{\mathbf{x}_m}{||\mathbf{x}_m||}$ . Note

that *N* multiplications, *N*–1 additions, and one squared root operation are required for the computation of  $||\mathbf{x}_m||$ . Moreover, *N* divisions are needed for  $\overline{\mathbf{x}}_m$ . Finally, the inner product of

$\bar{\mathbf{x}}_m^T \bar{\mathbf{t}}$  requires *N* multiplications and *N*–1 additions. In total, the basic implementation of the normalized correlation operations requires 2*N* multiplications, (2*N*–2) additions, *N* divisions, and 1 squared root operation. When the fast computation is an important concern, the hardware implementation may then be desirable.

#### 2.2. OSORT algorithm

The OSORT algorithm is an unsupervised template-based clustering algorithm for spike sorting. It does not require feature extraction, and the number of clusters c is automatically

determined by the algorithm. Define  $C_{i'}i = 1, ..., c$ , as the clusters of spikes generated by the OSORT algorithm, where  $t_{i'}i = 1, ..., c$ , is the average value of the spikes belonging to  $C_i$ .

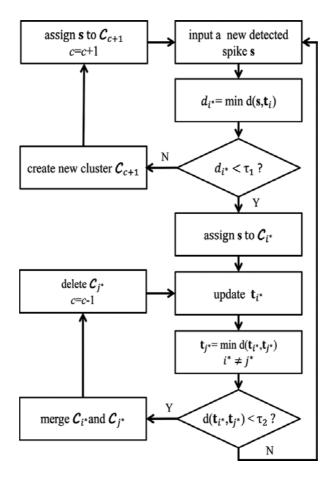

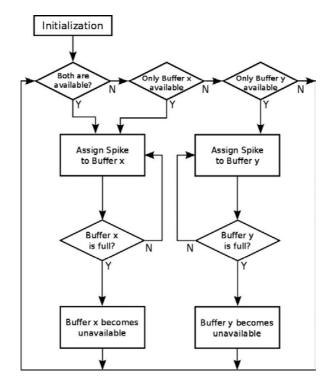

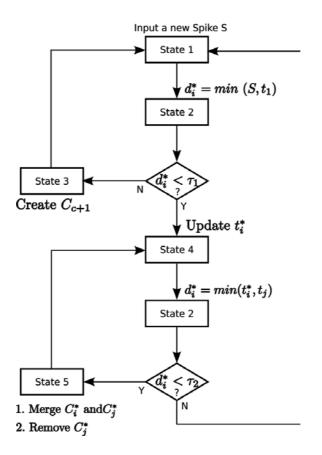

Given a current detected spike **s** for clustering, in the OSORT algorithm, the squared distances  $d_i = d(\mathbf{s}, \mathbf{t}_i)$  for i = 1, ..., c are first computed. The minimum distance  $d_{i^*}$  is then identified, where  $i^* = \arg \min_i d_i$ . We will assign **s** to  $C_{i^*}$  when  $d_{i^*}$  is less than a prespecified threshold  $\tau_1$ . In this case, because  $C_{i^*}$  has a new member, its mean value  $\mathbf{t}_{i^*}$  will also be updated. Otherwise, a new cluster is created, where **s** is its only member. After the updating of  $\mathbf{t}_{i^*}$ , the cluster merging process will be activated. The process involves the computation of the distance between  $\mathbf{t}_{i^*}$  and  $\mathbf{t}_{j'}$ ,  $i^* \neq j$ . Two clusters  $C_{i^*}$  and  $C_{j^*}$  will be merged when  $d(\mathbf{t}_{i^*}, \mathbf{t}_{j^*}) < \tau_{2'}$ , where  $j^* = \arg \min_{j, j \neq i^*} d(\mathbf{t}_{i^*}, \mathbf{t}_j)$ . Figure 1 summarizes the operations of the OSORT algorithm.

Figure 1. The flowchart of OSORT operations.

#### 2.3. Normalized correlation and OSORT algorithm for spike sorting

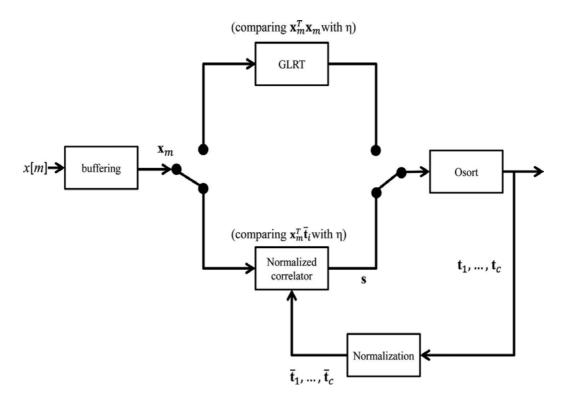

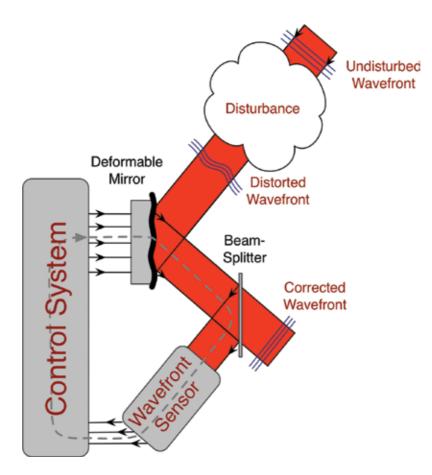

By combining the normalized correlation with the OSORT algorithm, an effective spike sorting system for both spike detection and classification can be realized. The system is a feedback system capable of automatic template generation for spike detection and unsupervised clustering for the classification. The block diagram of the system is revealed in **Figure 2**.

Figure 2. The block diagram of the spike detection/sorting system based on GLRT test, normalized correlator, and OSORT algorithms.

Initially, the clusters and templates produced by the OSORT are not available. As a result, it may be difficult to carry out the normalized correlation for spike detection. One way to solve this problem is to use only the block energy for the detection of spikes. The detected spikes are then clustered by the OSORT algorithm for the generation of initial templates.

After the templates become available, the spike detection is then based on the normalized correlation  $\bar{\mathbf{x}}_m^T \bar{\mathbf{t}}$ . The input block is detected as a spike when any of the c normalized correlation exceeds the threshold  $\eta$ . Because of the normalized correlation operations, the threshold value is bounded as shown in Eq. (5). Note that the templates for spike detection will be updated regularly so that the variations of input signals can be tracked to improve the spike detection performance.

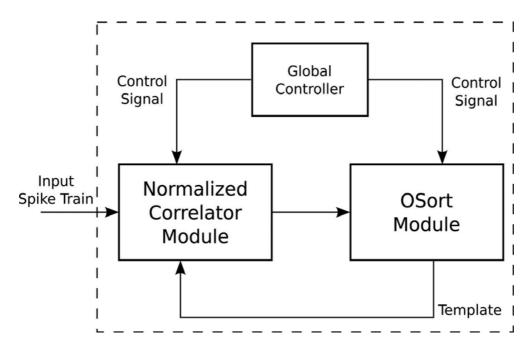

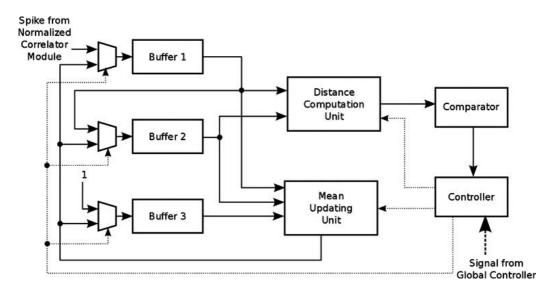

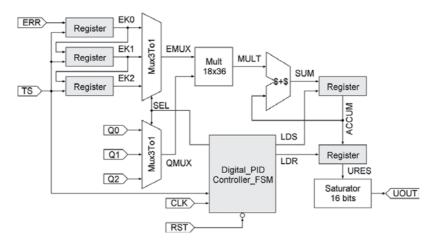

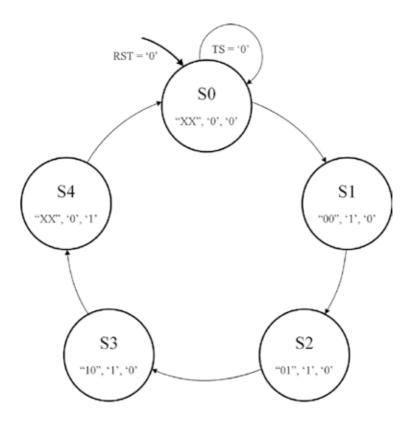

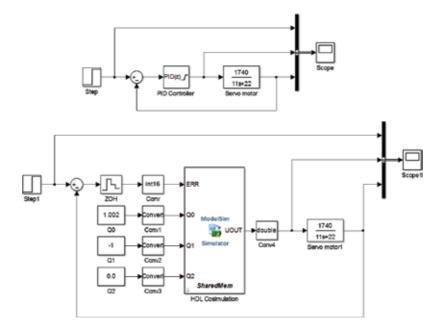

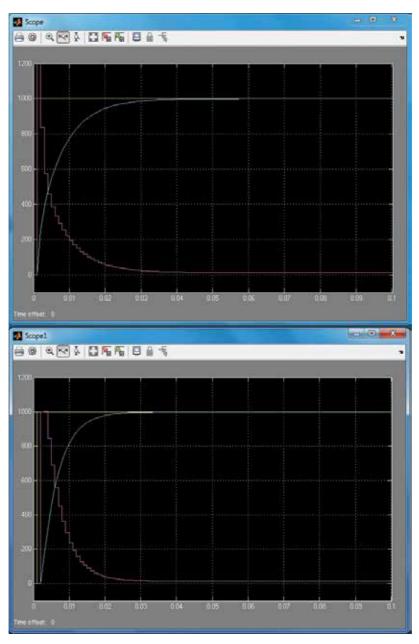

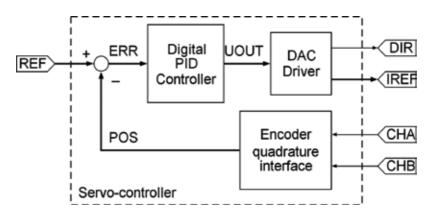

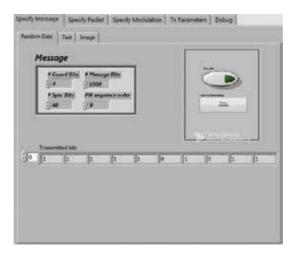

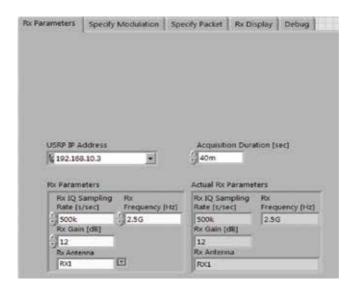

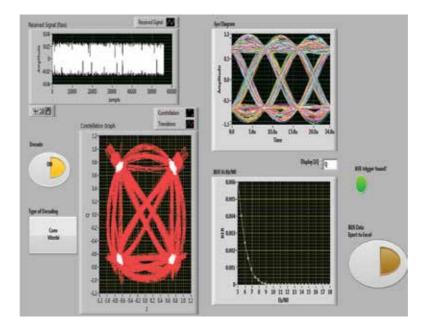

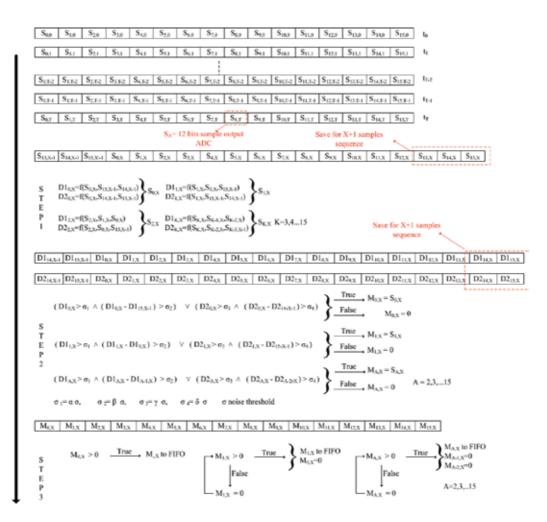

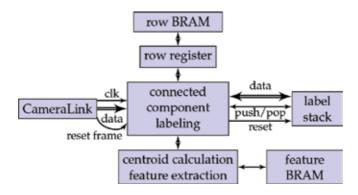

The hardware architecture for implementing the spike sorting system is depicted in **Figure 3**. The architecture contains two modules and one controller. The first module of the architecture, termed normalized correlator module, is responsible for the spike detection. It is capable of performing both the GLRT and normalized correlation operations. The second module, termed OSORT module, carries out the unsupervised OSORT spike sorting. The global controller coordinates the operations of these two modules. The architecture and detailed operations of the normalized correlator module and OSORT module are presented in the following two sections.

Figure 3. The hardware architecture of the proposed spike sorting system.

## 3. Architecture of the normalized correlator module

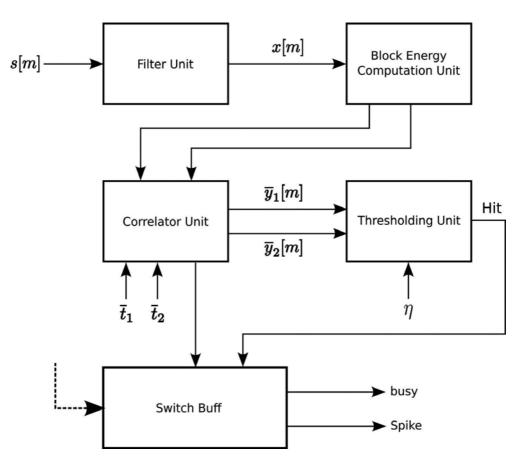

The block diagram of the normalized correlator module is revealed in **Figure 4**. The module supports the filtering, block energy computation, correlation computation, detection, and buffering. The filtering operation is the preprocessing step for the spike detection. It reduces the DC offset and noises. The objective of the block energy computation is to find  $||\mathbf{x}_m||^2$ , which is then followed by correlation computation for calculating  $\mathbf{\bar{x}}_m^T \mathbf{\bar{t}}$ . The detection results are then produced by the comparison operations. The detected spikes are stored in the switch buffer, which can be accessed by the OSORT module for subsequent clustering operations. Without loss of generality, the length of spike is set to be N = 64 for our discussion.

Figure 4. The block diagram of the normalized correlator module.

#### 3.1. Filter unit and block energy computation unit

The filter unit is a hardware implementation of a band-pass Butterworth filter. The filter unit contains multipliers, shift registers, and adders. The architecture is a simple realization of the direct form I of IIR filters. To implement the block energy computation unit, we first note that a basic approach may involve *N* multiplications for the energy computation, resulting in high-area costs. The proposed approach is based on the fact that

$$\|\mathbf{x}_{m}\|^{2} = \|\mathbf{x}_{m-1}\|^{2} + x^{2}[m] - x^{2}[m-N].$$

(6)

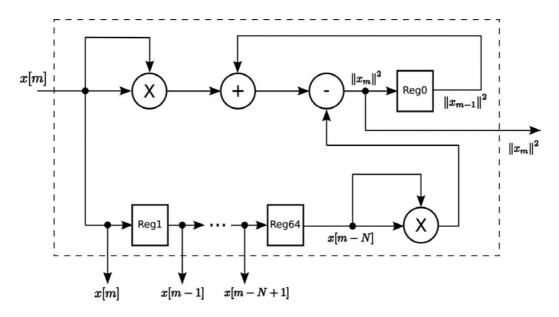

Consequently, the calculation of  $||\mathbf{x}_m||^2$  needs only two multiplications. This is because  $||\mathbf{x}_{m-1}||^2$  (i.e., the block energy of the previous block) is already available. **Figure 5** shows the resulting design, which contains two multiplier, a single *N*-stage shift register, and two adders. The goal of the shift register is to store the previous samples (i.e., x[k], k = m - 1, ..., m - N) of

x[m]. The shift register therefore is able to offer the sample x[m - N] for the calculation of  $x^2[m - N]$ . In addition, the shift register can be employed for the correlation computation.

Figure 5. Architecture of block energy computation unit.

#### 3.2. Correlator unit

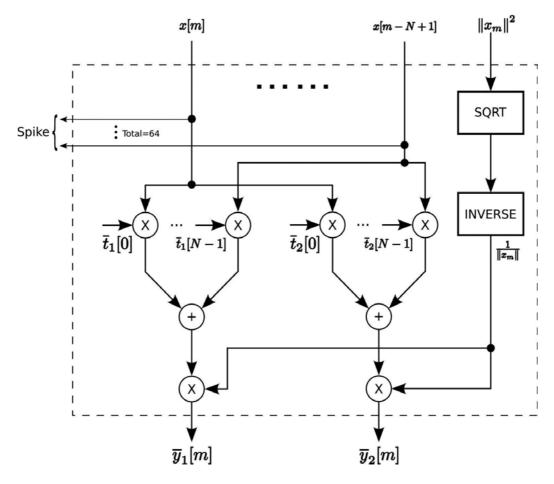

The goal of the unit is to carry out the normalized correlation  $\overline{\mathbf{x}}_m^T \overline{\mathbf{t}}$ . Note that the normalized template  $\overline{\mathbf{t}}$  can be obtained offline from the OSORT circuit. Therefore, it is only necessary to find  $\overline{\mathbf{x}}_m$  online. One simple approach to compute  $\overline{\mathbf{x}}_m$  is to divide each sample of  $\mathbf{x}_m$  by  $||\mathbf{x}_m||$ . Because the block  $\mathbf{x}_m$  contains *N* samples, *N* dividers are required. In the proposed architecture, a novel postnormalization approach is employed, where the inner product  $\mathbf{x}_m^T \overline{\mathbf{t}}$  is computed first. Because  $\mathbf{x}_m^T \overline{\mathbf{t}}$  is a scalar, we can then use only one divider to compute  $\overline{\mathbf{x}}_m^T \overline{\mathbf{t}}$  by dividing  $\mathbf{x}_m^T \overline{\mathbf{t}}$  by  $||\mathbf{x}_m||$ .

**Figure 6** shows the architecture of the correlator unit for the case of two templates. The circuit consists of 2*N* multipliers, one squared root circuit, two accumulators, and one divider. Moreover, there are two registers for storing the normalized templates  $\bar{\mathbf{t}}_1$  and  $\bar{\mathbf{t}}_2$ . Recall that the shift register in the block energy computation unit contains the samples of  $\mathbf{x}_m$ . Based on  $\mathbf{x}_m$  and  $\bar{\mathbf{t}}_{i'}$  i = 1, 2, the computation of each  $\mathbf{x}_m^T \bar{\mathbf{t}}_{i'}$  i = 1, 2, is carried out in parallel. Moreover, the multiplication results are accumulated in a pipelined fashion. The accumulation results are then scaled by a factor of  $1/||\mathbf{x}_m||$ . Because the block energy computation unit provides

$||\mathbf{x}_m||^2$ , only a squared root circuit and an inverse circuit are needed for the calculation of  $1/||\mathbf{x}_m||$ , as shown in **Figure 6**.

Figure 6. Architecture of correlator unit.

#### 3.3. Threshold unit

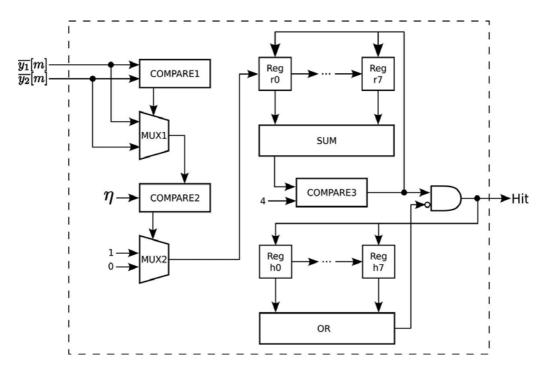

Although the operations of the unit can be easily accomplished by a simple comparison circuit, the detection accuracy may be further improved by taking the detection results of the neighboring blocks into consideration. Because the neighboring blocks are overlapping, they may be similar. As a result, the normalized correlation values of the neighboring blocks may also be similar. Therefore, it is likely that an occurrence of a single spike may result in the issues of multiple hits.

To solve this problem, when the normalized correlation value of a block is above the threshold, a hit is not immediately declared. The architecture will then examine the normalized

correlation values of the previous blocks. A hit would actually be issued only if *k* out of *K* preceding blocks have normalized correlation values above a threshold. In this way, the false alarm rate (FAR) can be effectively lowered. **Figure 7** shows the corresponding architecture, which contains a *K*-stage shift register storing the comparison results of the *K* previous blocks. Each stage of the shift register contains only a single-bit information, where 1 indicates that the corresponding block has normalized correlation value above the threshold  $\eta$ , and 0 otherwise. Therefore, if the sum of all the *K* stages is larger or equal to *k*, then at least *k* preceding blocks have normalized correlation value above the threshold. In this case, the architecture issues a hit.

Figure 7. Architecture of threshold unit.

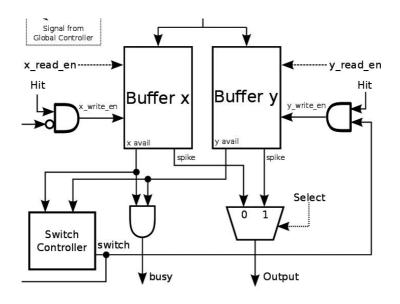

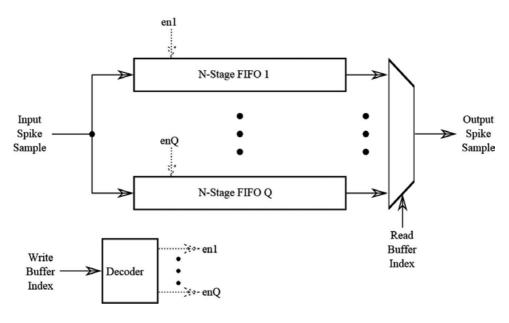

#### 3.4. Switch buffer

The goal of switch buffer is to store the detected spikes for subsequent clustering operations. As shown in **Figure 8**, there are two buffers (denoted as Buffer x and Buffer y) in the circuit. When one of the buffers stores the detected spikes, the other provides the detected spikes to the OSORT module for clustering operations. The switch controller in the circuit is responsible for the determination of the buffer to store the detected spikes. The flowchart of the operations of the switch controller is shown in **Figure 9**. From the flowchart, it can be observed that the controller assigns the detected spikes to a buffer in accordance with the availability of that buffer. A buffer is available when it has empty cells for storing new detected spikes, and is not currently providing spikes to the OSORT module.

Figure 8. Architecture of switch buffer.

Figure 9. Flowchart of switch controller.

# 4. The architecture of OSORT module

The OSORT module contains buffers, distance computation unit, mean updating unit, comparator, and controller, as shown in **Figure 10**. The centroid and the size of each cluster are stored in the buffers. The distance computation unit and mean updating unit are responsible for squared distance computation and the updating of centroid of the clusters, respectively. The control unit coordinates different components of the OSORT module for carrying out the unsupervised clustering operations.

Figure 10. Architecture of OSORT module.

#### 4.1. Buffers

There are three buffers in the OSORT module, which are denoted by Buffer 1, Buffer 2, and Buffer 3, respectively. Buffer 1 holds an input spike detected by the correlators. Buffers 2 and 3 contain the mean value and size of each cluster, respectively. Buffer 1 is a simple *N*-stage shift register, fetching or delivering one sample of the input spike at a time. As shown in **Figure 11**, Buffer 2 contains *QN*-stage shift registers. Each shift register holds the mean value of a cluster. Therefore, *Q* is the upper-bound of the number of clusters. Buffer 2 updates or provides mean values of clusters one at a time. Because the mean value  $t_i$  of a cluster  $C_i$  is the average value of the spikes mapping to that cluster, the mean value also contains *N* samples. Accessing the mean value of the cluster is also carried out one sample at a time. Buffer 3 records the size of each cluster. There are *Q* entries in the buffer. The *i*th entry contains the number of spikes in the cluster  $C_i$ .

Figure 11. Architecture of Buffer 2.

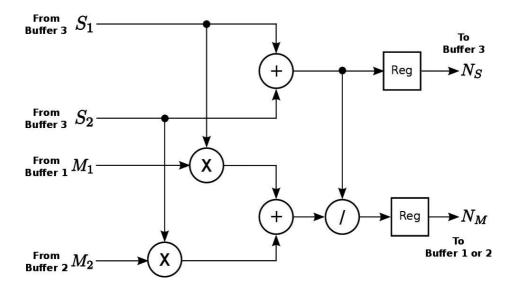

#### 4.2. Distance computation unit and mean updating unit

Because buffers in the memory unit can be accessed one sample at a time, the circuits in the distance computation unit and mean updating unit provide only sample-wise computations. This is beneficial for reducing the area costs. There are two cases when the distance computation unit needs to be activated. In the first case, a new spike is arrived. To find the cluster for the new spike, the squared distance computation is required. In the second case, it is desired to merge two clusters. The squared distance calculation is needed for finding the closest clusters. The distance computation unit takes the samples fetched from Buffer 1 and Buffer 2 as inputs. The unit finds the squared distance between the spikes stored in Buffer 1 and the mean value of a cluster selected in Buffer 2. Upon the completion of the squared distance computation, the comparison of the new squared distance with the current minimum distance stored in a register of the unit is carried out. If the new squared distance is smaller than the current minimum distance, then it becomes the new current minimum distance. The same squared distance computation and comparison operations will be repeated for until all the mean values in Buffer 2 are searched. This scheme is useful for finding the best matching mean value stored in Buffer 2 to the spike stored in Buffer 1.

The mean updating unit is activated after a new spike is assigned to a cluster, or after two clusters are merged. In these cases, the mean of the updated cluster needs to be computed. Note that the clusters to be updated are determined by the distance computation unit. The mean updating unit is only responsible for the computation of the new mean of the updated clusters. The circuit takes waveforms stored in Buffer 1 and Buffer 2, and the cluster size stored

in Buffer 3 as inputs. The updated mean is the weighted sum of the waveforms obtained from Buffer 1 and Buffer 2, as shown in **Figure 12**. The weights are determined from the cluster sizes from Buffer 3. The updated results are then stored back to Buffer 2 and Buffer 3.

Figure 12. Architecture of mean updating unit.

#### 4.3. Control unit

The control unit activates components of the memory unit and cluster computation unit for the unsupervised clustering. The states of the control unit are summarized in **Table 1**. In addition to the tasks carried out by each state, the activated circuit components associated with each state are also included in the table. **Figure 13** shows the flowchart of the OSORT algorithm in terms of the states defined in **Table 1**.

| States  | States Activated components Operations |                                                         |  |

|---------|----------------------------------------|---------------------------------------------------------|--|

| State 1 | Buffer 1                               | Fetch a new spike to Buffer 1                           |  |

|         | Distance computation unit              |                                                         |  |

| State 2 | Buffers 1, 2                           | Find the best matching cluster to the spike in Buffer 1 |  |

| State 3 | Buffers 1, 2, 3                        | Creating a new cluster                                  |  |

| State 4 | Buffers 1, 2, 3                        | Update the mean and size of a cluster                   |  |

|         | Mean updating unit                     |                                                         |  |

| State 5 | Buffers 2, 3                           | Remove a cluster                                        |  |

Table 1. States of the control unit in OSORT module.

Figure 13. The flowchart of the controller in the OSORT module.

The flowchart in **Figure 13** is consistent with that shown in **Figure 1**. Although the combinations of the states shown in **Table 1** are able to implement the OSORT algorithm, additional modifications may still be desirable to facilitate the hardware implementation. One modification implemented in the controller is to handle the cases when the current number of clusters reaches the upper limit *Q*, and the creation of new cluster is still desired. In this case, the least recently updated cluster will be replaced by the new cluster. To carry out this modification, an additional field is added to each entry of Buffer 3. The entry indicates the number of updates in the past for the corresponding cluster. This modification can be viewed as an additional function supported in State 3 in **Table 1** for the creation of a new cluster.

### 5. Global controller and NOC

As depicted in **Figure 3**, the global controller in the proposed spike sorting system coordinates the operations of the normalized correlator module and OSORT module. The major goal of the global controller is to fetch detected spikes from the normalized correlator module and

deliver them to the OSORT module. When a buffer in the switch buffer of the normalized correlator module becomes full, the global controller starts to fetch the detected spikes one at a time from the buffer to the OSORT module.

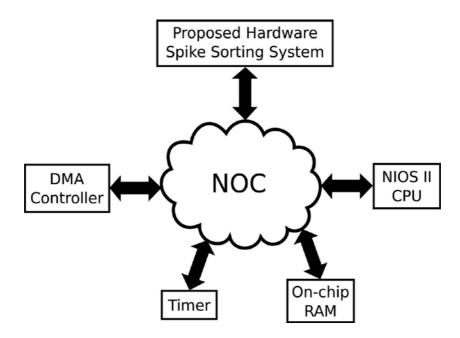

The fetching operations are repeated until all the spikes stored in the buffer are fetched. At this time, the buffer becomes available again for storing the new detected spikes, as shown in **Figure 14**. The proposed hardware spike sorting system is configured as a user component in a NOC system, which is designed by the QSYS platform. In addition to the proposed system, we see from **Figure 15** that the NOC contains the NIOS II processor, a DMA controller, an on-chip RAM, and a hardware timer.

Figure 14. The flowchart of the global controller.

The raw spike trains are stored in the on-chip RAM. The DMA controller is responsible for delivering the spike trains to the proposed hardware system without the intervention of the NIOS II processor. The DMA controller is able to halt the delivery of spike trains automatically when both buffers in the switch buffer of the normalized correlator module are unavailable and/or full. The hardware timer is used to measure the computation speed of the proposed system. The NIOS II processor integrates different components in the NOC. It activates the DMA controllers for the delivery of spike trains. After that, the processor collects the spike sorting results from the OSORT modules of the proposed spike sorting system. The processor is also able to read the information provided by the hardware timer for the measurement of the computation speed of the proposed circuit.

Figure 15. The proposed NOC system for spike sorting.

## 6. Experimental results

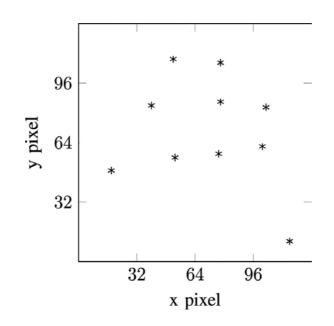

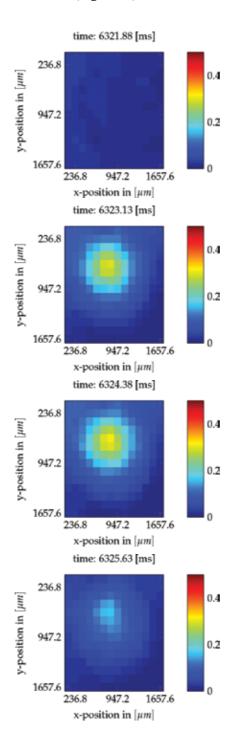

This section presents some experimental results of the proposed architecture. The extracellular recordings for the experiments are based on the simulator developed in [21], where the ground truth about spiking activity can be accessed. Each spike has length 2.67 ms. The sampling rate for the spike recording is 24,000 samples/s. Therefore, there are 64 samples (i.e., N = 64) in each spike.

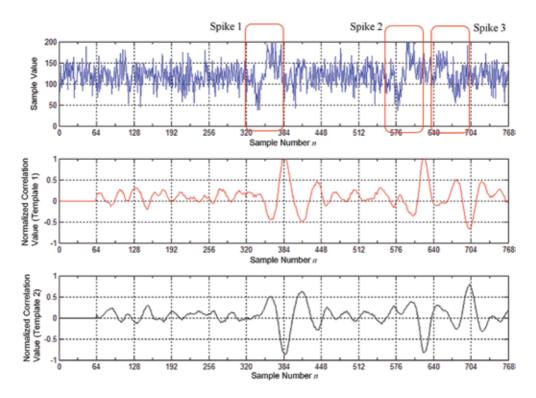

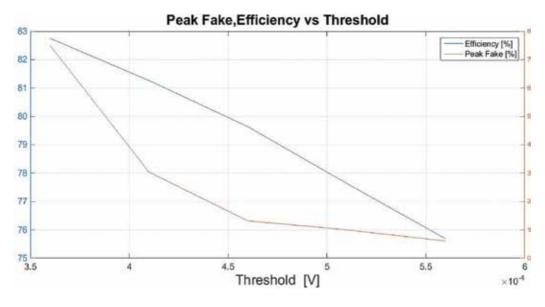

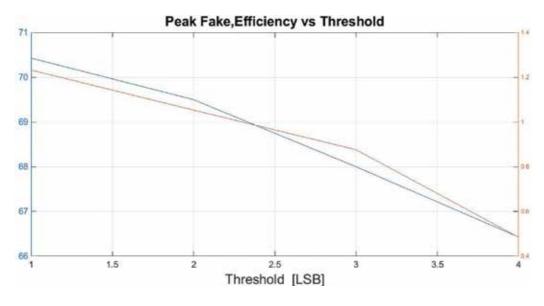

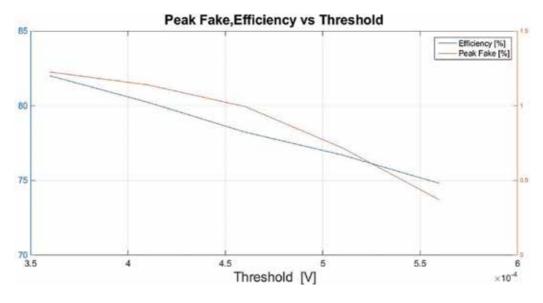

The performance of the proposed architecture for spike detection is first evaluated. The performance evaluation is based on the true positive rate (TPR) and false alarm rate (FAR). The TPR of a detection algorithm is defined as the number of true spikes detected by the algorithm divided by the total number of true spikes. The FAR of a detection algorithm is the number of silent segments, which are falsely detected as spikes by the algorithm, divided by the total number of the segments detected by the algorithm. The TPR and FAR of various detection algorithms are included in **Table 2**. In the experiments, the spike trains are from two neurons. Therefore, there are two templates (i.e., c = 2) for the proposed normalized correlator.

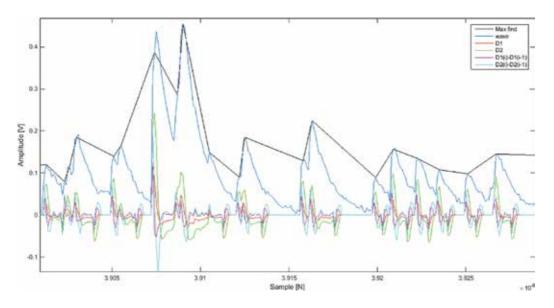

Because the normalized correlation is effective for detecting real spikes and ignoring silent segments, we can observe from **Table 2** that the proposed architecture has superior performance over the other algorithms. We use the example shown in **Figure 16** to further demonstrate this fact. In the example, a noisy spike train with SNR = -3 dB is used for the spike detection. **Figure 16** reveals the normalized correlation values  $\bar{y}_i[m]$ , i = 1, 2, for the spike train. From

| SNR (dB) |     | Normalized | Noncoherent energy | NEO    | SWT    | Matched     |

|----------|-----|------------|--------------------|--------|--------|-------------|

|          |     | correlator | detector [17]      | [12]   | [22]   | filter [16] |

| 10       | TPR | 93.64%     | 91.37%             | 93.10% | 94.82% | 89.65%      |

|          | FAR | 0.40%      | 5.35%              | 3.57%  | 6.77%  | 2.80%       |

| 1        | TPR | 90.04%     | 88.03%             | 87.21% | 92.43% | 82.90%      |

|          | FAR | 0.92%      | 6.36%              | 22.49% | 79.36% | 3.02%       |

| -3       | TPR | 82.71%     | 82.60%             | 80.53% | 86.66% | 80.31%      |

|          | FAR | 1.06%      | 9.52%              | 57.87% | 82.43% | 8.92%       |

**Figure 16**, we see that, because of large noise corruption, it is difficult to locate spikes even by direct eye inspection. However, based on the normalized correlation values provided by the proposed architecture, the location of true spikes can still be effectively identified.

Table 2. TPR and FAR values of various spike detection algorithms.

**Figure 16.** An example of the proposed normalized correlator for noisy spike detection with SNR = -3 dB for c = 2 templates.

Next we evaluate the area complexities. Because adders, multipliers, dividers, comparators, and registers are the basic building blocks of the proposed architecture, the area complexities

are separated into five types: the number of adders, multipliers, dividers, comparators, and registers. **Tables 3** and **4** show the area complexities of the normalized correlator and OSORT modules, respectively. It can be observed from **Table 3** that, in the normalized correlator module, the correlator unit and switch buffer have larger area complexities. The number of adders, multipliers, and registers grows with the block dimension N and the number of templates c in the correlator unit. Let L be the capacity (i.e., the maximum number of spikes) of each buffer in the switch buffer. The number of registers in the switch buffer therefore is dependent on L and N, as shown in **Table 3**. The area complexities of the other types are of O(1). Therefore, the proposed circuit has low consumption of dividers and comparators. From **Table 4**, we observe that only the area complexities of the buffers in the OSORT module grow with N. The other parts of the OSORT module have fixed area complexities.

|             | Filter unit  | Block energy computation | Correlator | Thresholding unit | Switch buffer | Subtotal     |

|-------------|--------------|--------------------------|------------|-------------------|---------------|--------------|

| Adders      | O(1)         | O(1)                     | O(cN)      | <i>O</i> (1)      | 0             | O(cN)        |

| Multipliers | <i>O</i> (1) | <i>O</i> (1)             | O(cN)      | <i>O</i> (1)      | 0             | O(cN)        |

| Dividers    | 0            | 0                        | 1          | 0                 | 0             | 1            |

| Comparators | 0            | 0                        | 0          | <i>O</i> (1)      | 0             | <i>O</i> (1) |

| Registers   | <i>O</i> (1) | O(N)                     | O(cN)      | <i>O</i> (1)      | O(LN)         | O(cN + LN)   |

Table 3. Area complexities of the normalized correlator module.

|             | Buffer | Distance computation | Mean          | Subtotal     |  |

|-------------|--------|----------------------|---------------|--------------|--|

|             |        | unit                 | updating unit |              |  |

| Adders      | 0      | O(1)                 | O(1)          | O(1)         |  |

| Multipliers | 0      | <i>O</i> (1)         | <i>O</i> (1)  | <i>O</i> (1) |  |

| Dividers    | 0      | 0                    | <i>O</i> (1)  | <i>O</i> (1) |  |

| Comparators | 0      | <i>O</i> (1)         | 0             | <i>O</i> (1) |  |

| Registers   | O(cN)  | O(1)                 | <i>O</i> (1)  | O(cN)        |  |

Table 4. Area complexities of the OSORT module.

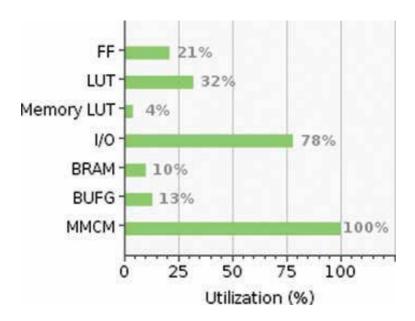

The proposed architecture has been implemented by FPGA for performance measurement. The target FPGA device for the hardware implementation is Altera STRATIX IV EP4SGX230. The design platform for the experiments is the Altera QUARTUS II with QSYS. **Table 5** shows the hardware utilization of the proposed architecture. There are four different FPGA hardware resources considered: adaptive look-up tables (ALUTs), dedicated logic registers, block memory bits, and DSP blocks. The DSP blocks are dedicated to the implementations of adders, multipliers, dividers, and comparators. The ALUTs, dedicated logic registers, and block memory bits can be used for the implementation of registers, as well as adders, multipliers, dividers, It can be observed from **Table 5** that the consumption of DSP blocks of normalized correlator is higher than that of the OSORT module. This is because the

normalized correlator requires more number of arithmetic operators. There are 182,400 ALUTs, 182,400 dedicated logic registers, 1288 DSP blocks, and 14,625,792 block memory bits in the target FPGA device. It can be observed from **Table 5** that only limited hardware resources are consumed by the proposed circuit.

|                              | ALUTs                      | Dedicated                  | Block                     | DSP blocks           |

|------------------------------|----------------------------|----------------------------|---------------------------|----------------------|

|                              |                            | logic registers            | memory bits               |                      |

| Normalized correlator module | 13,966                     | 29,733                     | 0                         | 532                  |

| OSORT module                 | 22,604                     | 22,562                     | 320                       | 88                   |

| Total                        | 39,355/182,400<br>(21.57%) | 52,517/182,400<br>(28.79%) | 320/14,625,792<br>(<0.1%) | 642/1288<br>(49.84%) |

**Table 5.** The utilization of FPGA resources of the proposed circuit. The switch buffer capacity for the measurement is L = 40.

In addition to consuming low hardware resources, the proposed architecture is able to provide high throughput. **Table 6** reveals the throughput of the proposed architecture for various clock rates and switch buffer size *L*. The throughput is defined as the number of spike samples which can be processed by the proposed architecture per second. The unit of the throughput in the table therefore is mega samples per second (Msamples/sec). It can be observed from **Table 6** that the throughput grows with *L* and/or clock rate. In particular, when L = 32 and clock rate is 100 MHz, the throughput is 25.04 Msamples/sec. The throughput of its software counterpart running on Intel I7-930 processor at clock rate 2.8 GHz and 16 GB RAM is only 0.69 Msamples/ sec. The throughput of the proposed architecture therefore is 36 times higher than that of its software counterpart.

| Clock rate | <i>L</i> = 20 | <i>L</i> = 40 | L = 80       |  |

|------------|---------------|---------------|--------------|--|

| 50 MHz     | 9.22          | 10.25         | 13.31        |  |

|            | Msamples/sec  | Msamples/sec  | Msamples/sec |  |

| 75 MHz     | 13.00         | 15.34         | 20.00        |  |

|            | Msamples/sec  | Msamples/sec  | Msamples/sec |  |

| 100 MHz    | 17.80         | 20.25         | 25.04        |  |

|            | Msamples/sec  | Msamples/sec  | Msamples/sec |  |

Table 6. The throughput of the proposed circuit for various clock rates and switch buffer capacities L.

# 7. Concluding remarks

The proposed architecture has been found to be effective for real-time spike sorting. It features high accuracy, low hardware resource consumption, and high throughput. The combination of the normalized correlation and OSORT algorithm is beneficial for accurate spike detection with high TPR and low FAR even for low SNR values. The postnormalization approach

adopted by the normalized correlator circuit is also able to reduce the area costs for the normalization operations. In addition, the switch buffer in the correlation circuit can effectively coordinate the operations of spike detection and classification for achieving high throughput. Experimental results reveal that the proposed architecture achieves TPR = 82.71% and FAR = 1.06% for SNR = -3 dB. The ALUT consumption is only 21.57% for the FPGA device STRUTIX IV EP4SGX230. The throughput is 25.04 Msamples/sec for the clock rate 100 MHz. All these facts demonstrate the effectiveness of the proposed architecture.

## Acknowledgements

The authors would like to acknowledge the financial support of the Ministry of Science and Technology, Taiwan, under grant MOST 105-2221-E-003-011-MY2.

## Author details

Chien-Min Ou<sup>1</sup> and Wen-Jyi Hwang<sup>2\*</sup>

\*Address all correspondence to: whwang@csie.ntnu.edu.tw

1 Department of Electronics Engineering, Chien-Hsin University of Science and Technology, Taoyuan, Taiwan

2 Department of Computer Science and Information Engineering, National Taiwan Normal University, Taipei, Taiwan

### References

- Einevoll, G. T.; Franke, F.; Hagen, E.; Pouzat, C.; Harris, K. D. Towards reliable spiketrain recordings from thousands of neurons with multielectrodes, Current Opinion in Neurobiology 2012, 22, 11–17.

- [2] Gibson, S.; Judy, J. W.; Markovic, D. Spike sorting: the first step in decoding the brain, IEEE Signal Processing Magazine 2012, 29, 124–143.

- [3] Hauck, S.; Dehon, A. Reconfigurable Computing: The Theory and Practice of FPGA-Based Computing, Morgan Kaufmann: San Francisco, CA, USA, 2008.

- [4] Zhu, X.; Yuan, L.; Wang, D.; Chen, Y. FPGA implementation of a probabilistic neural network for spike sorting. In Proceeding of the IEEE International Conference on Information Engineering and Computer Science, Piscataway, New Jersey, USA. 2010; pp. 26–29.

- [5] Dutta, K.; Prakash, N.; Kaushik, S. Probabilistic neural network approach to the classification of demonstrative pronouns for indirect anaphora in Hindi. Expert Systems with Applications 2010, 37, 5607–5613.

- [6] Yu, B.; Mak, T.; Li, X.; Xia, F.; Yakovlev, A.; Sun, Y.; Poon, C.S. A reconfigurable Hebbian eigenfilter for neurophysiological spike train analysis. In Proceedings of the IEEE International Conference on Field Programmable Logic and Applications, Piscataway, New Jersey, USA. 2010; pp. 556–561.

- [7] Haykin, S. Neural Networks and Learning Machines, 3rd ed.; Pearson: Upper Saddle River, NJ, USA, 2009.

- [8] Hwang, W. J.; Lee, W. H.; Lin, S. J.; Lai, S. Y. Efficient architecture for spike sorting in reconfigurable hardware, Sensors 2013, 13, 14860–14887.

- [9] Miyamoto, S.; Ichihashi, H.; Honda, K. Algorithms for Fuzzy Clustering, Springer: Berlin/Heidelberg, Germany, 2010.

- [10] Gibson, S.; Judy, J. W.;Markovic, D. An FPGA-based platform for accelerated offline spike sorting, Journal of Neuroscience Methods 2013, 215, 1–11.

- [11] Rutishauser, U. Online detection and sorting of extracellularly recorded action potentials in human medial temporal lobe recordings, in vivo, Journal of Neuroscience Methods 2006, 154, 204–224.

- [12] Mukhopadhyay, S.; Ray, G. C. A new interpretation of nonlinear energy operator and its efficacy in spike detection, IEEE Transactions on Biomedical Engineering 1998, 45, 180–187.

- [13] Quiroga, R. Q.; Nadasdy, Z.; Ben-Shaul, Y. Unsupervised spike detection and sorting with wavelets and superparamagnetic clustering, Neural Computation 2004, 16, 1661– 1687.

- [14] Gibson, S.; Judy, J. W.; Markovic, D. Technology-aware algorithm design for neural spike detection, feature extraction, and dimensionality reduction, IEEE Transactions on Neural Systems and Rehabilitation Engineering 2010, 18, 469–478.

- [15] Mtetwa, N.; Smith, L. S. Smoothing and thresholding in neuronal spike detection, Neurocomputing 2006, 69, 1366–1370.

- [16] Sato, T.; Suzuki, T.; Mabuchi, K. Fast template matching for spike sorting, Electronics and Communications in Japan 2009, 92, 57–63.

- [17] Oweiss, K.; Aghagolzadeh, M. Detection and classification of extracellular \*\*\*action potential recordings, Chapter 2 of Statistical Signal Processing for Neuroscience, Academic Press, Tokyo., pp.15–74, 2010.

- [18] Kim, S.; McNames, J. Automatic spike detection based on adaptive template matching for extracellular neural recordings, Journal of Neuroscience Methods 2007, 165, 165– 174.

- [19] Hwang, W. J.; Wang, S. H.; Hsu, Y. T. Spike detection based on normalized correlation with automatic template generation, Sensors 2014, 14, 11049–11069.

- [20] NIOS II Processor Reference Handbook; Altera Corporation: San Jose, CA, USA, 2015. Available online: http://www.altera.com/literature/lit-nio2.jsp (accessed on 8 April 2015).

- [21] Smith, L. S.; Mtetwa, N. A tool for synthesizing spike trains with realistic interference. Journal of Neuroscience Methods 2007, 159, 170–180.

- [22] Kim K.; Kim, S. A wavelet-based method for action potential detection from extracellular neural signal recording with low signal-to-noise ratio, IEEE Transactions on Biomedical Engineering 2003, 50, 999–1011.

# Efficient FPGA Implementation of a CTC Turbo Decoder for WiMAX/LTE Mobile Systems

Cristian Anghel, Cristian Stanciu and

Constantin Paleologu

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/67017

#### Abstract

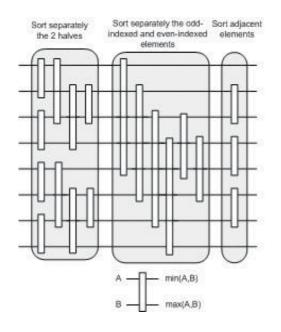

This chapter describes the implementation on field programmable gate array (FPGA) of a turbo decoder for 3GPP long-term evolution (LTE) standard, respectively, for IEEE 802.16-based WiMAX systems. We initially present the serial decoding architectures for the two systems. The same approach is used; although for WiMAX the scheme implements a duo-binary code, while for LTE a binary code is included. The proposed LTE serial decoding scheme is adapted for parallel transformation. Then, considering the LTE high throughput requirements, a parallel decoding solution is proposed. Considering a parallelization with  $N = 2^{p}$  levels, the parallel approach reduces the decoding latency N times versus the serial decoding one. For parallel approach the decoding performance suffers a small degradation, but we propose a solution that almost eliminates this degradation, by performing an overlapped data block split. Moreover, considering the native properties of the LTE quadratic permutation polynomial (QPP) interleaver, we propose a simplified parallel decoder architecture. The novelty of this scheme is that only one interleaver module is used, no matter the value of N, by introducing an even-odd merge sorting network. We propose for it a recursive approach that uses only comparators and subtractors.

**Keywords:** LTE, WiMAX, turbo decoder, single interleaver, Max LOG MAP, parallel architecture, FPGA

## 1. Introduction

The channel coding theory was intensively studied during the last decades, but the interest on this topic increased even more following the pioneering work of Berrou et al. on turbo codes [1–3].

© 2017 The Author(s). Licensee InTech. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. (cc) BY In their early existence, the turbo codes proved to obtain great decoding performances, so that they were used in many standards as recommendations. They transformed into a more appealing solution once the processing capacity increased for the field programmable gate array (FPGA) and digital signal processor (DSP). Their implementation complexity was not prohibitive anymore, this allowing them to become mandatory.

In this context, the Third-Generation Partnership Project (3GPP) organization early proposed these novel coding techniques. It should be mentioned that turbo codes were introduced in standard by the first version of Universal Mobile Telecommunications System (UMTS) technology (in 1999). Moreover, the next UMTS releases (the following high-speed packet access) contributed with new and interesting features, while turbo coding remained still unchanged. Furthermore, several modifications were introduced by the long-term evolution (LTE) standard. Even if they were not significant as volume, their importance arose in terms of concept. In this framework, the 3GPP proposed for LTE a new interleaver scheme, while maintaining exactly the same coding structure as in UMTS. Also, the turbo codes were introduced by the Institute of Electrical and Electronics Engineers (IEEE) in 802.16 standards, known as the base for WiMAX systems.

In Ref. [4], an UMTS dedicated turbo decoding binary scheme is developed, whereas for WiMAX systems a similar duo-binary architecture is presented in Refs. [5] and [6]. Thanks to the new LTE/LTE-advanced (LTE-A) interleaver, the decoding performances are improved, as compared to the ones corresponding to the UMTS standard. In addition, the new LTE interleaver comes with native properties suited for a parallel decoding approach inside the algorithm, thus taking advantage on the main idea brought by turbo decoders (i.e., exchanging the extrinsic values between the two decoding units). In Ref. [7], a serial decoding scheme implemented on FPGA is presented. However, parallelization is still required when high throughput is required, as in the particular case of LTE systems using diversity techniques.

In the past years, many interesting parallel decoder schemes were studied by the researchers. In this context, the obtained results are measured on two directions. The direction number 1 is represented by the decoding performance degradation between the parallel and the serial solutions. The direction number 2 is the hardware resources occupied for such parallel decoder implementation. In Ref. [8], a first group of parallel decoding solutions is presented. It is based on the classical maximum a posteriori (MAP) algorithm. This method passes through the trellis twice, first time to compute the forward state metrics (FSM) and the second time to obtain the backward state metrics (BSM) and simultaneously the log likelihood ratios (LLR). Following this approach, several approaches were developed in order to reduce the theoretical latency of the decoding process of 2*K* clock periods for each semi-iteration (where *K* is the data block length).

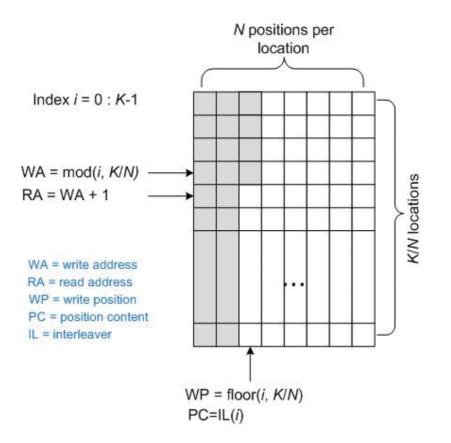

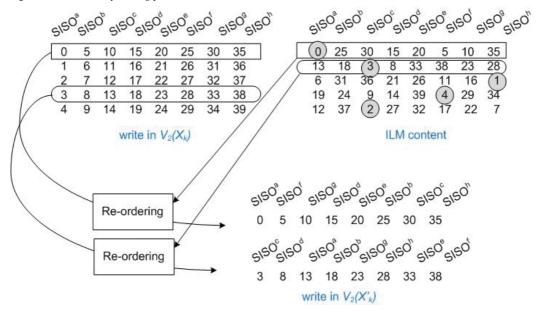

In Refs. [9] and [10], a second set of parallel architectures that take advantage of the quadratic permutation polynomial (QPP) interleaver algebraic-geometric properties is described. In these works, efficient hardware implementations of the QPP interleaver are proposed. However, the parallelization factor N still represents the number of used interleavers in the developed architectures.

In Ref. [11], a third approach was reported, which consists in using a folded memory. All the data needed for parallel processing are stored on the same time. On the other hand, the main

challenge of this kind of implementation is to correctly distribute the data to each decoding unit, once a memory location containing all N values is read. In order to solve this issue, an architecture based on two Batcher sorting networks was proposed. However, even in this approach, N interleavers are still needed to generate all the interleaved addresses that input the master network.

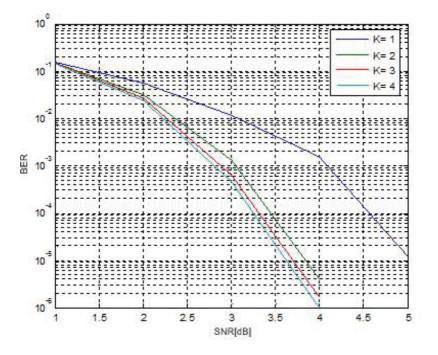

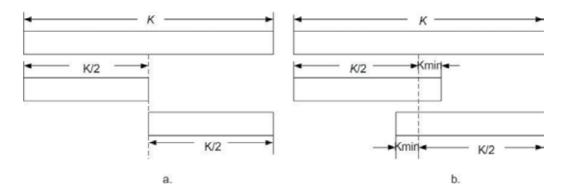

In this chapter, we present the optimized implementations for serial architectures for WiMAX and LTE turbo decoding schemes. Then, for LTE systems, we describe a parallel decoding architecture introduced in Refs. [12] and [13], which also relies on a folded memory-based approach. Nevertheless, the main difference as compared to the already existing solutions presented above is that our proposed approach includes only one interleaver. Additionally, with an even-odd merge sorting unit [14, 15], the parallel architecture maintains the same structure as the serial one, the only difference being given by the fact that the soft-input soft-output (SISO) decoding unit is included N times in the scheme. The block memory number and dimensions remain unchanged between the two proposed decoding structures. In terms of decoding performance, the obtained results for the serial and parallel approaches are almost similar. We propose an overlapped data block split that reduces the small degradation introduced by the parallel architecture.

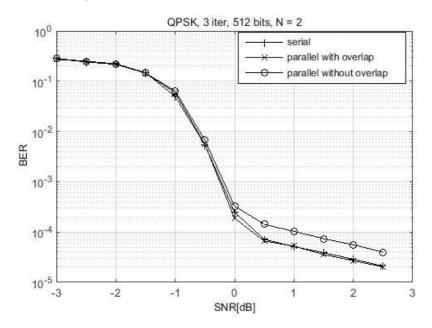

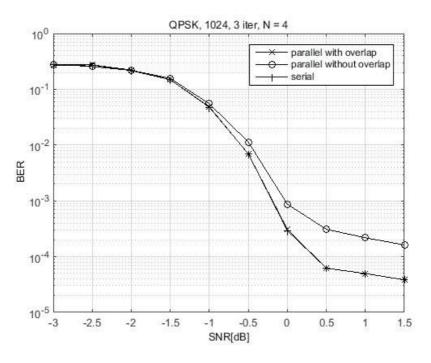

Finally, we present throughput and speed results obtained when targeting a XC5VFX70T [16] chip on Xilinx ML507 [17] board. Moreover, we provide simulation curves for the three considered cases, i.e., serial decoding, parallel decoding and parallel decoding with overlap.

## 2. The coding scheme

## 2.1. WiMAX systems

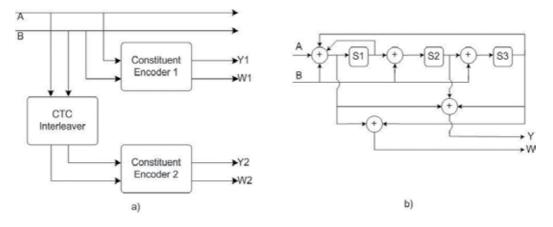

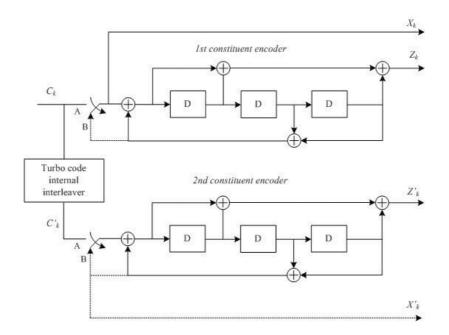

Section 8.4 from 802.16 standard [18] presents the coding scheme on the basis of which the proposed decoder is implemented. **Figure 1** shows the duo-binary encoder. The native coding rate is 1/3. In order to obtain other coding rates, a puncturing block must be used. Accordingly, a depuncturing block must be added to the receiver architecture.

Figure 1. (a) 802-16e turbo coding scheme; (b) constituent encoder.

Let us define the following parameters: coding rate *R*; block dimension (in pairs of bits, i.e., dibits) *K*, which is computed independent of a coding rate, as a function of the uncoded block size; the number of iterations *L*, i.e., the latency *Latency* (in clock periods); information bits rate  $R_b$  [Mbps]; and system clock frequency  $F_{clk}$  [MHz].

As mentioned in Ref. [6], the main problem of a convolutional turbo code (CTC) decoder implementation is represented by the amount of required hardware resources. Moreover, in order to reach the targeted high data rate, the system clock has to be fast. Equation (1) presents the decoding throughput.

$$R_b = \frac{2K}{\text{Latency } T_{clk}} \tag{1}$$

For a fixed latency algorithm, according to Eq. (1), the output throughput is improved when achieving a higher clock frequency. Another way is to reduce latency using a parallel architecture; however, this increases the occupied area and may lead to a smaller clock frequency due to longer routes. Moreover, another direct constraint is the significant memory needed for storing data. This issue also affects the frequency, since a large number of used memory blocks leads to a large resource spread on chip and, obviously, longer routes.

Taking into account the previously mentioned aspects, we can conclude that all the parameters presented above are related, so that a global optimization is not possible. Consequently, we have chosen to balance each direction in order to meet throughput requirements.

#### 2.2. LTE systems

A classic turbo coding scheme is presented in the 3GPP LTE specification, including two constituent encoders and one interleaver module (**Figure 2**). The data block  $C_k$  can be observed at the input of the LTE turbo encoder. The *K* bits from this input data block are transferred at the output, as systematic bits, in the steam  $X_k$ . At the same time, the first constituent encoder processes the input data block, resulting the parity bits  $Z_k$ , whereas the second constituent encoder processes the interleaved data block  $C'_{k'}$  resulting the parity bits  $Z'_k$ . Combining the systematic bits and the two streams of parity bits, we obtain the following sequence (at the output of the encoder):  $X_1$ ,  $Z_1$ ,  $Z'_1$ ,  $X_2$ ,  $Z'_2$ ,  $Z'_2$ , ...,  $X_{K'}$ ,  $Z_{K'}$ ,  $Z'_K$ .

In order to drive back the constituent encoders to the initial state (at the end of the coding process), the switches from **Figure 2** are moved from position A to position B. Since the final states of the two constituent encoders are not the same (different input data blocks produce different final state), this switching procedure generates tail bits for each encoder. These tail bits are sent together with the systematic and parity bits, thus resulting the following final sequence:  $X_{K+1}$ ,  $Z_{K+1}$ ,  $X_{K+2}$ ,  $Z_{K+3}$ ,  $Z_{K+3}$ ,  $Z'_{K+1}$ ,  $Z'_{K+1}$ ,  $Z'_{K+2}$ ,  $Z'_{K+2}$ ,  $Z'_{K+3}$ .

As it was previously mentioned and discussed in Ref. [7], the LTE turbo coding scheme introduces a new interleaving structure. Thus, the input sequence is rearranged at the output using:

Efficient FPGA Implementation of a CTC Turbo Decoder for WiMAX/LTE Mobile Systems 29 http://dx.doi.org/10.5772/67017

Figure 2. LTE turbo coding scheme.

$$C'_{i} = C_{\pi(i)}, \quad i = 1, 2, ..., K$$

, (2)

where the interliving function  $\pi$  applied over the output index *i* is defined as

$$\pi(i) = (f_1 \cdot i + f_2 \cdot i^2) \operatorname{mod} K \tag{3}$$

The input block length K and the parameters  $f_1$  and  $f_2$  are provided in Table 5.1.3-3 in Ref. [19].

#### 3. The decoding algorithm

#### 3.1. WiMAX systems

The decoding architecture consists of two decoding units called constituent decoders. Each such unit receives systematic bits (in natural order or interleaved) and parity bits, as shown in **Figure 1**.

The block diagram implements a maximum-logarithmic-maximum A posteriori (Max-Log-MAP) algorithm. For the case of turbo binary codes, the decoder scheme will represent, in the log likelihood ratio (LLR) space, each binary symbol as a single likelihood ratio. But in the situation of turbo duo-binary codes, the decoding unit requires three likelihood ratios in the same space. If we consider the duo-binary pair  $A_k$  and  $B_{kr}$ , the LLRs may be computed as:

$$\Lambda_{a,b} = (A_k, B_k) = \log \frac{P(A_k = a, B_k = b)}{P(A_k = 0, B_k = 0)}$$

(4)

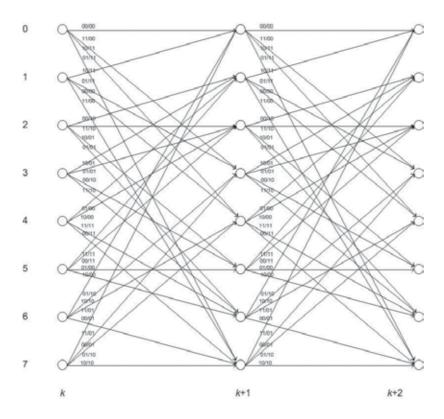

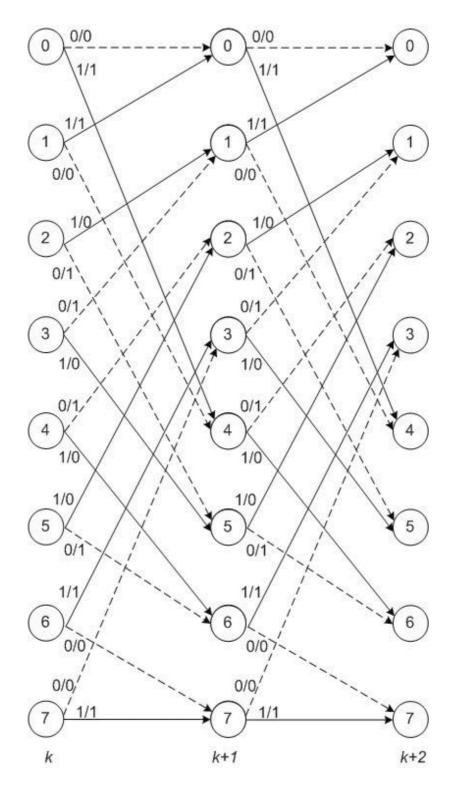

where (*a*,*b*) are (0,1), (1,0), or (1,1). The ratio set is updated by each decoding unit (constituent decoder) for each input pair, using the corresponding LLRs and parity bits, also seen as LLRs. Then, the output LLRs minus the input LLRs provides the extrinsic values. The trellis for a duo-binary code contains eight states, each such state with four inputs and four outputs, as presented in **Figure 3**. Using the systematic and parity pairs LLRs, for each branch, the metric  $\gamma_k(S_i \rightarrow S_j)$  is computed, i.e.,

$$\gamma_k(S_i \to S_j) = \Lambda^i_{a,b}(A_k, B_k) + w\Lambda(W_k) + y\Lambda(Y_k)$$

(5)

Figure 3. WiMAX decoder trellis.

The constituent decoder (**Figure 4**) performs the corresponding processing forward and backward over the trellis. When moving forward, the decoder computes the unnormalized metric  $\alpha'_{k+1}(S_j)$  corresponding to each computed normalized metric  $\alpha_k(S_i)$  associated with state  $S_i$ , using (**Figure 4**)

$$\alpha'_{k+1}(S_j) = \max_{S_i \to S_j} \{ \alpha_k(S_i) + \gamma_k(S_i \to S_j) \}$$

(6)

Efficient FPGA Implementation of a CTC Turbo Decoder for WiMAX/LTE Mobile Systems 31 http://dx.doi.org/10.5772/67017

Figure 4. Decoder block scheme.

where the operator "maximum" is executed over all four branches entering the state  $S_j$  at the time stamp k + 1. Once the metrics for all states are updated at time stamp k + 1, the normalization versus the state  $S_0$  value is made by the decoder. Analogously to forward processing, for backward moving, the decoder computes:

$$\beta'_k(S_i) = \max_{S_i \to S_j} \{\beta_{k+1}(S_j) + \gamma_k(S_i \to S_j)\}$$

$$\tag{7}$$

where the operator "maximum" and the normalization method are similar to Eq. (6).

The initialization with null values is carried out for all the forward and backward metrics at all states. Once the new values are computing and stored, the decoding unit executes the second step in the decoding procedure, i.e., the LLRs computing as in Eq. (4). The decoding unit starts by computing the likelihood ratio for each branch

$$Z_k(S_i \to S_j) = \alpha_k(S_i) + \gamma_k(S_i \to S_j) + \beta_{k+1}(S_j)$$

(8)

and continues with the value

$$t_k(a,b) = \max_{S_i \to S_i:(a,b)} \{Z_k\}$$

(9)

where the operator "maximum" is computed over all eight branches generated by the pair (a, b). At the end, the output LLR is computed as

$$\Lambda^{o}_{a,b}(A_k, B_k) = t_k(a, b) - t_k(0, 0)$$

(10)

The decoding procedure is executed for a decided number of iterations or until a convergence criterion is reached. Then, a final decision is taken over the bits. This is achieved by computing for each bit from the pair ( $A_k$ ,  $B_k$ ) the corresponding LLR:

$$\Lambda(A_k) = \max\{\Lambda_{1,0}^o(A_k, B_k), \Lambda_{1,1}^o(A_k, B_k)\} - \max\{\Lambda_{0,0}^o(A_k, B_k), \Lambda_{0,1}^o(A_k, B_k)\}$$

(11)

$$\Lambda(B_k) = \max\{\Lambda_{0,1}^o(A_k, B_k), \Lambda_{1,1}^o(A_k, B_k)\} - \max\{\Lambda_{0,0}^o(A_k, B_k), \Lambda_{1,0}^o(A_k, B_k)\},$$

(12)

where  $\Lambda_{0,0}^{o}(A_k, B_k) = 0$ . Finally, by comparing each LLR with a null threshold, i.e., looking at the sign, the hard decision is made.

#### 3.2. LTE systems

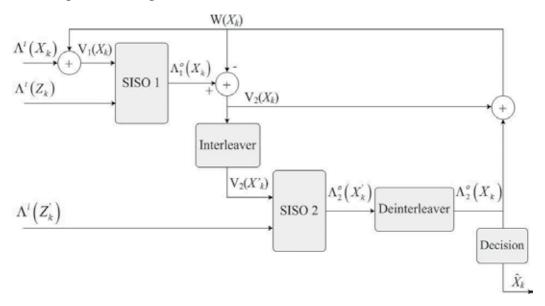

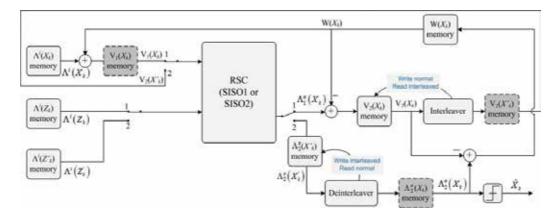

The decoding architecture for the LTE systems is presented in **Figure 5**. The two decoding units called recursive systematic convolutional (RSC) use theoretically the MAP algorithm. The MAP solution, a classical one, ensures the best decoding performances. Unfortunately, at the same time, it is characterized by an increased implementation complexity and also it may include variables with a large dynamic range. These are the reasons why the classical solution with the MAP algorithm is used only as a reference for the expected decoding performance. When it comes to real implementation, new suboptimal algorithms have been studied: Logarithmic MAP (Log MAP) [20], Max Log MAP, Constant Log MAP (Const Log MAP) [21] and Linear Log MAP (Lin Log MAP) [22].

Figure 5. LTE turbo decoder.

For the LTE systems, we consider a decoding architecture based on the Max Log MAP algorithm. This suboptimal algorithm overcomes the problems of implementation complexity and dynamic range by paying the price of lower decoding performance when compared with the MAP algorithm. However, this degradation can be maintained inside some accepted limits. Starting from the Jacobi logarithm, only the first term is used by the Max Log MAP algorithm, i.e.,

$$\max^{*}(x,y) = \ln(e^{x} + e^{y}) = \max(x,y) + \ln(1 + e^{-|y-x|}) \approx \max(x,y) .$$

(13)

The trellis diagram for the turbo decoding architecture of the LTE systems contains eight states, as presented in **Figure 6**. Each state of the diagram has two inputs and two outputs. The branch metric between the states  $S_i$  and  $S_j$  is

Efficient FPGA Implementation of a CTC Turbo Decoder for WiMAX/LTE Mobile Systems 33 http://dx.doi.org/10.5772/67017

Figure 6. LTE turbo coder trellis.

$$\gamma_{ii} = \mathcal{V}(X_k)X(i,j) + \Lambda^i(Z_k)Z(i,j) , \qquad (14)$$

where X(i,j) and Z(i,j) are the data, respectively, the parity bits, both associated with one branch and  $\Lambda^i(Z_k)$  is the LLR for the input parity bit. For SISO 1 decoding unit, this input LLR is  $\Lambda^i(Z_k)$ , whereas for SISO 2 it becomes  $\Lambda^i(Z'_k)$ . For SISO 1,  $V(X_k) = V_1(X_k)$  $= \Lambda^i(X_k) + W(X_k)$ , whereas for SISO 2,  $V(X_k) = V_2(X'_k) = IL\{\Lambda^o_1(X_k) + W(X_k)\}$ , where "IL" operator denotes the interleaving procedure. In **Figure 5**,  $W(X_k)$  is the *extrinsic information*, whereas  $\Lambda^o_1(X_k)$  and  $\Lambda^o_2(X'_k)$  are the output LLRs generated by the two SISOs.

Looking at the LTE turbo encoder trellis, one can notice that between two states, there are four possible values for the branch metrics:

$$\begin{aligned} \gamma_0 &= 0\\ \gamma_1 &= \mathbf{V}(\mathbf{X}_k)\\ \gamma_2 &= \Lambda^i(\mathbf{Z}_k)\\ \gamma_2 &= \mathbf{V}(\mathbf{X}_k) + \Lambda^i(\mathbf{Z}_k) . \end{aligned} \tag{15}$$

The LTE decoding process follows a similar approach as for WiMAX systems, i.e., it moves forward and backward through the trellis.

#### 3.2.1. Backward recursion

The algorithm moves backward over the trellis computing the metrics. The obtained values for each node are stored in a normalized manner. They will be used for the LLR computation once the algorithm will start moving forward through the trellis. We name  $\beta_k(S_i)$  the backward metric computed at the *k*th stage, for the state  $S_i$ , where  $2 \le k \le K + 3$  and  $0 \le i \le 7$ . For the backward recursion, the initialization  $\beta_{K+3}(S_i) = 0, 0 \le i \le 7$  is used at the stage k = K + 3. For the rest of the stages  $2 \le k \le K + 2$ , the computed backward metrics are

$$\hat{\beta}_{k}(S_{i}) = \max\{\left(\beta_{k+1}(S_{j1}) + \gamma_{ij1}\right), \left(\beta_{k+1}(S_{j2}) + \gamma_{ij2}\right)\},$$

(16)

where  $S_{j1}$  and  $S_{j2}$  are the two states from stage k + 1 connected to the state  $S_i$  from stage k and  $\hat{\beta}_k(S_i)$  represents the unnormalized metric. Once the unnormalized metric  $\hat{\beta}_k(S_0)$  is computed for state  $S_0$ , all the backward metrics for states  $S_1...S_7$  are normalized as

$$\beta_k(S_i) = \hat{\beta}_k(S_i) - \hat{\beta}_k(S_0) \tag{17}$$

and then stored in the dedicated memory.

#### 3.2.2. Forward recursion

When the backward recursion is finished, the algorithm moves forward through the trellis in the normal direction. This specific phase of the decoding is similar to the one for Viterbi algorithm. In this case, the storing procedure is needed only for the previous stage metrics, i.e., for computing the current stage k metrics, only the forward metrics from the last stage k - 1 are needed. We will name  $\alpha_k(S_i)$  the forward metric corresponding to state at the stage k, where  $0 \le k \le K - 1$  and  $0 \le i \le 7$ . For the forward recursion, the initialization  $\alpha_0(S_i) = 0$ ,  $0 \le i \le 7$  is used at the stage k = 0. For the rest of the stages  $1 \le k \le K$ , the unnormalized forward metrics are computed as

$$\hat{\alpha}_{k}(S_{j}) = \max\left\{ \left( \alpha_{k-1}(S_{i1}) + \gamma_{i1j} \right), \left( \alpha_{k-1}(S_{i2}) + \gamma_{i2j} \right) \right\},$$

(18)

where  $S_{i1}$  and  $S_{i2}$  are the two states from stage k - 1 connected to the state  $S_j$  from stage k. Once the unnormalized metric  $\hat{\alpha}_k(S_0)$  is computed for state  $S_0$ , all the forward metrics for states  $S_1...S_7$  are normalized as

$$\alpha_k(S_i) = \hat{\alpha}_k(S_i) - \hat{\alpha}_k(S_0) . \tag{19}$$

The decoding algorithm can obtain now an LLR estimated for the data bits  $X_k$  since it has for each stage k the forward metrics just computed and also the backward metrics stored in the memory. For the first time, this LLR is obtained by computing the likelihood of the connection between the state  $S_i$  at stage k - 1 and the state  $S_j$  at stage k as

$$Z_k(S_i \to S_j) = \alpha_{k-1}(S_i) + \gamma_{ij} + \beta_k(S_j) .$$

$$\tag{20}$$

The likelihood of having a bit equal to 0 (or 1) is when the Jacobi logarithm of all the branch likelihood corresponds to 0 (or 1) and thus:

$$\Lambda^{o}(X_{k}) = \max_{(S_{i} \to S_{j}): X_{i}=1} \{ Z_{k}(S_{i} \to S_{j}) \} - \max_{(S_{i} \to S_{j}): X_{i}=0} \{ Z_{k}(S_{i} \to S_{j}) \},$$

(21)

where "max" operator is recursively computed over the branches, which have at the input a bit of 1 { $(S_i \rightarrow S_j) : X_i = 1$ } or a bit 0 { $(S_i \rightarrow S_j) : X_i = 0$ }.

#### 4. Proposed serial decoding scheme

#### 4.1. WiMAX systems

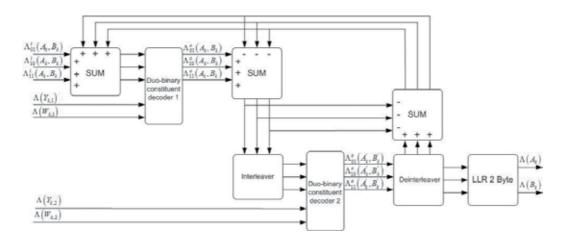

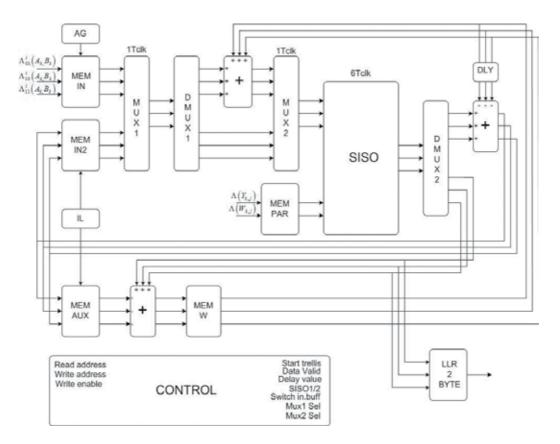

One important remark about the decoding algorithm is that the outputs of one constituent decoder represent the inputs for the other constituent decoder. At the same time, knowing that the interleaver and deinterleaver procedures apply over the data blocks (so the complete block is needed) in a nonoverlapping manner will allow the usage of a single constituent decoder. This decoding unit operates time multiplexed and the corresponding proposed scheme is presented in **Figure 7**.

In **Figure 7**, we can identify storing requirements: the memory blocks that store data from one semi-iteration to another and the memory blocks used from one iteration to another. IL stands for the interleaver/deinterleaver procedure, while CONTROL is the management unit, controlling the decoder functionalities. This module provides the addresses used for

Figure 7. Proposed decoder scheme.

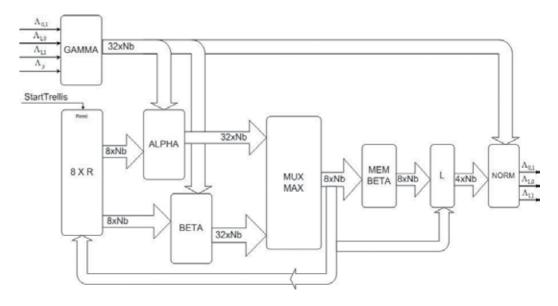

read and write, the signals used to trigger the forward and backward movements through the trellis, the selection for one of the two SISO units and also the control of MUX and DEMUX blocks. The input buffer is also selected since the decoding architecture can accept a new-encoded data block while still processing the previous one. The most important module shown in **Figure 7** is the SISO unit, which is the decoding structure. **Figure 8** depicts the block scheme of this decoding unit. One can observe the unnormalized metric computing modules BETA (backward) and ALPHA (forward) and the module GAMMA that computes the transition metric. This last one ensures also the normalization: the metrics values obtained for state  $S_0$  are subtracted from the metrics values obtained for the states  $S_1...S_7$ . The output LLRs are computed inside the L module and normalized inside the NORM module. The MUX-MAX module provides the correct inputs when moving forward or backward through the trellis. It also computes the maximum function. The backward metrics are stored in MEM BETA memory during backwards recursion, their values being read when executing the forward recursion, in order to compute the estimated LLRs.

It is important to mention that some studies have been conducted regarding the normalization function. Trying to increase the system frequency (in order to reduce the decoding latency and

Efficient FPGA Implementation of a CTC Turbo Decoder for WiMAX/LTE Mobile Systems 37 http://dx.doi.org/10.5772/67017

Figure 8. SISO block scheme.

so, to increase the decoded data throughput), one may think of removing the normalization and so to reduce the amount of logic on the critical path. This solution is not applicable because five extra bits would be needed for metrics values. From here more the memory blocks and more the complex arithmetic. Finally, all these will lead to a lower system frequency, so no benefit on this approach. On the other hand, we propose a dedicated approach to implement the metric computation blocks (ALPHA, BETA and GAMMA). Based on the trellis state, we identified the relations for each metric, 32 equations being used for transition metric computation (we remind that for each of the eight trellis states we have four possible transitions). Moreover, only 16 are distinct (the other 16 are the same) and from these 16, some are null. Using this approach, a complexity decrease is obtained.

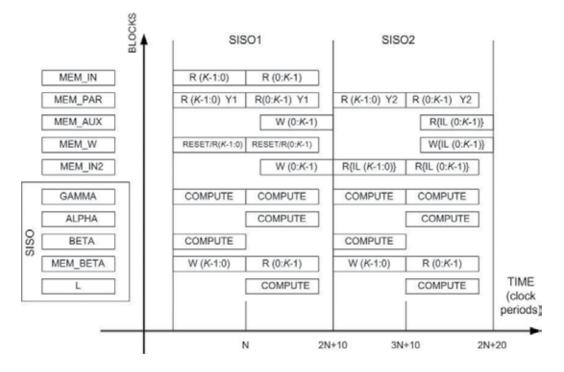

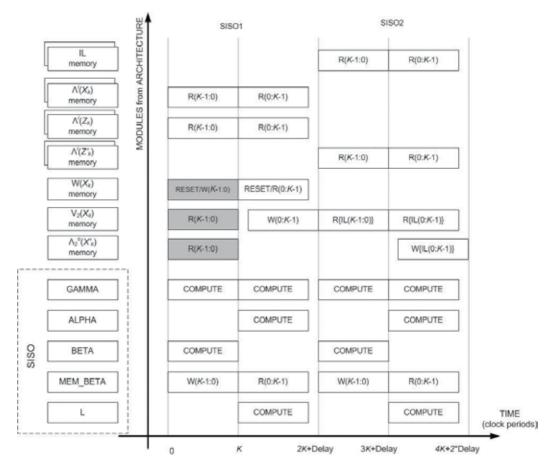

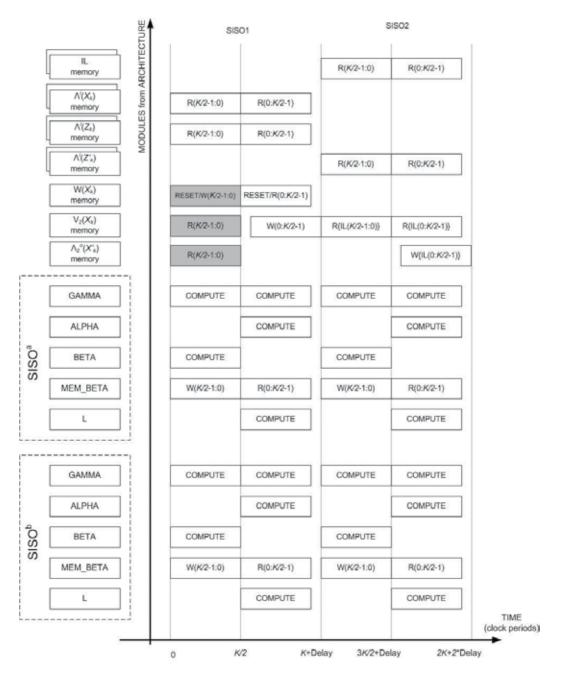

**Figure 9** depicts the timing diagram for the proposed SISO. This corresponds to the scenario with one SISO unit and some MUX and DEMUX blocks replacing the two SISO units from the theoretical decoding architecture (see **Figure 7**).

In **Figure 9**, R/W (K – 1:0) means reading/writing memory from addresses K – 1 to 0, R/W {IL (K – 1:0)} means reading/writing memory from interleaved addresses K – 1 to 0 and COM-PUTE means that the block is processing the input data.

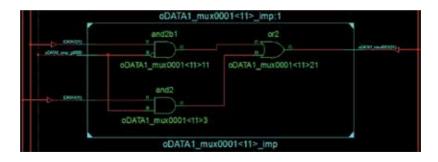

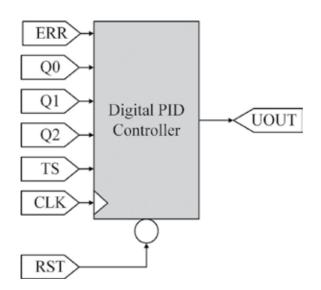

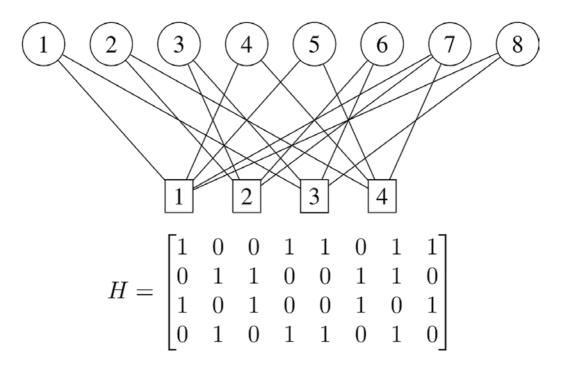

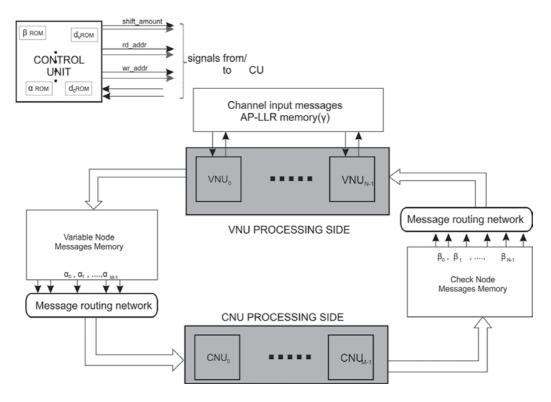

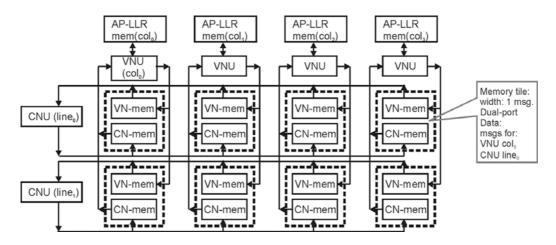

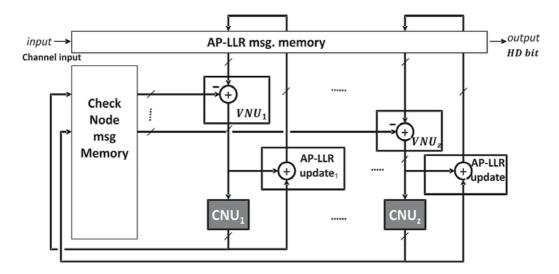

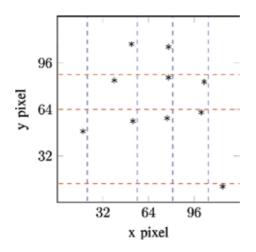

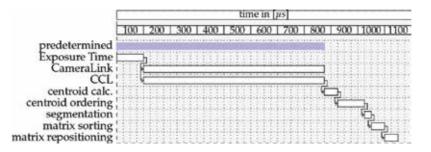

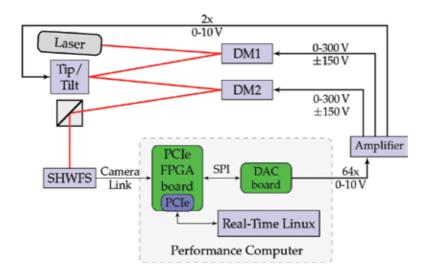

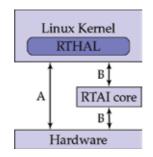

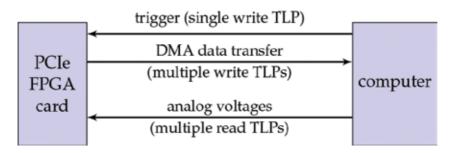

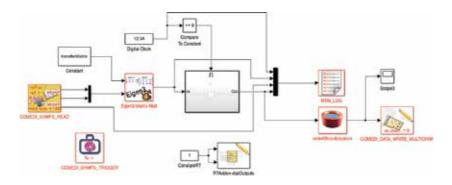

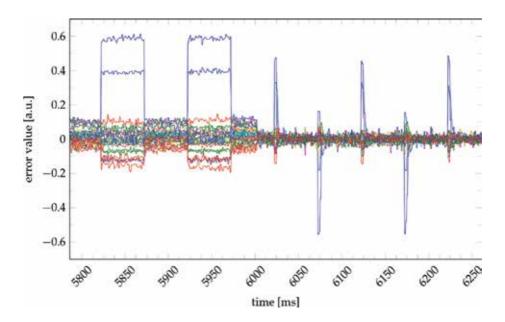

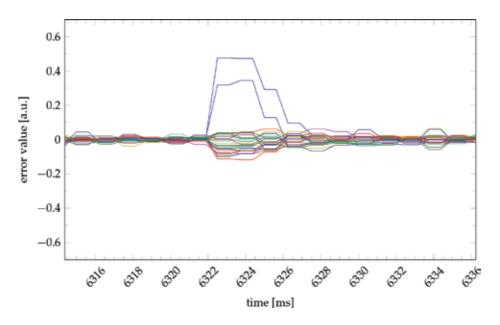

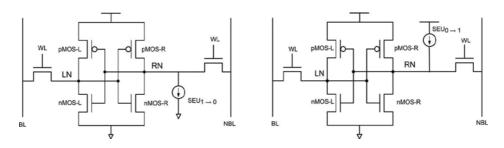

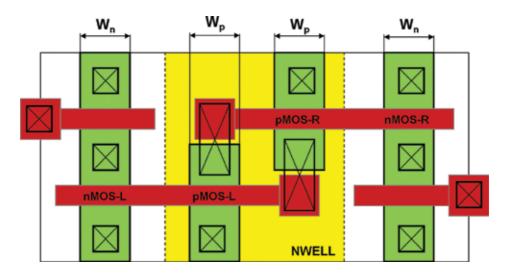

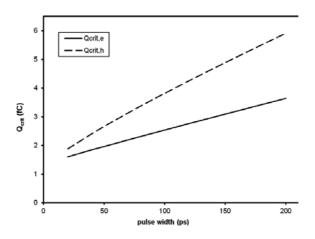

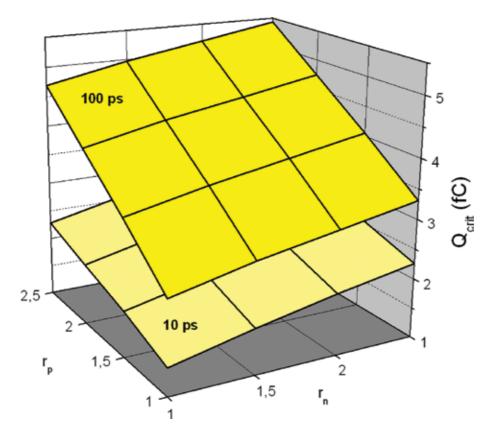

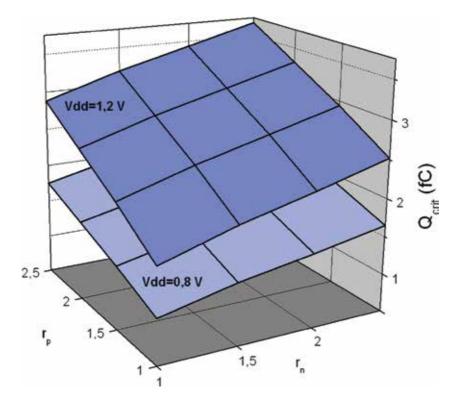

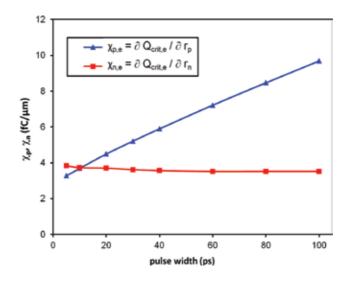

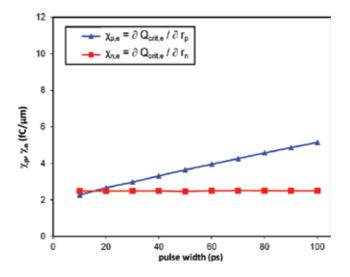

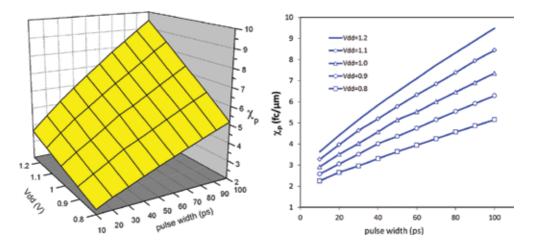

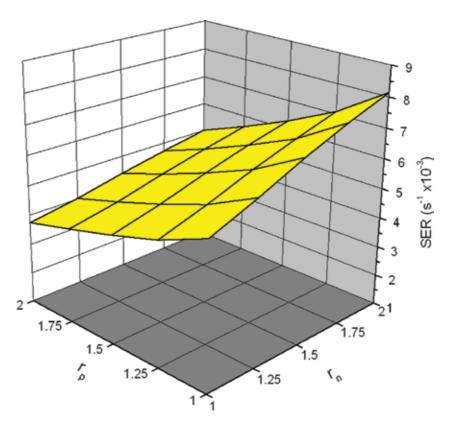

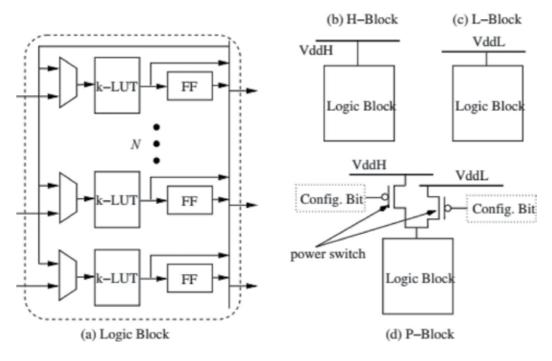

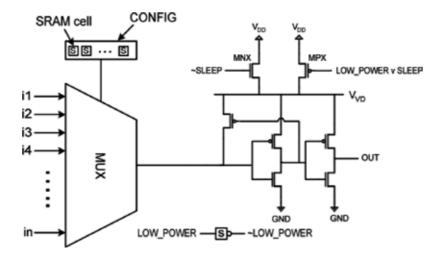

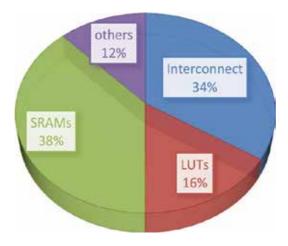

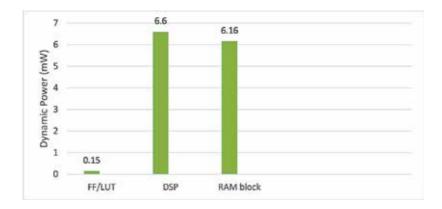

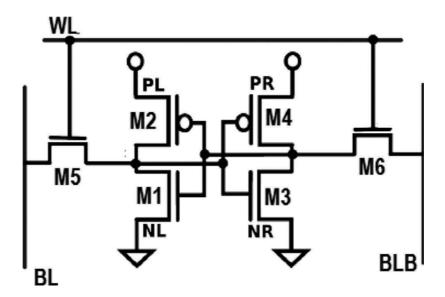

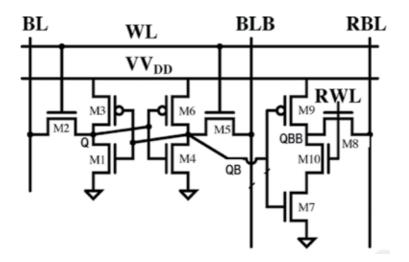

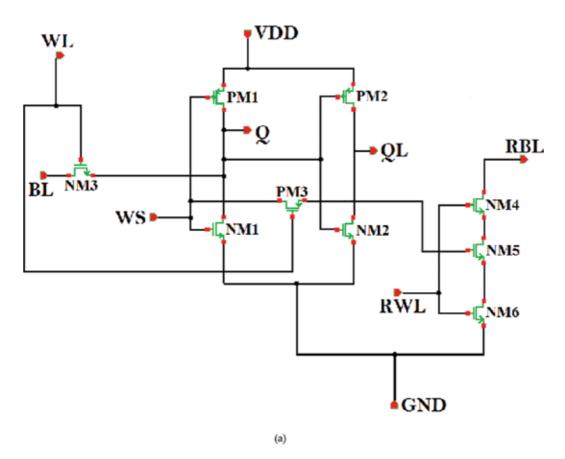

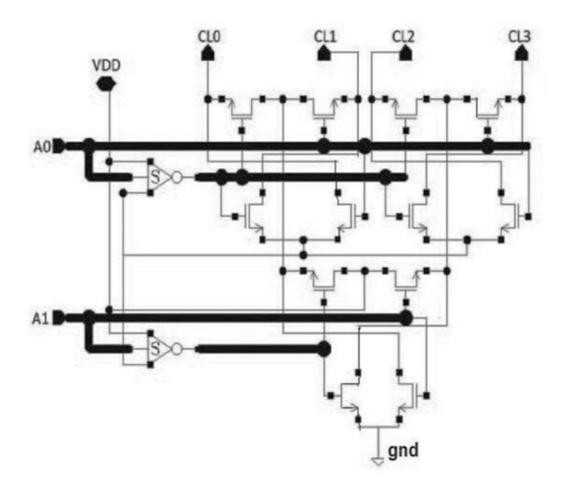

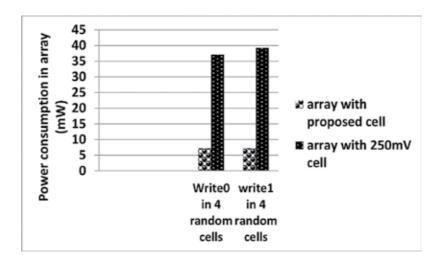

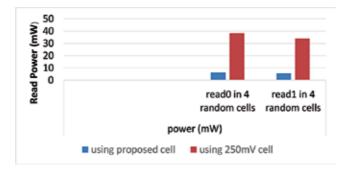

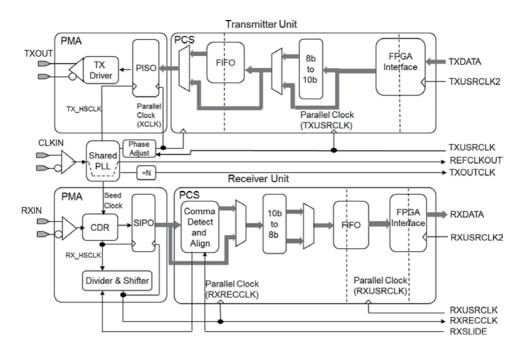

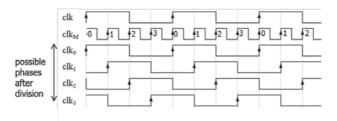

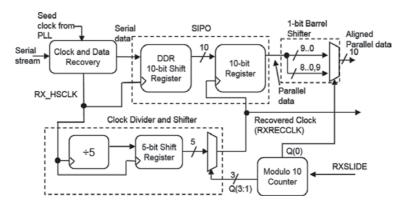

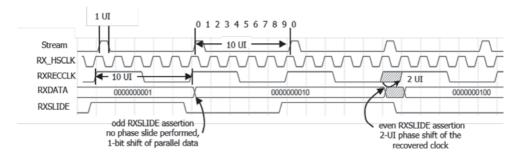

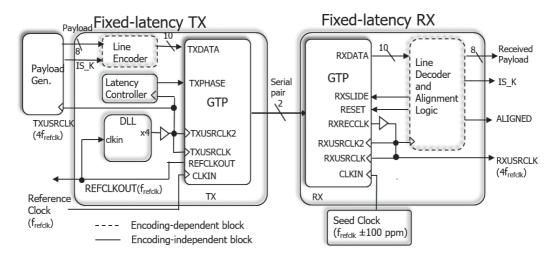

#### 4.2. LTE systems