### IntechOpen

## Ferroelectrics Applications

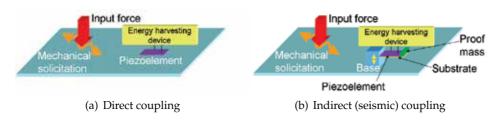

Edited by Mickaël Lallart

# FERROELECTRICS -APPLICATIONS

Edited by Mickaël Lallart

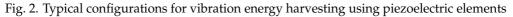

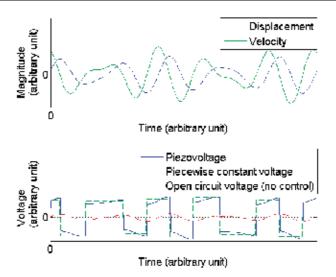

#### **Ferroelectrics - Applications**

http://dx.doi.org/10.5772/947 Edited by Mickaël Lallart

#### Contributors

Kai-Huang Chen, Chien-Min Cheng, Chih-sheng Chen, Ping-Kuan Chang, Ying-Chung Chen, Antonino S. Fiorillo, Salvatore A. Pullano, Yuegang Zhang, Noureddine Tayebi, Igor Leonidovich Baginsky, Edward G. Genadievich Kostsov, Sung-Min Yoon, Shinhyuk Yang, Soon-Won Jung, Sang-Hee Ko Park, Chun-Won Byun, Min-Ki Ryu, Himchan Oh, Chi-Sun Hwang, Kyoung-Ik Cho, Byoung-Gon Yu, Ana Guerreiro, Alan Silva, Cicília Raquel Maia Leite, Larry McMillan, Carlos Araujo, Maurizio Tranchero, Claudio Sansoe, Kinam Kim, Dong Jin Jung, Sylvain Ballandras, Gwenn Ulliac, Emilie Courjon, Florent Bassignot, Jérôme Hauden, Julien Garcia, Thierry Laroche, William Daniau, Toshio Ogawa, Mickaël Lallart, Daniel Jean Guyomar

#### © The Editor(s) and the Author(s) 2011

The moral rights of the and the author(s) have been asserted.

All rights to the book as a whole are reserved by INTECH. The book as a whole (compilation) cannot be reproduced, distributed or used for commercial or non-commercial purposes without INTECH's written permission. Enquiries concerning the use of the book should be directed to INTECH rights and permissions department (permissions@intechopen.com).

Violations are liable to prosecution under the governing Copyright Law.

#### CC BY

Individual chapters of this publication are distributed under the terms of the Creative Commons Attribution 3.0 Unported License which permits commercial use, distribution and reproduction of the individual chapters, provided the original author(s) and source publication are appropriately acknowledged. If so indicated, certain images may not be included under the Creative Commons license. In such cases users will need to obtain permission from the license holder to reproduce the material. More details and guidelines concerning content reuse and adaptation can be foundat http://www.intechopen.com/copyright-policy.html.

#### Notice

Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published chapters. The publisher assumes no responsibility for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained in the book.

First published in Croatia, 2011 by INTECH d.o.o. eBook (PDF) Published by IN TECH d.o.o. Place and year of publication of eBook (PDF): Rijeka, 2019. IntechOpen is the global imprint of IN TECH d.o.o. Printed in Croatia

Legal deposit, Croatia: National and University Library in Zagreb

Additional hard and PDF copies can be obtained from orders@intechopen.com

Ferroelectrics - Applications Edited by Mickaël Lallart p. cm. ISBN 978-953-307-456-6 eBook (PDF) ISBN 978-953-51-4456-4

# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

4,000+

Open access books available

+ 116,000+

International authors and editors

120M+

Downloads

151 Countries delivered to Our authors are among the Top 1%

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

### Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# Meet the editor

Mickaël Lallart graduated from Institut National des Sciences Appliquées de Lyon (INSA Lyon), Lyon, France, in electrical engineering in 2006, and received his Ph.D. in electronics, electrotechnics, and automatics from the same university in 2008, where he worked for the Laboratoire de Génie Electrique et Ferroélectricité (LGEF). After working as a post-doctoral fellow in the

Center for Intelligent Material Systems and Structures (CIMSS) in Virginia Tech, Blacksburg, VA, USA in 2009, Dr. Lallart has been hired as an Associate Professor in the Laboratoire de Génie Electrique et Ferroélectricité. His current field of interest focuses on electroactive materials and their applications, vibration damping, energy harvesting and Structural Health Monitoring, as well as autonomous, self-powered wireless systems.

### Contents

#### Preface XI

Part 1 Sensors and Actuators 1

- Chapter 1 Giant k<sub>31</sub> Relaxor Single-Crystal Plate and Their Applications 3 Toshio Ogawa

- Chapter 2 **MEMS Based on Thin Ferroelectric Layers 35** Igor L. Baginsky and Edward G. Kostsov

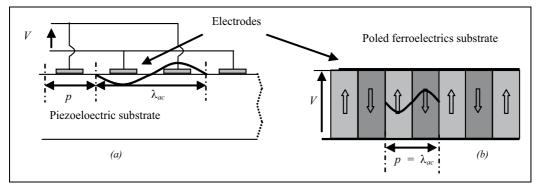

- Chapter 3 **Periodically Poled Acoustic Wave-Guide** and Transducers for Radio-Frequency **Applications 59** Sylvain Ballandras, Emilie Courjon, Florent Bassignot, Gwenn Ulliac, Jérôme Hauden, Julien Garcia, Thierry Laroche and William Daniau

- Chapter 4 Ferroelectric Polymer for Bio-Sonar Replica 75 Antonino S. Fiorillo and Salvatore A. Pullano

- Chapter 5 Ferroelectric Materials for Small-Scale Energy Harvesting Devices and Green Energy Products 95 Mickaël Lallart and Daniel Guyomar

- Part 2 Memories 115

- Chapter 6 Future Memory Technology and Ferroelectric Memory as an Ultimate Memory Solution 117 Kinam Kim and Dong Jin Jung

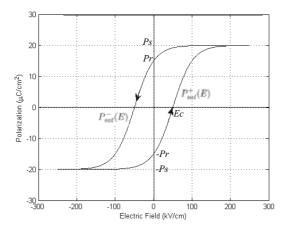

- Chapter 7 Ultrahigh Density Probe-based Storage Using Ferroelectric Thin Films 157 Noureddine Tayebi and Yuegang Zhang

- X Contents

- Chapter 8 Fabrication and Study on One-Transistor-Capacitor Structure of Nonvolatile Random Access Memory TFT Devices Using Ferroelectric Gated Oxide Film 179 Chien-Min Cheng, Kai-Huang Chen, Chun-Cheng Lin, Ying-Chung Chen, Chih-Sheng Chen and Ping-Kuan Chang

- Chapter 9 Ferroelectric Copolymer-Based Plastic Memory Transistos 195

Sung-Min Yoon, Shinhyuk Yang, Soon-Won Jung, Sang-Hee Ko Park, Chun-Won Byun, Min-Ki Ryu, Himchan Oh, Chi-Sun Hwang, Kyoung-Ik Cho and Byoung-Gon Yu

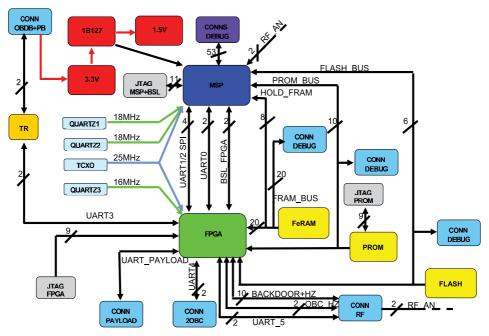

- Chapter 10 Use of FRAM Memories in Spacecrafts 213 Claudio Sansoè and Maurizio Tranchero

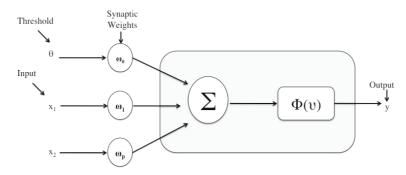

- Chapter 11 Adaptive Boolean Logic Using Ferroelectrics Capacitors as Basic Units of Artificial Neurons 231 Alan P. O. da Silva, Cicília R. M. Leite, Ana M. G. Guerreiro, Carlos A. Paz de Araujo and Larry McMillan

### Preface

Ferroelectricity has been one of the most used and studied phenomena in both scientific and industrial communities. Properties of ferroelectrics materials make them particularly suitable for a wide range of applications, ranging from sensors and actuators to optical or memory devices. Since the discovery of ferroelectricity in Rochelle Salt (which used to be used since 1665) in 1921 by J. Valasek, numerous applications using such an effect have been developed. First employed in large majority in sonars in the middle of the 20<sup>th</sup> century, ferroelectric materials have been able to be adapted to more and more systems in our daily life (ultrasound or thermal imaging, accelerometers, gyroscopes, filters...), and promising breakthrough applications are still under development (non-volatile memory, optical devices...), making ferroelectrics one of tomorrow's most important materials.

The purpose of this collection is to present an up-to-date view of ferroelectricity and its applications, and is divided into four books:

- *Material Aspects,* describing ways to select and process materials to make them ferroelectric.

- *Physical Effects,* aiming at explaining the underlying mechanisms in ferroelectric materials and effects that arise from their particular properties.

- *Characterization and Modeling,* giving an overview of how to quantify the mechanisms of ferroelectric materials (both in microscopic and macroscopic approaches) and to predict their performance.

- *Applications,* showing breakthrough use of ferroelectrics.

Authors of each chapter have been selected according to their scientific work and their contributions to the community, ensuring high-quality contents.

The present volume focuses on the applications of ferroelectric materials, describing innovative systems that use ferroelectricity. The current use of such devices as sensors and actuators, in the field of acoustics, MEMS, micromotors and energy harvesting will be presented in chapters 1 to 5. The next section proposes a particular emphasis

#### XII Preface

on the application of ferroelectric materials as transistors and memory devices (chapters 6 to 11), showing one of the future breakthrough uses of these materials.

I sincerely hope you will find this book as enjoyable to read as it was to edit, and that it will help your research and/or give new ideas in the wide field of ferroelectric materials.

Finally, I would like to take the opportunity of writing this preface to thank all the authors for their high quality contributions, as well as the InTech publishing team (and especially the publishing process manager Ms. Silvia Vlase) for their outstanding support.

June 2011

**Dr. Mickaël Lallart** INSA Lyon, Villeurbanne, France

Part 1

**Sensors and Actuators**

### Giant k<sub>31</sub> Relaxor Single-Crystal Plate and Their Applications

Toshio Ogawa

Department of Electrical and Electronic Engineering, Shizuoka Institute of Science and Technology, Japan

#### 1. Introduction

Typical ferroelectric ceramics, lead zirconate titanate (PZT) ceramics are widely used for devices of electrical-mechanical energy conversion devices such as sensors and actuators, which correspond to the five senses and foot & hand of human being. Recently, these devices spread out in the computer controlled fields, for example, robotics and mechatronics. The research and development of ferroelectric ceramics, particularly PZT ceramics, have mainly focused on the material compositions to realize new electronic devices utilizing their piezoelectric properties. Many researchers in companies and institutes have carried out R & D on such chemical compositions since the discovery of piezoelectricity in PZT ceramics by Jaffe et al. in 1954. On the other hand, through the new research on DC poling field dependence of ferroelectric properties in PZT ceramics, the poling field has become an effective tool for evaluation and control of the domain structures, which fix the dielectric and ferroelectric properties of PZT ceramics. Therefore, PZT ceramics with different domain structures can be fabricated even though the ceramic compositions remain the same. These ceramics are called poling field domain controlled ceramic. It is thought that the domain controlled ceramics will lead to a breakthrough and the appearance of new ferroelectric properties. The study on the clarification of relationships between [compositions] vs [poling fields] vs [dielectric and piezoelectric properties] in hard and soft PZT ceramics was applied to other ferroelectric materials of lead titanate ceramics, lead-free ceramics such as barium titanate, alkali bismuth niobate, alkali bismuth titanate ceramics and relaxor single crystals of Pb[(Zn<sub>1/3</sub>Nb<sub>2/3</sub>)<sub>091</sub>Ti<sub>0.09</sub>]O<sub>3</sub> (PZNT91/09) and Pb[(Mg<sub>1/3</sub>Nb<sub>2/3</sub>)<sub>0.74</sub>Ti<sub>0.26</sub>]O<sub>3</sub> (PMNT74/26) compositions.

This chapter describes how can be achieved the new ferroelectric properties such as giant transverse-mode electromecanical coupling factor of  $k_{31}$  over 80% and piezoelectric strain  $d_{31}$  constant of -2000 pC/N in PZNT91/09 and PMNT74/26 single crystals realized a monodomain single crystal by accurately controlling the domain structures. In addition, high-efficiency piezoelectric unimorph and bimorph are also discribed as the devices using giant  $k_{31}$  single crystals.

### 2. Giant electromechanical coupling factor of $k_{31}$ mode and piezoelectric $d_{31}$ constant in Pb[(Zn<sub>1/3</sub>Nb<sub>2/3</sub>)<sub>0.91</sub>Ti<sub>0.09</sub>]O<sub>3</sub> single-crystal plates

Ferroelectric single crystals made of compounds such as  $Pb[(Zn_{1/3}Nb_{2/3})_{0.91}Ti_{0.09}]O_3$  (PZNT91/09) have been attracting considerable attention, because of the large longitudinal-

mode electromechanical coupling factor of  $k_{33}$  over 92%. Since high-quality and large crystals are necessary to develop devices such as transducers for medical use, we have undertaken and succeeded in the fabrication of PZNT91/09 single crystals with large dimensions. In addition, for further applications to sensors and actuators, a large  $k_{31}$  ( $d_{31}$ ) mode as well as a large  $k_{33}$  ( $d_{33}$ ) mode are needed.

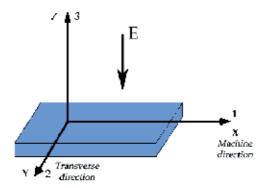

#### 2.1 Single-crystal sample preparation

The single crystals evaluated were grown by a solution Bridgman method with a Pt crucible supported at the bottom by a conical insulator stand. The crystals without Pt contamination from the crucible have the dimensions of 50 mm (2 inches) diameter, 35 mm height, and 325 g weight. The as-grown single crystals were cut along [100] of the original cubic direction confirmed by X-ray diffraction and from Laue photographs. The single-crystal samples with dimensions of  $4.0^{W}$ (width)x13<sup>L</sup>(length)x0.36<sup>T</sup>(thickness) mm for k<sub>31</sub>, k<sub>t</sub> and d<sub>31</sub> and  $4.2^{W}x4.2^{L}x12^{T}$  mm for k<sub>33</sub> and d<sub>33</sub> were prepared to evaluate the dielectric and piezoelectric properties. Gold electrodes for the following DC poling and electrical measurements were fabricated by conventional sputtering. Poling was conducted at 40 °C for 10 min by applying 1.0 kV/mm to obtain resonators with various vibration modes.

#### 2.1.1 What is "giant k<sub>31</sub> piezoelectricity"?

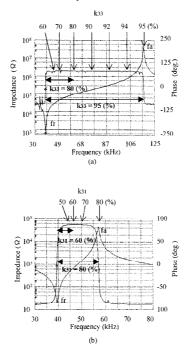

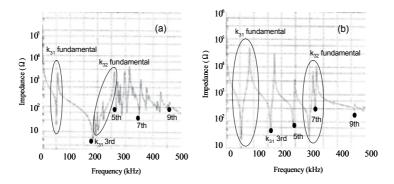

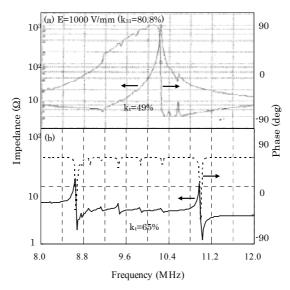

Figure 1 shows the frequency responses of the impedance in  $k_{33}$  and  $k_{31}$  modes in the cases of various coupling factors. It is easy to explain the wide frequency band, which corresponds to the difference between anti-resonant frequency (fa) and resonant frequency (fr), in higher coupling factors. An early work on a PZNT91/09 single crystal poled

Fig. 1. Frequency and phase responses of (a)  $k_{33}$  and (b)  $k_{31}$  fundamental modes in the cases of various coupling factors.

along [001] of the original cubic direction found that the values of  $k_{31}$  ( $d_{31}$ ) and  $k_{33}$  ( $d_{33}$ ) modes were 62% (-493 pC/N) and 92% (1570 pC/N), respectively. In a more recent work, the  $k_{31}$  ( $d_{31}$ ) mode of 53% (-1100 pC/N) and the  $k_{33}$  ( $d_{33}$ ) mode of 94% (2300 pC/N) were reported for Pb[( $Zn_{1/3}Nb_{2/3}$ )<sub>0.92</sub>Ti<sub>0.08</sub>]O<sub>3</sub> (PZNT92/08) single crystals poled along [001]. There are significant differences in the  $k_{31}$  and  $d_{31}$  modes between our result and the previous results, despite finding almost the same  $k_{33}$  (95%) and  $d_{33}$  (2500pC/N).

A large difference between  $k_{31}$ =80.8% and  $-d_{31}$ =1700 pC/N in this study and  $k_{31}$ =53-62% and  $-d_{31}$ =493-1100 pC/N in the previous studies for the single crystals is considered to be due to the following. It is well known that dielectric and piezoelectric properties are strongly affected by the quality of the crystals. It was pointed out that a small portion of opaque parts in the crystal wafer significantly reduces the electromechanical coupling factor of the crystals. Since PZNT91/09 crystals evaluated in this study have very high transparency with a minimum defect level thus far reported, due to better control of the Bridgman crystal growth, the highest  $k_{31}$  and  $d_{31}$  can be obtained.

#### 2.1.2 Where does "giant k<sub>31</sub> piezoelectricity" come from?

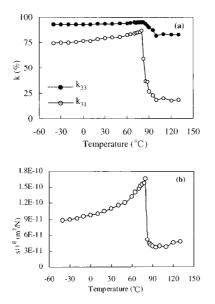

Figures 2(a) and 2(b) show the temperature dependences of  $k_{31}$ ,  $k_{33}$  and elastic compliance  $(s_{11}^{E})$ . Higher  $k_{31}$  and  $k_{33}$  were obtained in the rhombohedral phase below 80 °C. The values of  $s_{11}^{E}$  in the rhombohedral phase are larger than those in the tetragonal phase. Furthermore, the frequency constant (fc=frxL, where L is length), which corresponds to half the bulk wave velocity, of the  $k_{31}$  mode (fc<sub>31</sub> =522 Hz·m) is relatively small in comparison with that of lead zirconate titanate (PZT) ceramics ( $fc_{31}$ =1676 Hz·m). We believe that the high piezoelectricity in the PZNT91/09 single crystal is due to the mechanical softness of the rhombohedral phase, not the existence of a MPB, for easy deformation by the poling field. This concept may be supported by the result that high  $k_{33}$  (>90%) independent rhombohedral composition, PZNT91/09, of the such as PZNT92/08 or Pb[(Zn<sub>1/3</sub>Nb<sub>2/3</sub>)<sub>0.955</sub>Ti<sub>0.045</sub>]O<sub>3</sub> (PZNT95.5/4.5), was obtained.

Fig. 2. Temperature dependences of (a) electromechanical coupling factors ( $k_{31}$  and  $k_{33}$ ) and (b) elastic compliance ( $s_{11}^{E}$ ) in PZNT91/09 single crystal.

In conclusion of this part, frequency spectrum analysis of the responses to vibration modes was carried out in detail utilizing large PZNT91/09 single crystals of high quality. Giant  $k_{31}$  and  $d_{31}$ , as well as  $k_{33}$  and  $d_{33}$ , were obtained by efficient and uniform DC poling, it means a mono-domain structure in the single-crystal plate as described the next part. The crystals with these giant  $k_{31}$  and  $d_{31}$  will be applied for use in sensors and actuators with high performance.

#### 2.2 Origin of giant piezoelectricity in PZNT91/09 single-crystal plates

In order to clarify the origin of giant piezoelectricity in PZNT91/09 single-crystal plates, the poling field dependence of dielectric and ferroelectric properties were investigated in single-crystal samples with demension of  $4.0^{W}x13^{L}x0.36^{T}$  mm for  $k_{31}$ ,  $k_t$  and  $d_{31}$  and  $4.2^{W}x4.2^{L}x12^{T}$  mm for  $k_{33}$  and  $d_{33}$ . The poling field dependence was carried out as follows; the poling was conducted at 40 °C for 10 min while varying the poling field (E) from 0 to 2000 V/mm. After each poling, the dielectric and piezoelectric properties were measured at room temperature using an LCR meter, an impedance analyzer and a  $d_{33}$  meter. Moreover, the domain structures were observed under polarized light with crossed nicols by an optical microscope.

### 2.2.1 DC poling field dependence of dielectric constant, $d_{33}$ constant, $k_{31}$ , $k_t$ , $k_{33}$ and their frequency constants of $fc_{31}$ and $fc_t$

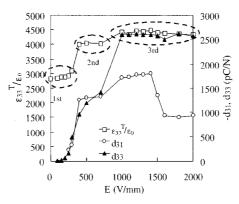

Figure 3 shows the effect of DC poling field (E) on dielectric constant ( $\epsilon_{33}T/\epsilon_0$ ) and piezoelectric d<sub>31</sub> and d<sub>33</sub> constants. There were three stages in  $\epsilon_{33}T/\epsilon_0$  with increasing E. The first stage was E<400 V/mm, the second stage was 400 V/mm≦E<1000 V/mm, and the third stage was E≥1000 V/mm. These stages in terms of dielectric constant mean that there are three thresholds of domain rotation and switching in the direction of the poling field. From our previous study, E of 300 V/mm in the first stage corresponds to the coercive field (Ec) and E of 180° domain clamping on PZNT91/09 single crystals. While d<sub>33</sub> has approximately the same tendency as the dielectric constant for the poling field, d<sub>31</sub> decreased abruptly over 1500 V/mm in the third stage. The giant -d<sub>31</sub> of nearly 1700 pC/N could be obtained at 1000 V/mm≦E<12000 V/mm. It was thought that the difference between d<sub>31</sub> and d<sub>33</sub> at 1500 V/mm≦E≤2000 V/mm was due to the difference in the domain structure in the directions of the length and the thickness for the sample plate (4.0<sup>W</sup>x13<sup>L</sup>x0.36<sup>T</sup> mm).

Fig. 3. Poling field dependence of dielectric constant, and piezoelectric d<sub>31</sub> and d<sub>33</sub> constants (poling temperature: 40 °C, time: 10 min).

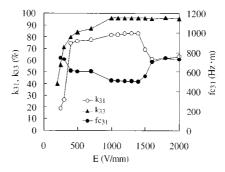

Figure 4 shows the effect of poling field (E) on the electromechanical coupling factors ( $k_{31}$ ,  $k_{33}$ ) and frequency constant ( $f_{C_{31}}$ ). The plots of the poling field vs  $k_{33}$  and  $k_{31}$  were almost the same as the plots of the poling field vs  $d_{33}$  and  $d_{31}$  shown in Fig. 3. While the giant  $k_{31}$  of over 80% was obtained at 1000 V/mm $\leq$ E<1500 V/mm, the highest  $k_{33}$  of over 90% was obtained at 1000 V/mm $\leq$ E<2000 V/mm. Furthermore, the frequency constant of the  $k_{31}$  mode ( $f_{C_{31}}$ ) showed the lowest value of nearly 500 Hz·m at 1000 V/mm $\leq$ E<1500 V/mm. Therefore, it was found that the giant  $k_{31}$  ( $d_{31}$ ) and the minimum  $f_{C_{31}}$  appeared simultaneously at the specific poling fields of 1000 V/mm $\leq$ E<1500 V/mm. With increasing E from 1500 V/mm to 2000 V/mm,  $k_{31}$  decreased and  $f_{C_{31}}$  increased abruptly without any change in  $k_{33}$ . The behavior observed for the poling field vs  $k_{31}$  ( $d_{31}$ ) and  $f_{C_{31}}$  in the third region suggested that a mono-domain in the length direction (the direction perpendicular to the poling field) was achieved at 1000 V/mm $\leq$ E<1500 V/mm, and further, the mono-domain changed into a number of domains (multi-domains in the plate) in the length direction at 1500 V/mm.

Fig. 4. Poling field dependence of  $k_{31}$  and  $k_{33}$ , and frequency constant  $fc_{31}$  (poling temperature: 40°C, time: 10 min).

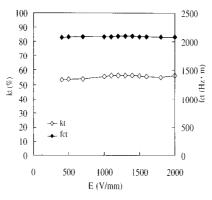

Figure 5 shows the effect of poling field (E) on electromechanical coupling factor ( $k_t$ ) and frequency constant ( $fc_t$ ). The  $k_t$  mode and  $fc_t$  correspond to the thickness vibration for the sample plate ( $4.0^w \times 13^L \times 0.36^T$  mm). While  $k_{33}$  increased from 80% to 95% with increasing E from 400 V/mm to 2000 V/mm in Fig. 4,  $k_t$  and  $fc_t$  were independent of the poling field in the same range of E. We believe the difference in the poling field dependence between  $k_{33}$  and  $k_t$  is due to the effect of the domain structure on the vibrations of  $k_{33}$  and  $k_t$  modes in the thickness direction for the sample plate.

Fig. 5. Poling field dependence of  $k_t$  and frequency constant fc<sub>t</sub> (poling temperature: 40 °C, time: 10 min).

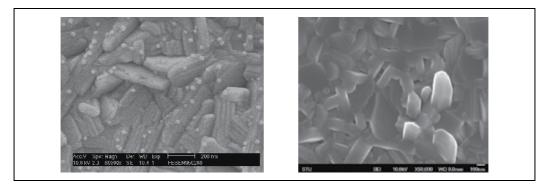

#### 2.2.2 Domain structures of single-crystal plates at various poling fields

After each poling at E, both the surfaces of the sample plate  $(4.0^{W}x13^{L}x0.36^{T} \text{ mm})$  were polished and the domain structure in the plate area  $(4.0^{W}x13^{L} \text{ mm})$  was observed under polarized transmission light with crossed nicols. The frequency responses of the impedance in  $k_{31}$  mode were also measured at every poling field. Figures  $6(a)\sim 6(d)$  show the domain structures and the frequency responses in  $k_{31}$  mode. The as-grown crystal mainly had black and brown stripes as shown in Fig. 6(a). We believe that the stripes consist of 180° domains alongside their domain walls. By applying E of 350 V/mm for 10 min at 40 °C, the brown area increased, the boundaries between black and brown stripes became unclear and the single response of the  $k_{31}$  (47%) mode was obtained [Fig. 6(b)]. A mono-domain crystal without domain walls was confirmed to exist at E=1000 V/mm. In addition, the giant  $k_{31}$  of nearly 80% appeared in the mono-domain crystal with the single response and with the minimum frequency constant of  $f_{c_{31}}$  mode [Fig. 6(c)]. The

Fig. 6. Poling field dependence of domain structures in sample plate area ( $4.0^{W}x13^{L}$  mm) and frequency responses of impedance and phase on  $k_{31}$  mode; (a) as-grown (before poling), (b) E=350 V/mm, (c) E=1000 V/mm and (d) E=2000 V/mm; the thickness of the plate is 0.36 mm and the broken line in Fig. 6(d) indicates a domain boundary.

frequency constant ( $fc_{31}$ ) corresponds to half the bulk wave velocity ( $v_{31}$ ), and further, there is a relationship between the Young's modulus (Y) of the crystal and  $fc_{31}$  as follows:

$$v_{31} = 2 x fc_{31} = 2 x fr x L = Y^{1/2} \rho^{-1/2}$$

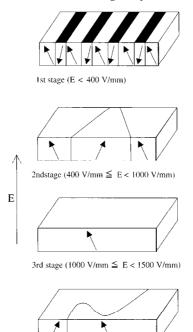

where fr and  $\rho$  are the resonant frequency of k<sub>31</sub> mode and the bulk density of the crystal, respectively. Therefore, it is said that the most softened (i.e., with the lowest  $v_{31}$  or  $f_{C_{31}}$ ) PZN91/PT09 crystals poled by the specific poling conditions (1000 V/mm $\leq$ E<1500 V/mm at 40 °C for 10 min) are essential to achieve the giant  $k_{31}$  and  $d_{31}$ . With E greater than 1500 V/mm, since the mono-domain changed into the muluti-domains, the single response of the  $k_{31}$  mode was divided into two responses and the value of fr or  $fc_{31}$  increased. As a consequence,  $k_{31}$  was reduced to 63% [Fig. 6(d)]. It was thought that the reason only a few domains were formed was the generation of strain in the direction perpendicular to the poling field - namely, not in the sample thickness of 0.36<sup>T</sup> mm but in the sample plate area of 4.0<sup>w</sup>x13<sup>L</sup> mm, in the crystal poled by the higher poling field. This is summarized schematically in Fig. 7 for the relationships among the poling fields and the domain structures. In addition, Table 1 shows the relationships among the Young's modulus (Y), k<sub>33</sub> and  $k_{31}$  for various materials. It is found that the Y (0.89x10<sup>10</sup> N/m<sup>2</sup>) in rhombohedral PZNT91/09 with giant  $k_{31}$  is one order of magnitude smaller than the Y (6~9x10<sup>10</sup> N/m<sup>2</sup>) of PZT ceramics and, roughly speaking, one order of magnitude larger than the Y  $(0.05 \times 10^{10})$  $N/m^2$ ) of rubber. Therefore, we believe that the giant  $k_{31}$  of over 80% arises from the remarkable softness of the domain controlled single crystal due to the poling field.

3rd stage (1500 V/mm  $\leq E \leq 2000$  V/mm)

Fig. 7. Schematics of domain structures ( $\sqrt[n]{\sqrt{n}}$ ) in PZNT91/09 single crystal under various poling fields; the arrow of E shows the direction of the poling field.

| Material                    | $Y (\times 10^{10} \text{ N/m}^2)$ | k33 (%) | $\frac{k_{31} (\%)}{80}$ |  |

|-----------------------------|------------------------------------|---------|--------------------------|--|

| PZNT 91/09                  | 0.89* (2.58)**                     | 95      |                          |  |

| Soft PZT ceramics           | 6                                  | 70      | 40                       |  |

| Hard PZT ceramics           | 9                                  | 60      | 30                       |  |

| PbTiO <sub>3</sub> ceramics | 13                                 | 50      | б                        |  |

| BaTiO <sub>3</sub> ceramics | 11                                 | 45      | 15                       |  |

| Steel                       | 20                                 |         |                          |  |

| Rubber                      | 0.05                               |         |                          |  |

\*Rhombohedral phase, \*\*Tetragonal phase.

Table 1. Relationships among Young's modulus (Y), k<sub>33</sub> and k<sub>31</sub> in various materials.

In conclusion of this part, the origin of PZNT91/09 single crystals with giant  $k_{31}$  of over 80% and  $-d_{31}$  constant nearly 1700 pC/N were due to a mono-domain structure in the crystal plates. Controlling the poling conditions, the crystal plate with multi-domains changed into one having the mono-domain in the direction perpendicular to the poling field as well as in the direction parallel to the poling field. Futhermore, this ferroelectric domain controlled single crystal by a poling field possessed the lowest frequency constant of  $f_{C_{31}}$ .

#### 3. Giant k<sub>31</sub> in Pb(Mg<sub>1/3</sub>Nb<sub>2/3</sub>)O<sub>3</sub>-PbTiO<sub>3</sub> single-crystal plates

Another relaxor single crystal of  $Pb(Mg_{1/3}Nb_{2/3})O_3$ -PbTiO<sub>3</sub> (PMNT) is investigated in detail regarding the  $k_{31}$  mode and the conditions for obtaining giant  $k_{31}$  and  $d_{31}$  constant are clarified.

### 3.1 Crystal plane dependence of giant $k_{31}$ in Pb(Mg<sub>1/3</sub>Nb<sub>2/3</sub>)O<sub>3</sub>-PbTiO<sub>3</sub> single-crystal plates

Recently, a giant  $k_{31}$  over 86% and a piezoelectric  $d_{31}$  constant of nearly -2100 pC/N were found for a (100) Pb[( $Zn_{1/3}Nb_{2/3}$ )<sub>0.91</sub>Ti<sub>0.09</sub>]O<sub>3</sub> (PZNT91/09) single crystal poled in the [001] direction. In order to realize giant  $k_{31}$ , it was the significant relationship between the crystal plane and the poling direction. Moreover, it was clarified that the giant  $k_{31}$  and  $d_{31}$  constant could be obtained with a poling temperature of 40 °C in the rhombohedral phase and with sufficient poling fields of 1000~1500 V/mm. The origin of the giant  $k_{31}$  and  $d_{31}$  constant was found to be due to the mono-domain structure in the direction perpendicular to the poling field as well as in the direction parallel to the poling field. In this part, we investigate the relationships between the crystal planes and the poling direction in (1-x)Pb(Mg<sub>1/3</sub>Nb<sub>2/3</sub>)O<sub>3</sub>xPbTiO<sub>3</sub> [PMNT(1-x)/x] single-crystal plates to obtain giant  $k_{31}$ .

#### 3.1.1 Realization of giant k<sub>31</sub> in PMNT plates

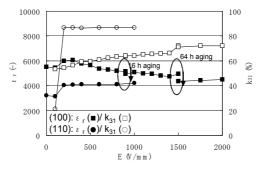

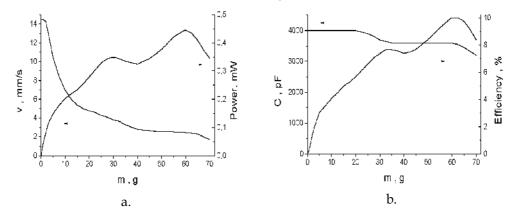

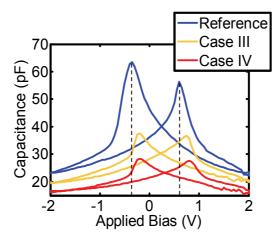

Figure 8 shows the DC poling field (E) dependence of relative dielectric constant ( $\epsilon_r$ ) and  $k_{31}$  in (100) PMNT68/32 and (110) PMNT74/26 single-crystal plates. The  $\epsilon_r$  (**•**) in (100) PMNT has a peak at E=300 V/mm and decreases with increasing E. There is aging in  $\epsilon_r$  (**•**) and  $k_{31}$  (**□**) for (100) PMNT, after 16 and 64 h at room temperature. The same phenomena were observed in (110) PZNT91/09 single-crystal plates poled in the [110] direction. On the other hand, the  $\epsilon_r$  (**•**) and  $k_{31}$  (**○**) in (110) PMNT increased abruptly at E=200 V/mm and reached constant values without aging. It was found that a giant  $k_{31}$  of over 86% was obtained at E $\geq$  200 V/mm in (110) PMNT single-crystal plates at the poling temperature of 40 °C.

Fig. 8. DC poling field dependence of  $\varepsilon_r$  and  $k_{31}$  in (100) and (110) PMNT single-crystal plates.

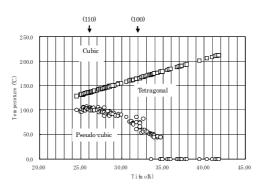

The effects of poling temperature on  $k_{31}$ ,  $d_{31}$  constant and the frequency constant (half of the bulk wave velocity) of the  $k_{31}$  mode (fc<sub>31</sub>) in (110) PMNT74/26 single-crystal plates are shown in Fig. 9. The temperatures of 40 °C ( $\circ$ ), 100 °C ( $\Box$ ) and 120 °C ( $\Delta$ ) correspond to the pseudo-cubic phase, the phase boundary between pseudo-cubic and tetragonal phases, and the tetragonal phase, respectively (Fig. 10). It is confirmed that giant  $k_{31}$  and  $d_{31}$  constant were obtained to polarize (110) PMNT plates in pseudo-cubic phase (the poling temperature of 40 °C), while applying  $E \ge 200$  V/mm. In addition, the giant  $k_{31}$  and  $d_{31}$  constant were accompanied by the lowest fc<sub>31</sub>, nearly 700 Hz·m. These results were the same as those of (100) PZNT91/09 single-crystal plates with giant  $k_{31}$ .

Fig. 9. DC poling field dependence of  $k_{31}$ ,  $d_{31}$  and  $fc_{31}$  in (110) PMNT74/26 single-crystal plates at poling temperatures of 40 °C ( $\circ$ ), 100 °C ( $\Box$ ) and 120 °C ( $\triangle$ ).

Fig. 10. Phase diagram of  $Pb(Mg_{1/3}Nb_{2/3})O_3$ -PbTiO<sub>3</sub> single crystals grown by a solution Bridgman method.

#### 3.1.2 Impedance response analysis of giant k<sub>31</sub>

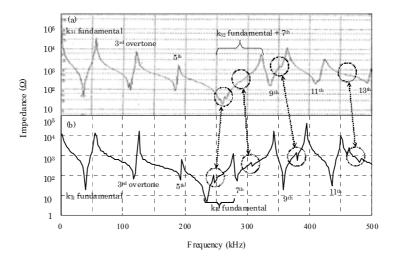

Figures 11(a), (b) and Figs. 12 (a), (b) show the frequency responses of impedance on the fundamental  $k_{31}$  modes and up to 500 kHz in the cases of (100) and (110) PMNT single-crystal plates poled at 40 °C, E=1000 V/mm and 10 min. The values of  $k_{31}$  in (100) and (110) PMNT single-crystal plates were 42.6% and 84.6% (giant  $k_{31}$ ), respectively. The  $k_{31}$  fundamental and its overtones were observed to have complicated spurious responses in (100) PMNT in Fig. 12(a). However, the  $k_{31}$  fundamental and its 3rd, 5th, 7th and 9th overtones were confirmed not to have spurious responses in (110) PMNT with giant  $k_{31}$  in Fig. 12(b), and were also confirmed the frequency responses of impedance in (100) PZNT91/09 single-crystal plates with giant  $k_{31}$ . Therefore, it is found that a single vibration was generated in the direction of the length (L). In order to clarify the resonance response near 300 kHz [inside the ellipse in Fig. 12(b)], the original single-crystal plate (13<sup>L</sup>x4.0<sup>W</sup>x0.47<sup>T</sup> mm) was cut to the small plate dimensions (0.97<sup>L</sup>x4.0<sup>W</sup>x0.47<sup>T</sup> mm). The  $k_{32}$  in

Fig. 11. Impedance and phase responses of the fundamental  $k_{31}$  mode in (a) (100) and (b) (110) PMNT single-crystal plates.

Fig. 12. Frequency responses of impedance in fully poled (a) (100) and (b) (110) PMNT single-crystal plates (DC poling conditions: 40 °C, 1000 V/mm, 10 min).

the width (W) direction was 69%, which was calculated from the resonance response of the small plate. Furthermore, the frequency constants on the  $k_{31}$  (length direction) and  $k_{32}$  (width direction) modes became 680 Hz·m and 1425 Hz·m, respectively. Consequently, it was found that the (110) PMNT single-crystal plate with giant  $k_{31}$  possessed an anisotropy in the frequency constant on the  $13^{L}x4.0^{W}$  mm plate and consisted of a mono-domain as in the case of the (100) PZNT91/09 single-crystal plate with giant  $k_{31}$ .

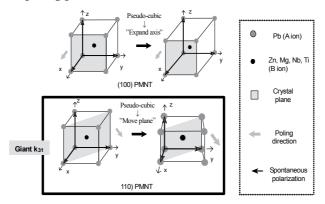

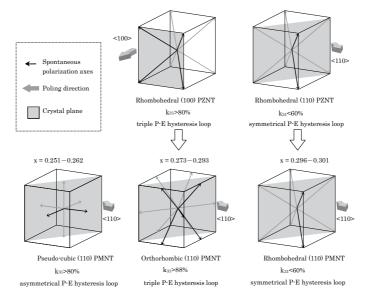

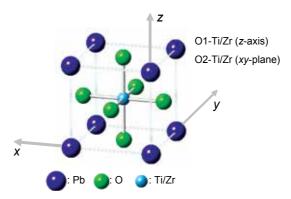

#### 3.1.3 Relationship between crystal plane and poling direction

The mechanism for realizing giant  $k_{31}$  can be explained by using the crystal plane and poling direction. Figure 13 shows the relationship between the crystal plane, which determines the direction of the spontaneous polarization, and the poling direction in (100) and (110) PMNT single-crystal plates. While applying the poling field to the (100) PMNT single-crystal plate at a poling temperature of 40 °C (pseudo-cubic phase), the poling field only acts to expand the x-axis in the direction of the poling field. In the (110) PMNT plate, the poling field acts to generate strain via the expansion of the x and y-axes (Fig. 13), which moves the ferroelectric domains on the (110) plane. While the domain structure on the (110) plane became singular due to the generated strain, it is thought that the anisotropy of the frequency constants on the  $k_{31}$  and  $k_{32}$  modes appeared and the giant value of the  $k_{31}$  mode in (110) PMNT was achieved through the poling process.

Fig. 13. Relationship between crystal plane, direction of the spontaneous polarization and poling direction in (100) and (110) PMNT single-crystal plates at 40 °C (pseudo-cubic phase).

Table 2 shows the values of  $k_{31}$ ,  $k_{32}$ ,  $d_{31}$  and  $d_{33}$  constants in PMNT and PZNT single-crystal plates with various crystal planes. Although giant  $k_{31}$  and  $d_{31}$  constant were obtained in the (110) PMNT plate, a large  $d_{33}$  constant (2420 pC/N) was realized in the (100) PMNT plate. On the other hand, giant  $k_{31}$ ,  $d_{31}$  constant, and large  $d_{33}$  constant (2400 pC/N) were obtained simultaneously in the (100) PZNT91/09 plate. Therefore, it was clarified that giant  $k_{31}$ ,  $d_{31}$  and  $d_{33}$  constants appeared in the peculiar combination of the crystal plane and poling direction in the relaxor single crystals. Moreover, there was anisotropy on the  $k_{31}$  (length direction) and  $k_{32}$  (width direction) modes in (110) PMNT with giant  $k_{31}$  as well as in (100) PZNT with giant  $k_{31}$ .

| Crystal | Single  | k <sub>31</sub> | -d <sub>31</sub> | kt  | d <sub>33</sub> | k <sub>32</sub> | Pr             | Ec     | A aima |

|---------|---------|-----------------|------------------|-----|-----------------|-----------------|----------------|--------|--------|

| plane   | crystal | (%)             | (pC/N)           | (%) | (pC/N)          | (%)             | $(\mu C/cm^2)$ | (V/mm) | Aging  |

| (100)   | PZNT    | 86              | 2100             | 55  | 2400            | 42              | 35             | 600    | Good   |

| (100)   | PMNT    | 65              | 1030             | 60  | 2420            |                 | 22             | 300    | NG     |

| (110)   | PZNT    | 30~60           | 300~720          | 40  | 530~1030        |                 |                |        | NG     |

| (110)   | PMNT    | 87              | 1320             | 48  | 970             | 69              | 30             | 200    | Good   |

| (111)   | PZNT    | 20              | ~170             | 50  | 190~560         |                 |                |        | Good   |

Table 2. Giant  $k_{31}$  and  $d_{31}$  constant in PMNT and PZNT single-crystal plates with various crystal planes.  $k_t$  is the coupling factor of thickness vibration in a plate, and piezoelectric  $d_{33}$  constant was measured with a  $d_{33}$  meter.

In conclusion of this part, giant  $k_{31}$  over 86% in (110) PMNT single-crystal plates was realized in order to control the relationship between the crystal plane, which determines the direction of the spontaneous polarization, and the poling direction. The plate with giant  $k_{31}$  shows the impedance responses with a single vibration generated in the length direction. It is thought that the origin of giant  $k_{31}$  is the mono-domain structure in the plate.

#### 3.2 Chemical composition dependnce of ginat k<sub>31</sub> in PMNT single-crystal plates

A giant electromechanical coupling factor of  $k_{31}$  mode of more than 86% was found for (100)  $Pb[(Zn_{1/3}Nb_{2/3})_{0.91}Ti_{0.09}]O_3$  (PZNT91/09) single-crystal plates ( $13^Lx4.0^Wx0.36^T$  mm) and (110)  $Pb[(Mg_{1/3}Nb_{2/3})_{0.74}Ti_{0.26}]O_3$  (PMNT74/26) single-crystal plates ( $13^Lx4.0^Wx0.47^T$  mm) poled in the [001] and [110] directions, respectively. In this part, the chemical composition dependence of  $k_{31}$  mode in PMNT single-crystal plates with (110) plane is investigated in detail and furthermore, the relationships between the crystal phase after poling and giant  $k_{31}$  are clarified.

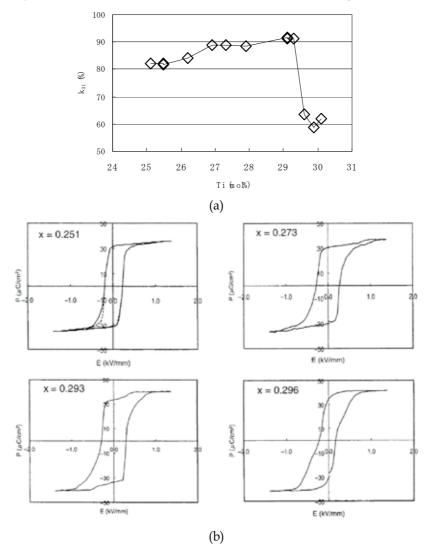

#### 3.2.1 Ti composition dependence of ginat k<sub>31</sub>

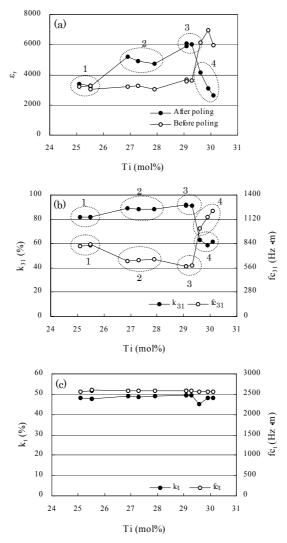

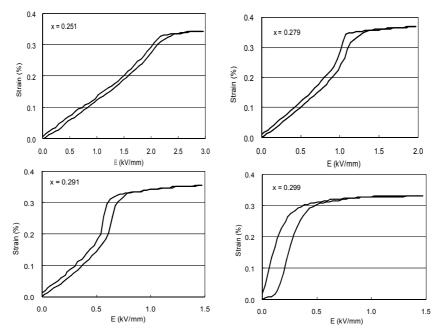

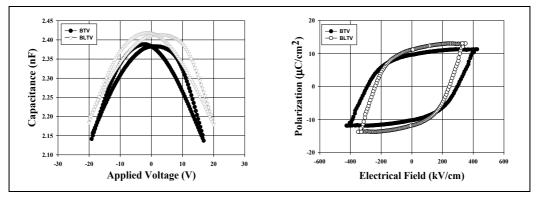

The (110) PMNT(1-x)/x (x=0.251~0.301) single-crystal plates in this study have pseudocubic phase before poling below 100 °C (x=0.25) and 90 °C (x=0.30). Figure 14 shows the relationships between relative dielectric constant ( $\varepsilon_r$ ) before and after poling [Fig. 14(a)], k<sub>31</sub> and the frequency constant (half the bulk wave velocity) of k<sub>31</sub> mode (fc<sub>31</sub>) [Fig. 14(b)], and the electromechanical coupling factor of the thickness vibration mode of the plate (k<sub>t</sub>) and frequency constant of k<sub>t</sub> mode (fc<sub>t</sub>) [Fig. 14(c)] versus Ti composition (x) in (110) PMNT(1x)/x single-crystal plates. Although  $\varepsilon_r$  ( $\circ$ ) in (110) PMNT is almost constant and abruptly increases for x>0.293 before poling,  $\varepsilon_r$  ( $\bullet$ ) after poling is divided into four groups 1~4: group 1 (x=0.251~0.255), group 2 (x=0.269~0.279), group 3 (x=0.291~0.293) and group 4 (x=0.296~0.301) in Fig. 14(a). Since the groups of  $\varepsilon_r$  correspond to the groups of the domain structure, it was thought that the PMNT single-crystal plates processed different domain structures in each group after DC poling. On the other hand,  $k_{31}$  increases with an increase in x and reaches a maximum of 92% at x=0.291. After that,  $k_{31}$  suddenly decreases with x as shown in Fig. 14(b). The fc<sub>31</sub> also has four groups and shows an opposite tendency compared with  $k_{31}$  vs x. This means that higher  $k_{31}$  is obtained for lower fc<sub>31</sub>, because the decrease in the number of domain boundaries through the improvement of the poling process in the single-crystal plates leads to a decrease in stiffness. Since  $k_t$  and fc<sub>t</sub> are independent of x in Fig. 14(c), the domain structures are almost the same in the thickness direction of the plates. Therefore, the chemical composition dependence of  $\varepsilon_r$  after poling,  $k_{31}$  and fc<sub>31</sub> appears to be dependent on the domain structure in the plate (13<sup>L</sup>x4.0<sup>W</sup> mm).

Fig. 14. Ti composition dependence of (a)  $\varepsilon_r$  before and after poling, (b)  $k_{31}$ ,  $fc_{31}$  and (c)  $k_t$ ,  $fc_t$  in PMNT(1-x)/x single-crystal plates.

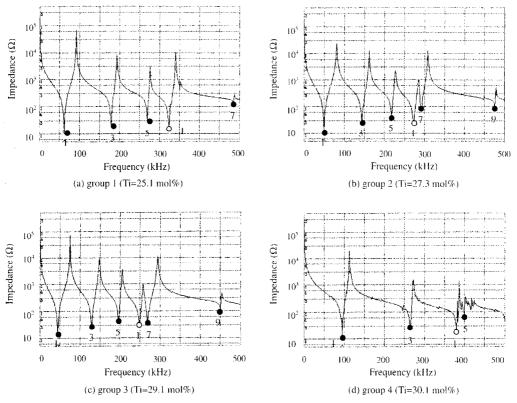

#### 3.2.2 Impedance response analysis of ginat k<sub>31</sub>

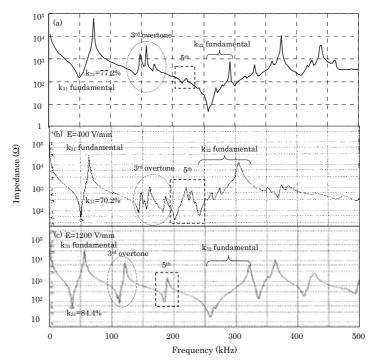

Figure 15 shows the frequency responses of impedance to 500 kHz in the cases of groups  $1\sim4$  in Fig. 14. The k<sub>31</sub> fundamental and their odd-number overtones of 3rd, 5th, 7th and 9th with the k<sub>32</sub> fundamental vibration (width direction) were confirmed without spurious responses in groups  $1\sim3$  in (110) PMNT with giant k<sub>31</sub>, as well as the frequency response of impedance in the (100) PZNT91/09 single-crystal plate with giant k<sub>31</sub>. However, the k<sub>31</sub> fundamental and their overtones were observed with complicated spurious responses in group 4 in the (110) PMNT with k<sub>31</sub>=60%. Therefore, it was found that a single vibration is generated in the direction of the length (L) in the (110) PMNT with giant k<sub>31</sub>, similar to the case of the (100) PZNT91/09 single-crystal plate with giant k<sub>31</sub>.

Fig. 15. Frequency responses of impedance in fully poled (110) PMNT(1-x)/x single-crystal in cases of (a) group 1, (b) group 2, (c) group 3 and (d) group 4 ( $\bullet$ 1: k<sub>31</sub> fundamental vibration,  $\bullet$ 3-9: k<sub>31</sub> odd-number overtones,  $\circ$ 1: k<sub>32</sub> fundamental vibration; DC poling conditions: 40°C, 1000 V/mm, 10 min).

#### 3.2.3 Crystal phase to realize ginat k<sub>31</sub>

A mechanism to realize giant  $k_{31}$  can be explained by the crystal plane, which strongly affects the direction of the spontaneous polarization and poling direction. Giant  $k_{31}$  in relaxor single-crystal plates can be achieved when the poling field generates sufficient strain to move the ferroelectric domains in the plates ( $13^{L}x4.0^{W}$  mm), not merely to expand the spontaneous polarization axes in the direction of the poling field. We will

discuss in detail the relationships between crystal planes, spontaneous polarization axes and poling direction in (110) PMNT single-crystal plates (groups  $1\sim4$ ) in comparison with the cases of (100) and (110) PZNT91/09 single-crystal plates (see Fig. 27 in the paragraph 4.2.3). Furthermore, it will be clarified that the crystal phases after poling can be estimated by the value of  $k_{31}$  and the combination between the directions of the spontaneous polarization axes and the poling field, which generates the strain sufficient to move the domains in the plates.

In conclusion of this part, giant  $k_{31}$  of more than 80% in (110) PMNT single-crystal plates was clarified to possess Ti composition dependence. The frequency response of impedance in (110) PMNT single-crystal plates with giant  $k_{31}$  was composed of a single vibration in the length direction. In addition, the domain movement to realize giant  $k_{31}$  in the crystal plate was due to the combination between the direction of the spontaneous polarization and the poling direction.

#### 4. Other characteristics investigation

The giant  $k_{31}$  and  $d_{31}$  constant in the PZNT91/09 and PMNT(1-x)/x single-crystal plates were due to the generation of a single vibration in the length direction. However, there is as yet no evidence of the close relationship between the mono-domain plate with a giant  $k_{31}$ , which means a single vibration body, and the single vibration in the plates measured from the impedance response.

Furthermore, the P-E hysteresis loops and the relationship to electric field (E) vs strain measurement were investigated from the viewpoints of giant  $k_{31}$ .

### 4.1 Frequency response analysis by finite element method in relaxor single-crystal plates with ginat $k_{\rm 31}$

In this part, the frequency response analysis of impedance on the giant  $k_{31}$  mode is evaluated by a finite element method (FEM) in order to characterize the mono-domain plates. Since the number of ferroelectric domains in the plates corresponds to the number of piezoelectric vibration bodies, the frequency response analysis by FEM was applied to the evaluation of their domain structures. Moreover, the domain behavior of the PZNT91/09 single-crystal plates is also investigated by FEM, particularly focusing on the 3rd overtone of the  $k_{31}$  fundamental vibration.

#### 4.1.1 FEM application

Resonators composed of relaxor single-crystal plates, the dimensions of which are  $13^{L}x4.0^{W}x0.36^{T}$  mm, with a giant  $k_{31}$  in PZNT91/09 with the (100) plane and PMNT74/26 with the (110) plane were analyzed using a commercial analysis program (ANSYS) by FEM. For the FEM simulation, an electric field of 1.0 V/mm to simulate the impedance responses was added in the thickness direction of the plate resonators because the actual voltage to be measured was 0.5 V by the impedance analyzer. The material constants obtained from the measured and reference data on the relaxor single crystals were used to calculate the impedance responses. The numbers of the elements and nodes for FEM were 800 pieces and 4271 points, respectively. Piezoelectric equations were applied to the orthorhombic phase. Furthermore, Poisson ratio in the length direction ( $k_{31}$  mode) and width direction ( $k_{32}$  mode)

was measured from the impedance responses by single-crystal plate resonators with different dimensions. In order to evaluate domain structures in the single-crystal plates, the relationships between the number of domains in the PZNT91/09 single-crystal plates and the 3rd overtone splitting of the  $k_{31}$  fundamental vibration were also investigated by FEM simulation.

Table 3 shows the coupling factors of  $k_{31}$ ,  $k_{32}$  and their frequency constants (fr x L or W, where fr is the resonant frequency) of  $fc_{31}$ ,  $fc_{32}$  in the relaxor single-crystal plates with a giant  $k_{31}$  of more than 80%. The values of  $\sigma_W^{E}/\sigma_L^{E}$  in Table 3 were calculated from the elastic compliance of  $s_{11}^{E}$  and  $s_{22}^{E}$  because  $\sigma_L^{E=-}(s_{12}^{E}/s_{11}^{E})$  and  $\sigma_W^{E=-}(s_{12}^{E}/s_{22}^{E})$ , where  $\sigma_L^{E}$  and  $\sigma_W^{E}$  are the Poisson ratios in the directions of length (13 mm) and width (4 mm), respectively. In the simulation,  $\sigma_W^{E}/\sigma_L^{E}$  was used to evaluate the crystal anisotropy of the relaxor single crystals, because of the difficulty in measuring the values of  $s_{12}$  in the single crystals. It was confirmed that there are large crystal anisotropies of  $s_{11}^{E}$  and  $s_{22}^{E}$  between the L and W directions and large differences in  $\sigma_W^{E}/\sigma_L^{E}$  of 3.4 (PZNT91/09) and 4.5 (PMNT74/26), respectively.

| single<br>crystal | k <sub>31</sub><br>(%) | k <sub>32</sub><br>(%) | fc <sub>31</sub><br>(Hz m) | fc <sub>32</sub><br>(Hz m) | $\frac{s_{11}^E}{(10^{-12}m^2/N)}$ | $\frac{s_{22}^E}{(10^{-12}m^2/N)}$ | $\sigma_W{}^E/\sigma_L{}^E$ |

|-------------------|------------------------|------------------------|----------------------------|----------------------------|------------------------------------|------------------------------------|-----------------------------|

| PZNT91/09         | 86                     | 42                     | 520                        | 830                        | 110                                | 32                                 | 3.4                         |

| PMNT74/26         | 87                     | 69                     | 683                        | 1425                       | 67                                 | 15                                 | 4.5                         |

Table 3. Material constants of relaxor single-crystal plates with giant k<sub>31</sub>.

Although the values of  $k_t$  (coupling factor of plate thickness vibration) and fct (frequency constant of the  $k_t$  mode) of the PZNT91/09 and PMNT74/26 single-crystal plates with a giant  $k_{31}$  were 57, 49% and 2087, 2588 Hz·m, respectively, it was thought the crystal structure of the plate resonators after DC poling becomes a field-induced phase such as the orthorhombic phase, because of the anisotropy of the bulk wave velocities (twofold the frequency constant) in the length (L=13 mm), width (W=4.0 mm) and thickness (T=0.36 mm) directions. Furthermore, a giant  $k_{31}$  could be obtained only in the orthorhombic phase after DC poling from the relationships between the directions of the spontaneous polarization and DC poling field to move domains in the plate (13<sup>L</sup>x 4.0<sup>W</sup> mm).

#### 4.1.2 Simulation of k<sub>31</sub> and k<sub>32</sub> modes by FEM

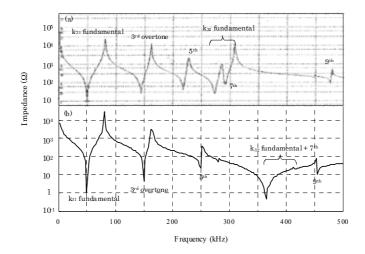

The change in the values of  $\sigma_W^E$  and  $\sigma_L^E$  affected the frequency response of impedance on  $k_{31}$  fundamental vibration, the overtones, and  $k_{32}$  fundamental vibration in the frequency range of 0~500 kHz. The simulated response at  $\sigma_W^E/\sigma_L^E=3.2$  ( $\sigma_L^E=0.089$ ,  $\sigma_W^E=0.29$ ) and  $s_{12}^E=-10$  (10<sup>-12</sup> m<sup>2</sup>/N) was well fitted to the measured responses, as shown by the arrows in Fig. 16, in the case of the PZNT91/09 single-crystal plate. The simulated data at  $\sigma_W^E/\sigma_L^E=4.9$  ( $\sigma_L^E=0.041$ ,  $\sigma_W^E=0.20$ ) and  $s_{12}^E=-3$  (10<sup>-12</sup> m<sup>2</sup>/N) in the PMNT74/26 single-crystal plates also showed the same result (Fig. 17). In the calculations, the values of  $s_{12}^E$  were chosen to fit the simulated responses to the measured responses. Moreover, the Poisson ratio affected the value of  $k_{31}$  as well as the frequency response of impedance.

Fig. 16. Frequency responses of impedance on  $k_{31}$  and  $k_{32}$  modes in PZNT91/09 singlecrystal plates; (a) measured and (b) simulated data.

Fig. 17. Frequency responses of impedance on  $k_{31}$  and  $k_{32}$  modes in PMNT74/26 singlecrystal plates; (a) measured and (b) simulated data.

#### 4.1.3 Simulation of kt mode by FEM

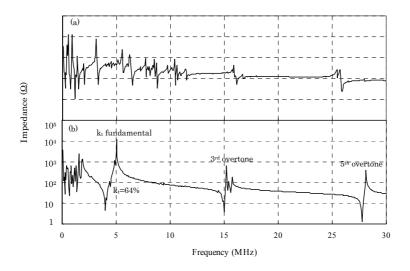

The impedance responses up to 30 MHz in Fig. 18 were calculated in the PZNT91/09 singlecrystal plates at  $\sigma_W^E/\sigma_L^E=3.2$ ,  $\sigma_L^E=0.045-0.13$ , and  $\sigma_W^E=0.15-0.41$ . The  $k_t$  fundamental vibration and the 3rd and 5th overtones of the  $k_t$  fundamental vibration were observed between  $\sigma_L^E=0.063-0.11$  and  $\sigma_W^E=0.20-0.35$ . In particular, sharp responses of the  $k_t$ fundamental vibration and the 3rd overtone were obtained between  $\sigma_L^E=0.080-0.098$  and  $\sigma_W^E=0.26-0.32$ . The simulated coupling factor of  $k_t=64\%$  was higher than that of  $k_t=57\%$ calculated from the measured response. It was clarified that the large difference in  $\sigma_W^E/\sigma_L^E=3.2$  and the suitable values of the elastic compliance, particularly  $-s_{12}E=9-11$  ( $10^{-12}$ m<sup>2</sup>/N), were key factors for the appearance of the  $k_t$  fundamental vibration and overtones. The simulated response of the PMNT74/26 single-crystal plates is shown in Fig. 19 at  $\sigma_W^E/\sigma_L^{E}=4.9$  ( $\sigma_L^E=0.041$ ,  $\sigma_W^E=0.20$ ) and  $s_{12}^E=-3$  ( $10^{-12}$  m<sup>2</sup>/N). The fundamental  $k_t$  mode ( $k_t=65\%$ ) and the 3rd overtone were observed independent of  $-s_{12}^E$  values between  $1\sim7$  ( $10^{-12}$  m<sup>2</sup>/N). In the calculations, the values of  $-s_{12}^E$  were chosen at a Poisson ratio ( $\sigma_W^E$ ) within  $0\sim0.5$ .

Fig. 18. Frequency responses of impedance on  $k_t$  mode in PZNT91/09 single-crystal plates; calculation for (a)  $\sigma_W^E/\sigma_L^{E=3.2}$  ( $\sigma_L^{E=0.13}$ ,  $\sigma_W^E=0.41$ )/  $s_{12}^{E=-14}$  (10-12 m<sup>2</sup>/N) and (b)  $\sigma_W^E/\sigma_L^{E=3.2}$  ( $\sigma_L^{E=0.089}$ ,  $\sigma_W^E=0.29$ )/  $s_{12}^{E=-10}$  (10-12 m<sup>2</sup>/N).

Fig. 19. Frequency responses of impedance on  $k_t$  mode in PMNT74/26 single-crystal plates; calculation for  $\sigma_W^E/\sigma_L^{E=4.9}$  ( $\sigma_L^{E=0.041}$ ,  $\sigma_W^E$  =0.20) and  $s_{12}^{E=-3}$  (10<sup>-12</sup> m<sup>2</sup>/N).

Figure 20 shows the impedance and phase responses of  $k_t$  fundamental vibration in the PZNT91/09 single-crystal plates. The impedance response consisted of four peaks split into ①-④ in the cases of the simulated and the measured responses. Herein, the PZNT91/09 plate resonator with a giant  $k_{31}$  of 84% was prepared under the poling conditions of a DC poling field (E) of 1200 V/mm. Although the simulation for the splitting was calculated from the values of  $\sigma_W^E/\sigma_L^E=3.2$  ( $\sigma_L^E=0.089$ ,  $\sigma_W^E=0.29$ ) and  $s_{12}^E=-10$  ( $10^{-12}$  m<sup>2</sup>/N), the splitting of the four peaks occurred in the case of a giant  $k_{31}$  in the PZNT91/09 single-crystal plates. Therefore, it was confirmed that the simulation data were exactly fitted to the measured data in both the

cases of the generation of the  $k_t$  mode and the impedance and phase responses of the  $k_t$  fundamental vibration. The impedance and phase responses of the  $k_t$  fundamental vibration of PMNT74/26 single-crystal plates are shown in Fig. 21 [ $\sigma_W^E/\sigma_L^E=4.9$  ( $\sigma_L^E=0.041$ ,  $\sigma_W^E=0.20$ ) and  $s_{12}^E=-3$  (10<sup>-12</sup> m<sup>2</sup>/N)] in comparison with the measured responses. The simulated impedance and phase responses were well fitted to the measured responses.

Fig. 20. Frequency responses of impedance and phase on  $k_t$  fundamental vibration in PZNT91/09 single-crystal plates; (a) measured and (b) simulated data.

Fig. 21. Frequency responses of impedance and phase on  $k_t$  fundamental vibration in PMNT74/26 single-crystal plates; (a) measured and (b) simulated data.

#### 4.1.4 Domain behavior evaluation by FEM

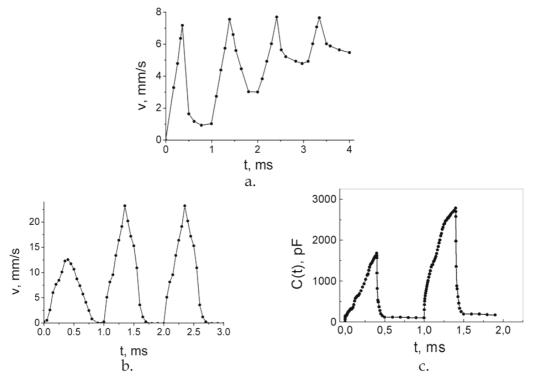

The 3rd overtone in the  $k_{31}$  mode was calculated to synthesize one-third of the simulated responses each in the cases of (i)  $\sigma_W^E/\sigma_L^E=2.5$  ( $\sigma_L^E=0.13$ ,  $\sigma_W^E=0.32$ ), (ii)  $\sigma_W^E/\sigma_L^E=2.4$  ( $\sigma_L^E=0.13$ ,  $\sigma_W^E=0.31$ ), and (iii)  $\sigma_W^E/\sigma_L^E=1.8$  ( $\sigma_L^E=0.17$ ,  $\sigma_W^E=0.31$ ). The simulated 3rd overtone response consisted of three peaks splitting in PZNT91/09 [shown in the circle of Fig. 22(a)]. On the other hand, the plate resonator DC poled at E=400 V/mm, the poling field of which is just below that required to obtain a giant  $k_{31}$ , also possesses the 3rd overtone with three peaks splitting [shown in the circle of Fig. 22(b)]. Therefore, it was thought that the PZNT91/09 single-crystal plate was composed of three vibration bodies, namely, three large domains with  $\sigma_W^E/\sigma_L^E$  values of 2.5, 2.4, and 1.8. Since the splitting of the three peaks of the 3rd overtone response formed one peak at E= 1200 V/mm obtaining a giant  $k_{31}$  of 84.4% (shown in the circle of Fig. 22(c)), it was proved that a mono-domain plate with a giant  $k_{31}$  was achieved. From our study, it was confirmed that frequency response analysis of impedance is an effective tool for the evaluation of domain structures in single-crystal plates.

Fig. 22. Frequency responses of impedance on 3rd overtone on  $k_{31}$  mode in PZNT91/09 single-crystal plates; (a) simulated data, (b) measured data of plate resonator DC poled at E=400 V/mm, and (c) measured data of plate resonator DC poled at E=1200 V/mm.

#### 4.1.5 Origin of giant k<sub>31</sub> from viewpoints of material constants

The most significant factors for realizing giant piezoelectricity in the  $k_{31}$  mode in the relaxor single-crystal plates were thought as follows: Firstly, large  $s_{11}^E$  values of 110 (10<sup>-12</sup> m<sup>2</sup>/N) in the PZNT91/09 single-crystal plates and 67 (10<sup>-12</sup> m<sup>2</sup>/N) in the PMNT74/26 single-crystal plates in the direction of length were required (Table 3). These  $s_{11}^E$  values are relatively

larger than that of 11-17 (10<sup>-12</sup> m<sup>2</sup>/N) in PZT ceramics. This means that the single-crystal plates with a giant  $k_{31}$  of more than 80% became markedly soft and showed a low Poisson ratio, particularly  $\sigma_L^{E}$ <0.1 after DC poling. Secondly, a large anisotropy of bulk wave velocity (twofold the frequency constant) accompanied by a large  $\sigma_W^{E}/\sigma_L^{E}$ =3.2-3.4 in PZNT91/09 single-crystal plates and a large  $\sigma_W^{E}/\sigma_L^{E}$ =4.5-4.9 in PMNT74/26 single-crystal plates was essential. Therefore, it was thought that the physical meaning of the above-mentioned large  $s_{11}^{E}$ , low  $\sigma_L^{E}$ , and large  $\sigma_W^{E}/\sigma_L^{E}$  originated from a field-induced phase such as the orthorhombic phase by DC poling because the combination of the directions of spontaneous polarization and poling field in the orthorhombic phase could only move domains in the plates.

In conclusion of this part, impedance response analysis by FEM was performed using the  $k_{31}$ ,  $k_{32}$ , and  $k_t$  modes in relaxor single-crystal plates with a giant  $k_{31}$ . It was found that a large anisotropy on the  $k_{31}$  and  $k_{32}$  modes was generated in the plate resonators with a giant  $k_{31}$ . As the Poisson ratios of the length and width directions in the plates were changed, the simulation results were well fitted to the measured impedance responses. These results could be explained by the material constants in a field-induced phase induced by the DC poling field. Furthermore, the domain behavior in the single-crystal plates was evaluated from the synthesized impedance response of three vibration bodies, i.e., three domains with different Poisson ratios.

### 4.2 Giant $k_{31}$ and $d_{31}$ in relaxor single-crystal plates evaluated using P-E hysteresis loops and strain

The longitudinal-mode electromechanical coupling factor  $k_{33}$  of over 90% was easy to obtain because the vibration direction of the  $k_{33}$  mode is the same as that of the poling field. However, the relationship between the giant  $k_{31}$  and  $k_{33}$  modes is not clarified. In this part, we could explain the relationship using P-E hysteresis loops and electric field (E) vs strain measurement from the viewpoint of giant  $k_{31}$ .

#### 4.2.1 P-E hysteresis loops

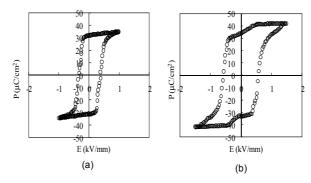

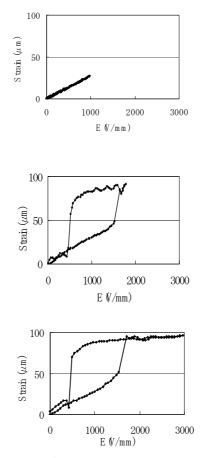

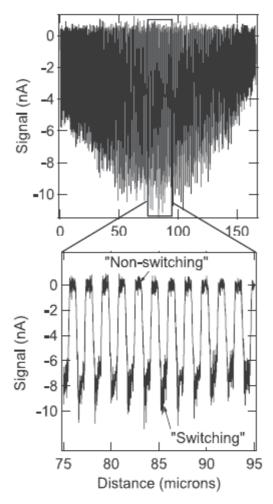

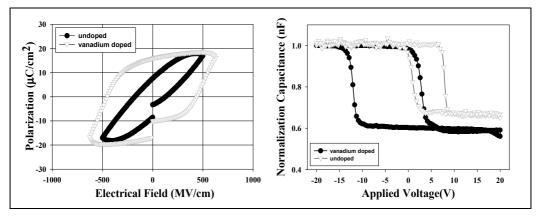

Figure 23 shows the electric field (E) dependence of P-E hysteresis loops in (100) PZNT91/09 single-crystal plate measured at 40°C by a high voltage test system. While a symmetrical P-E loop was observed at E = 1000 V/mm, a triple loop was generated as  $E \ge 1500$  V/mm in the case of the crystal plate with giant  $k_{31}$ .

Fig. 23. P-E hysteresis loops in PZNT91/09 single-crystal plates (a) before (E=1000 V/mm) and (b) after (E=1500 V/mm) the appearance of giant  $k_{31}$  over 80%.

Therefore, it was considered that the E of 1500 V/mm is a coercive field to obtain giant  $k_{31}$ . In addition, the triple loops were realized at 20-60 °C, in the rhombohedral phase of PZNT91/09.

Figure 24 shows the Ti composition (x) dependence of  $k_{31}$  [Fig. 24(a)] and P-E loops [Fig. 24(b)] in PMNT(1-x)/x single-crystal plate measured at 40 °C (pseudo-cubic phase) under E =1500 V/mm. Although a symmetrical P-E hysteresis loop was obtained at x = 0.296-0.301 in the plate with  $k_{31}$ =60%, triple loops were observed at x=0.273-0.293, and asymmetrical loops were observed at x=0.251-0.262 in the plates with giant  $k_{31}$  (>80%). The E=800 V/mm to generate the triple and asymmetrical loops corresponds to a coercive field to realize giant  $k_{31}$ .

Fig. 24. Ti composition (x) vs (a)  $k_{31}$  and (b) P-E hysteresis loops in PMNT(1-x)/x singlecrystal plates; x=0.251 (asymmetrical part near dotted lines), x=0.273/ 0.293 (triple loop at high E), and x=0.296 (symmetrical loop).

#### 4.2.2 Shrinkage strain characteristics

Figure 25 shows the dependence of the shrinkage strain measured at room temperature (rhombohedral phase of PZNT91/09) on the electric field (E) applied in the same direction as the DC poling field using a photonic sensor. A large hysteresis regarding E vs strain appeared between 400 and 1500 V/mm, the E of which (1500 V/mm) is the coercive field to obtain giant  $k_{31}$  in PZNT91/09. The large hysteresis for E vs shrinkage strain corresponds to the large hysteresis for E vs expansion strain in PZNT91/09 single crystal. Therefore, it was found that the large hysteresis for E vs strain (shrinkage and expansion) is due to the generation of giant  $k_{31}$ .

Fig. 25. Applied field (E) dependence of shrinkage strain in the length (13 mm) direction in PZNT91/09 single-crystal plate with giant  $k_{31}$ .

Figure 26 shows the Ti composition (x) dependence of E vs strain in PMNT(1-x)/x singlecrystal plates measured at room temperature (pseudo-cubic phase) and under E=1500 V/mm. By increasing x from 0.251 to 0.299, the linear relationship between E and strain changed into a line with a brake, and finally reached to a typical E vs strain similarly to the case of PZT ceramics. Furthermore, the E of 800 V/mm to generate the triple and asymmetric loops corresponded to the E of a break in the line for E vs strain.

Fig. 26. Ti composition dependence (x) of E vs strain in PMNT(1-x)/x single-crystal plates; x=0.251(linear line and small hysteresis), x=0.279/0.291 (line with break and intermediate hysteresis) and x=0.299 (large hysteresis like PZT ceramics).

### 4.2.3 Field-induced phase transition

A mechanism to realize giant  $k_{31}$  can be explained using the crystal plane, which closely affects the direction of the spontaneous polarization, and poling direction. Giant  $k_{31}$  in relaxor single-crystal plates can be achieved when the poling field generates strain to move the ferroelectric domains in the plates (13L×4.0W mm) and not to only expand the spontaneous polarization axes in the direction of the poling field. Figure 27 shows the relationships between crystal planes, spontaneous polarization axes, and poling direction in (110) PMNT(1-x)/x single-crystal plates (x=0.251-0.301) in comparison with the case of (100) and (110) PZNT91/09 single-crystal plates. The crystal phases after poling can be estimated using the values of  $k_{31}$  and the combination between the directions of the spontaneous polarization axes and the poling field, which generates the strain to move the domains in the plates. Therefore, it was considered that the crystal phase of the PMNT(1-x)/x single-crystal plates after poling changed from pseudo-cubic to pseudo-cubic (x=0.251-0.262) from pseudo-cubic to orthorhombic (x=0.273-0.293), and from pseudo-cubic to rhombohedral (x=0.296-0.301), because of the combination to move the domains in the plates. These results were supported by the fact that the shapes of the P-E loops are triple or asymmetrical. Furthermore, it was considered that the E for such types of loops to appear was a coercive field to generate the DC-field-induced phase transition with giant  $k_{31}$ .

In conclusion of this part, the relationships between giant  $k_{31}$  (>80%) and  $k_{33}$  (>90%) in (100) PZNT91/09 and (110) PMNT(1-x)/x single-crystal plates were clarified to investigate the P-E hysteresis loops and the strain measurement. Triple and asymmetrical loops appeared in PMNT(1-x)/x single-crystal plates with giant  $k_{31}$  as well as in PZNT91/09 single-crystal plates with giant  $k_{31}$ . The typical relaxor-type hysteresis was observed for the electric-field-induced strain and their break points correspond to the coercive field to generate giant  $k_{31}$ . The crystal

phases after DC poling could be estimated using the relationships between the crystal plane, which closely affects the direction of the spontaneous polarization, and poling direction.

Fig. 27. Schematic diagrams of relationships between crystal plane, which affects direction of spontaneous polarization, and poling direction for realizing giant  $k_{31}$  (>80%) in (110) PMNT(1-x)/x (pseudo-cubic phase before poling) and PZNT91/09 (rhombohedral phase before poling) single-crystal plates at poling temperature of 40 °C.

# 5. Applications

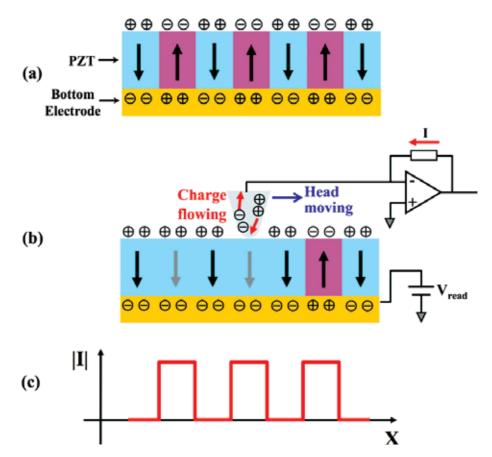

Utilizing the giant  $k_{31}$  and  $d_{31}$  in PZNT91/09 single crystals, devices such as piezoelectric unimorphs and bimorphs were fabricated in comparison with the devices consisting of PZT ceramics.

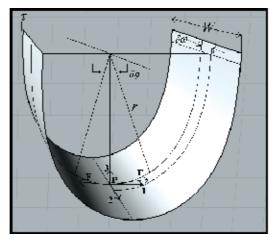

# 5.1 Applications of $Pb[(Zn_{1/3}Nb_{2/3})_{0.91}Ti_{0.09}]O_3$ single-crystal plates with giant $k_{31}$ to piezoelectric unimorphs and bimorphs

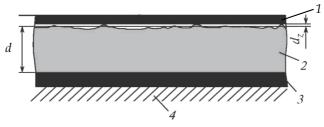

In this part, the piezoelectric and displacement properties on various kinds of unimorphs and bimorphs were reported. Piezoelectric unimorphs were prepared by sticking the PZNT91/09 single-crystal plates with giant  $k_{31}$  on center shim plates ( $15^{L}x4^{W}x0.10^{T}/0.20^{T}$  mm) composed of 42 nickel alloy. These were compared with unimorphs fabricated by ordinary PZT ceramic plates ( $k_{31}$ =37%,  $d_{31}$ =-330 pC/N) with the same dimensions. Furthermore, series-type bimorphs were made from the unimorphs by sticking other PZNT91/09 single-crystal plates and also PZT ceramic plates. The coupling factors on the bending mode ( $k_b$ ) of the unimorphs and bimorphs were evaluated. The displacement of the devices was measured by laser displacement equipment at room temperature.

# 5.1.1 Realization of giant $k_{31}$ over 80% in single-crystal plates

Table 4 shows the poling and annealing processes to obtain the giant  $k_{31}$  over 80%. When we poled three plate samples ( $13^{L}x4^{W}x0.36^{T}$  mm) of Nos. 1~3, only the one sample of No. 3-1 had a giant  $k_{31}$  of 85.6%. The others were 42.2% (No. 1-1) and 40.4% (No. 2-1). Therefore, the

| Sample No. | E (kV/mm) | k <sub>31</sub> (%) | k <sub>t</sub> (%) |  |

|------------|-----------|---------------------|--------------------|--|

| 1-1        | 1.0       | 42.2                | 55.1               |  |

|            | Annealing | 0.0                 | 0.0                |  |

| 1-2        | 1.0       | 49.6                | 59.0               |  |

| 1-3        | 1.5       | 39.6                | 55.8               |  |

| 1-4        | 2.0       | 79.5                | 56.2               |  |

| 1-5        | 2.5       | 55.7                | 59.6               |  |

| 1-6        | 3.0       | 39.8                | 55.7               |  |

| 2-1        | 1.0       | 40.4                | 54.9               |  |

|            | Annealing | 0.0                 | 0.0                |  |

| 2-2        | 1.0       | 45.4                | 54.2               |  |

| 2-3        | 1.5       | 86.2                | 56.2               |  |

| 3-1        | 1.0       | 85.6                | 56.8               |  |

Table 4. Process combination of poling and annealing to obtain Giant k<sub>31</sub>.

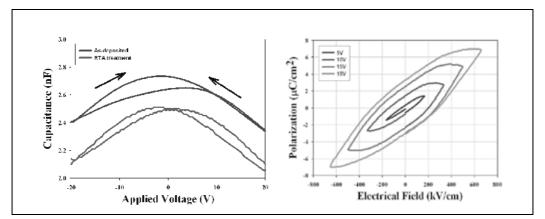

annealing at 200 °C for 30 min was carried out to de-polarize the samples. On the following processes, the poling fields increased from 1.0 kV/mm to 3.0 kV/mm. As a result, the giant  $k_{31}$  was realized in the cases of No. 1-4 and No. 2-3 while the electromechanical coupling factors of the thickness mode ( $k_t$ ) were almost the same of 54~60%. This means that the domain reorientation in thickness had been saturated; on the other hand, the one in the plate is changeable by the poling field. Furthermore, there was an optimum DC poling field for appearing the giant  $k_{31}$  on each individual plate sample. As mentioned above, the giant  $k_{31}$  can be obtained by the process combination of the DC poling and the annealing. Figure 28

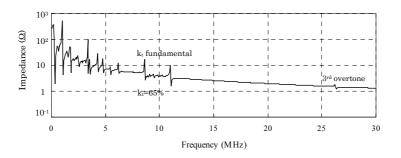

Fig. 28. Frequency responses of impedance on  $k_{31}$  mode in (a) PZNT91/09 single-crystal plate and (b) PZT ceramic plate.

shows the comparison between frequency responses of impedance in (a) the PZNT91/09 single-crystal plate and (b) the conventional PZT ceramic plate. The  $k_{31}$ 's were 86.2% (PZNT91/09: sample No. 2-3 in Table 4) and 37.3% (PZT), respectively.

### 5.1.2 Bending mode prpperties

The PZNT91/09 single-crystal plate ( $13^{L}x4.0^{W}x0.36^{T}$  mm) with giant  $k_{31}$  of 86.2% (No. 2-3 in Table 4) was stuck on a center shim plate ( $15^{L}x4^{W}x0.20^{T}$  mm) composed of 42 nickel alloy to prepare a piezoelectric unimorph. The same dimensions of the PZT ceramic plate ( $k_{31}$ =37%,  $d_{31}$ =-330 pC/N) was also used to realized a unimorph. Figure 29 shows the comparison between frequency responses of impedance in (a) the PZNT91/09 single-crystal unimorph and (b) the conventional PZT ceramic unimorph. The  $k_b$ =64.7% on bending mode in the PZNT91/09 single-crystal plate was three times larger than the  $k_b$ =20.6% in the PZT ceramic plate. Therefore, it was confirmed that the giant  $k_{31}$  and  $d_{31}$  constant could be useful to realize the piezoelectric unimorphs with high efficiency as well as the plate ( $13^{L}x4.0^{W}x0.36^{T}$  mm) resonators with giant  $k_{31}$  and  $d_{31}$  constant.

Fig. 29. Frequency responses of impedance on  $k_b$  mode in (a) PZNT91/09 single-crystal unimorph and (b) PZT ceramic unimorph.

A piezoelectric bimorph was fabricated by sticking the PZNT91/09 single-crystal plate with giant  $k_{31}$  of 85.6% (No. 3-1 in Table 4) on the PNZT91/09 single-crystal unimorph with the  $k_b$  of 64.7% as previously mentioned. A PZT ceramic bimorph was also prepared. Figure 30 shows the comparison between frequency responses of impedance in (a) the PZNT91/09

single-crystal bimorph and (b) the conventional PZT ceramic bimorph. The  $k_b$ =69.8% on bending mode in the PZNT91/09 single-crystal plate was twice larger than  $k_b$ =31.2% in the PZT ceramic plate. Therefore, it was confirmed that highly efficiency piezoelectric devices could be realized to utilize PZNT91/09 single-crystal plates with giant  $k_{31}$  and  $d_{31}$  constant in the cases of the piezoelectric bimorphs as well as the piezoelectric unimorphs.

Fig. 30. Frequency responses of impedance on  $k_b$  mode in (a) PZNT91/09 single-crystal bimorph and (b) PZT ceramic bimorph.

### 5.1.3 Displacement properties

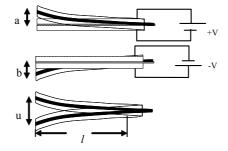

The displacement was evaluated regarding the PZNT91/09 single-crystal unimorphs (the center shim plate thickness of 0.20 mm)/ bimorphs (the center shim plate thickness of 0.10 mm) and the PZT ceramic unimorphs (the center shim plate thicknesses of 0.10 mm and 0.20 mm)/ bimorphs (the center shim plate thickness of 0.10 mm). In the case of a series-type bimorph in Fig. 31, the total displacement (u = a+b) was estimated by the following equation;

$$u = \left(\frac{3}{2}d_{31}\left(\frac{l}{t}\right)^2 \cdot \left(1 + \frac{t_s}{t}\right)V\alpha\right) \times 2 \tag{1}$$

where *l*: effective length (9 mm), *t*: thickness of devices (0.36+0.2 mm for single-crystal and ceramic unimorphs, 0.36+0.1 mm for ceramic unimorph, and 0.36x2+0.1 mm for single-

crystal and ceramic bimorphs),  $t_s$ : thickness of shim plate (0.1 mm and 0.2 mm), V: applied voltage and  $\alpha$ : non-linearity coefficient, respectively.

Fig. 31. Series type bimorphs and total displacement.

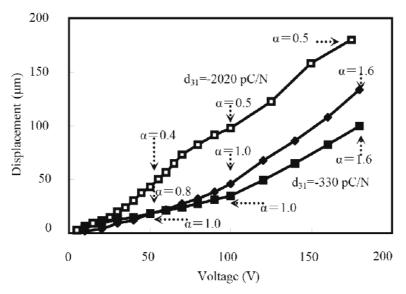

The relationships between the applied voltage and the displacement were shown in Fig. 32 for the different shim thickness in the PZNT single-crystal unimorph and the PZT ceramic unimorph. The d<sub>31</sub> constants of the stuck piezoelectric plates calculated from the frequency responses of the impedance were -2020 pC/N in the PZNT91/09 single crystal and -330 pC/N in the PZT ceramics, respectively. The displacement of the PZNT91/09 single-crystal unimorph was twice larger than the one of the PZT ceramic unmorph. The decrease in thickness of the shim plate from 0.20 mm to 0.10 mm increased the displacement in the range of over 100 V. The  $\alpha$  calculated from (1) was 0.4~0.5 in the PZNT91/09 single-crystal unimorph. Otherwise, the  $\alpha$  was 1.0 ( $\leq 100$  V) and 1.6 at 180 V in the PZT ceramic unimorph. Furthermore, the  $\alpha$  was independent of the shim plate thickness in the PZT ceramic unimorphs.

Fig. 32. Applied voltage dependence of displacement in PZNT91/09 single-crystal unimorph ( $\square$ : shim thickness of 0.20 mm) and PZT ceramic unimorph ( $\blacksquare$ : shim thicknesses of 0.20 mm and  $\blacklozenge$ : 0.10 mm).

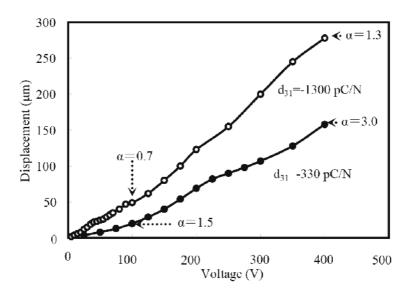

Figure 33 shows the applied voltage dependence of the displacement in the PZNT91/09 single-crystal bimorph and the PZT ceramic bimorph. The average  $d_{31}$  constants of the two stuck PZNT91/09 single-crystal plates and the two stuck PZT ceramic plates also showed in this figure. Although the  $d_{31}$  constant of the PZNT91/09 single crystals is 4~7 times larger than the  $d_{31}$  of the PZT ceramics, the displacement of the PZNT91/09 single-crystal bimorph became almost twice larger than the one of the PZT ceramic bimorph. The reason the displacement becomes twice, not more, was due to that the  $\alpha$  in the PZNT91/09 single-crystal bimorph was a half of the  $\alpha$  in the PZT ceramic bimorph.

Fig. 33. Applied voltage dependence of displacement in PZNT91/09 single-crystal bimorph ( $\circ$ : shim thickness of 0.10 mm) and PZT ceramic bimorph ( $\bullet$ : shim thickness of 0.10 mm).

The origin of the decrease in  $\alpha$  of the PZNT91/09 single-crystal bimorph was thought the mechanical softness of PZNT91/09 single-crystal plates with giant k<sub>31</sub> and d<sub>31</sub> constant. Namely, the Young's modulus of PZNT single crystals (0.89x10<sup>10</sup> N/m) is one order smaller than the one of PZT ceramics (6~8x10<sup>10</sup> N/mm). In addition to the above mentioned, the values of  $\alpha$  in bimorphs were approximately twice larger than the ones of unimorphs. This phenomenon was thought that the  $\alpha$  depends on the number of the piezoelectric plate; one plate in unimorph and two plates in bimorph, respectively.

In conclusion of this part, the process combination of poling and annealing to obtain giant  $k_{31}$  and  $d_{31}$  constant was clarified to fabricate PZNT91/09 single-crystal unimorphs and bimorphs. The coupling factors on bending mode ( $k_b$ ) in PZNT91/09 single crystal unimorphs and bimorphs were 2~3 times larger than the  $k_b$ 's in PZT ceramic unimorphs and bimorphs. The displacement of PZNT91/09 single-crystal unimorphs and bimorphs was almost twice larger than the one of PZT ceramic devices. The advantage of PZNT91/09 single-crystal plates with giant  $k_{31}$  and  $d_{31}$  constant was confirmed through the development of piezoelectric devices such as unimorphs and bimorphs.

## 6. Conclusion

We found the giant electromechanical coupling factor of  $k_{31}$  mode to be over 80% and the piezoelectric  $d_{31}$  constant to be nearly -2000 pC/N in ferroelectric relaxor single-crystal plates. The discovery of the giant  $k_{31}$  and the  $d_{31}$  constant became breakthroughs in applications to high-performance sensors and actuators utilizing  $k_{31}$  mode.

# 7. Acknowledgments

This work was partially supported by the Grant-in-Aid for Scientific Research C (Nos. 12650327, 17560294) from the Ministry of Education, Culture, Sports, Science and Technology, and the Foundation from the Regional Science Promotion (RSP) program 2004 of the Japan Science and Technology Agency, and the Research Foundation Grant 2003, 2006, 2007, 2008 jointly sponsored by Academia and Industry of Fukuroi City. The author would like to thank the Research Laboratory of JFE Mineral Co., Ltd. for supplying the PZNT and PMNT single-crystal plates.

## 8. References

- Koto, R. et al. (2006). Chemical Composition Dependence of Giant Piezoelectricity on k<sub>31</sub> Mode in Pb(Mg<sub>1/3</sub>Nb<sub>2/3</sub>)O<sub>3</sub>-PbTiO<sub>3</sub> Single Crystals, *Jpn. J. Appl. Phys.*, Vol.45, pp. 7418-7421.

- Koto, R. & Ogawa, T. (2007). Frequency Response Analysis by Finite Element Method in Relaxor Single-Crystal Plates with Giant k<sub>31</sub>, Jpn. J. Appl. Phys., Vol.46, pp. 7058-7062.

- Kuwata, J. et al. (1982). Dielectric and Piezoelectric Properties of 0.91Pb(Zn<sub>1/2</sub>Nb<sub>2/3</sub>)O<sub>3</sub>-0.09PbTiO<sub>3</sub> Single Crystals, *Jpn. J. Appl. Phys.*, Vol.21, p. 1298-1302.

- Matsushita, M. et al. (2001). Abstr. Am. Ceram. Soc., 103rd Annual Meet., p. 247.

- Ogawa, T. & Nakamura, K. (1999). Effect of Domain Switching and Rotation on Dielectric and Piezoelectric Properties in Lead Zirconate Titanate Ceramics, *Jpn. J. Appl. Phys.*, Vol.38, pp. 5465-5469.

- Ogawa, T. et al. (2002). Giant Electromechanical Coupling Factor of k<sub>31</sub> Mode and Piezoelectric d<sub>31</sub> Constant in Pb[(Zn<sub>1/3</sub>Nb<sub>2/3</sub>)<sub>0.91</sub>Ti<sub>0.09</sub>]O<sub>3</sub> Piezoelectric Single Crystal, *Jpn. J. Appl. Phys.*, Vol.41, pp. L55-L57.

- Ogawa, T. & Numamoto, Y. (2002). Origin of Giant Electromechanical Coupling Factor of k<sub>31</sub> Mode and Piezoelectric d<sub>31</sub> Constant in Pb[(Zn<sub>1/3</sub>Nb<sub>2/3</sub>)<sub>0.91</sub>Ti<sub>0.09</sub>]O<sub>3</sub> Single Crystal, *Jpn. J. Appl. Phys.*, Vol.41, pp. 7108-7112.

- Ogawa, T. et al. (2005). Giant Piezoelectricity on k<sub>31</sub> Mode in Pb(Mg<sub>1/3</sub>Nb<sub>2/3</sub>)O<sub>3</sub>-PbTiO<sub>3</sub> Single Crystal, *Jpn. J. Appl. Phys.*, Vol.44, pp. 7028-7031.

- Ogawa, T. (2005). Piezoelectric Bimorph with Giant Electromechanical Coupling Factor of Bending Mode Nearly 70% Fabricated by Low Symmetry Mono-Domain Pb[(Zn<sub>1/3</sub>Nb<sub>2/3</sub>)<sub>0.91</sub>Ti<sub>0.09</sub>]O<sub>3</sub> Single Crystal, Ferroelectrics, Vol.320, pp. 115-123.

Ogawa, T. (2008). Giant Transverse-Mode Electromechanical Coupling Factor and Piezoelectric Strain in Relaxor Single-Crystal Plates Evaluated Using P-E Hysteresis Loop, *Jpn. J. Appl. Phys.*, Vol.47, pp. 7655-7658.

Yin, J. et al. (1999). IEEE Proc. Med. Imag., Vol.3664, p. 239.

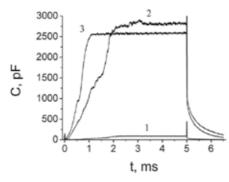

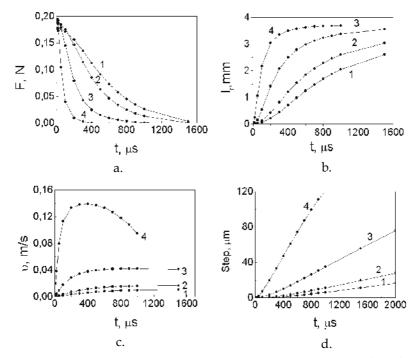

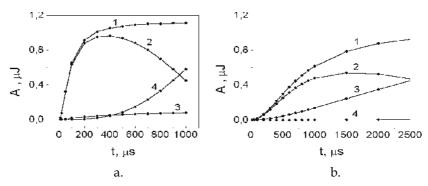

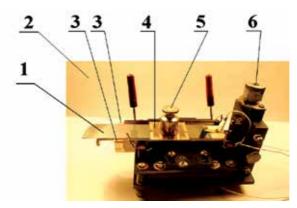

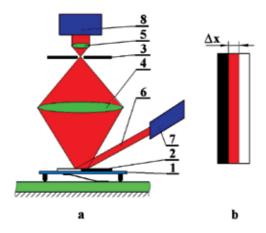

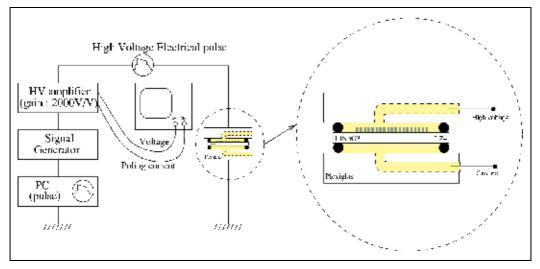

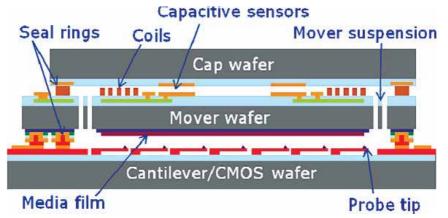

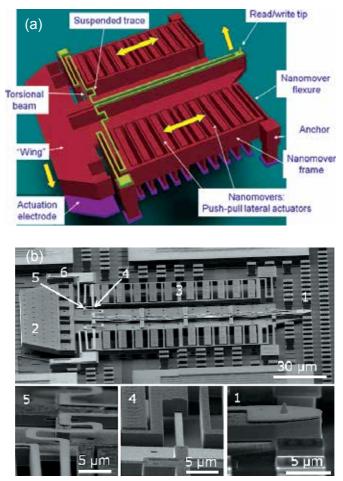

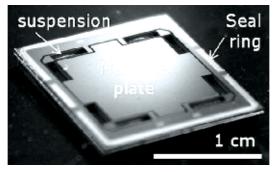

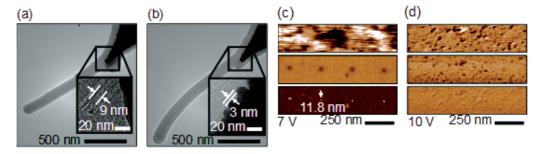

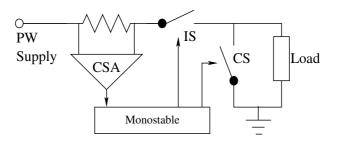

# **MEMS Based on Thin Ferroelectric Layers**

Igor L. Baginsky and Edward G. Kostsov

Institute of Automation and Electrometry, Russian Academy of Sciences, Russia

# 1. Introduction

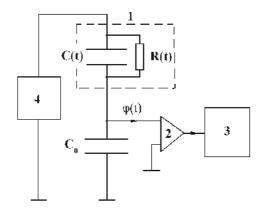

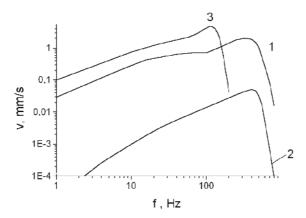

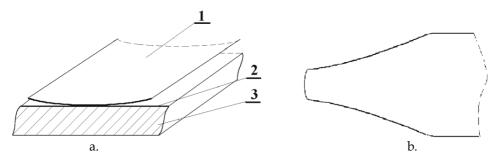

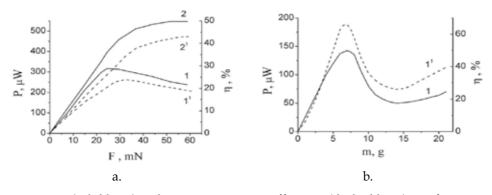

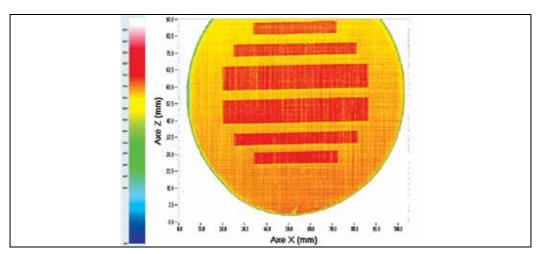

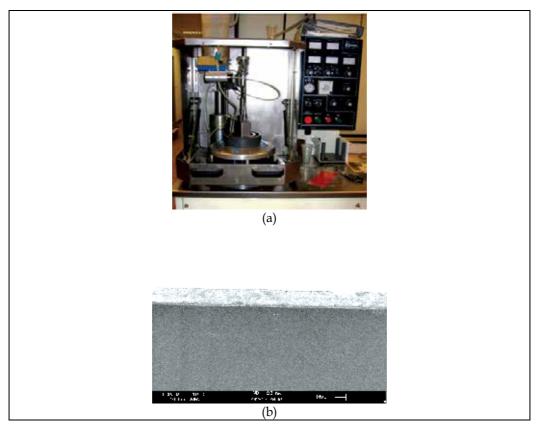

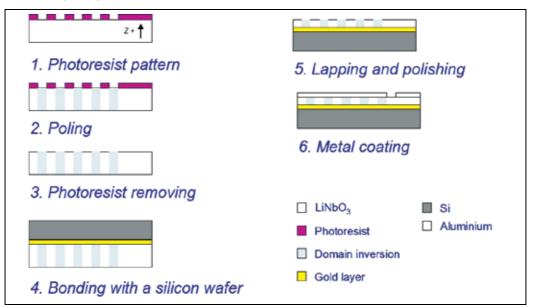

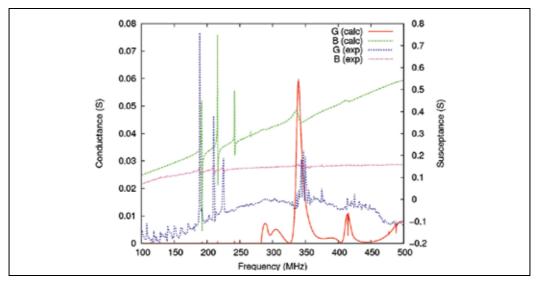

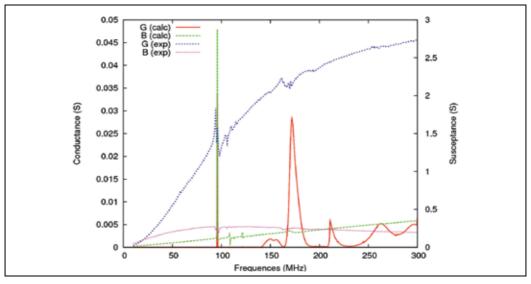

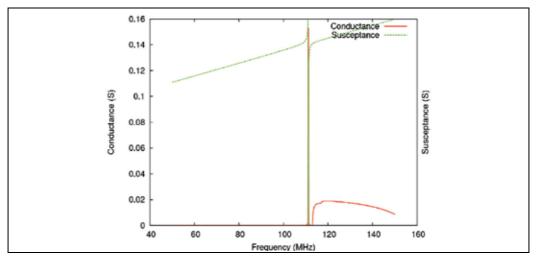

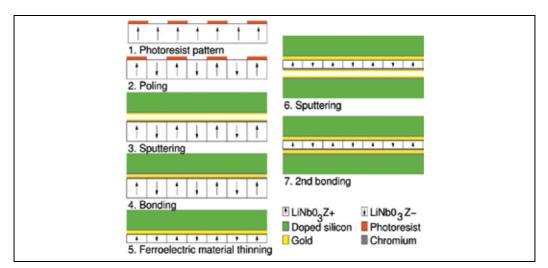

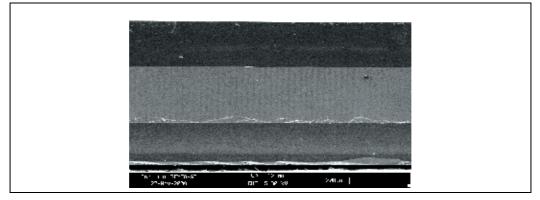

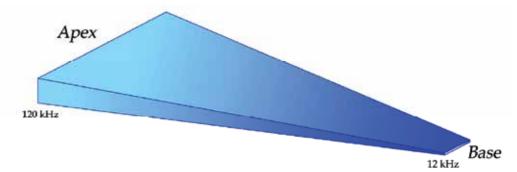

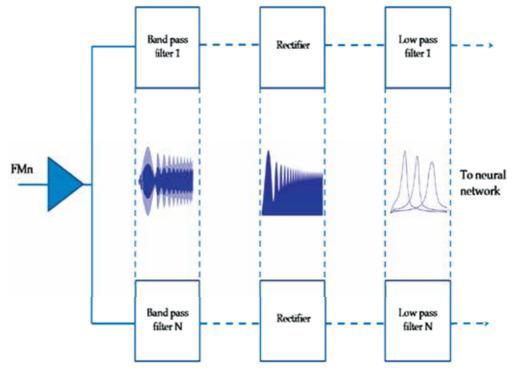

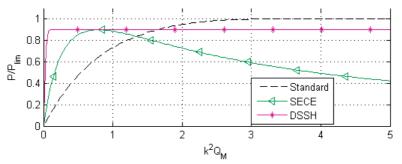

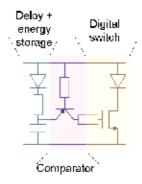

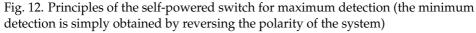

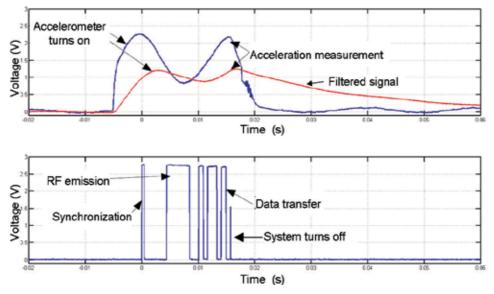

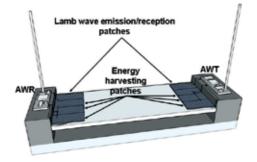

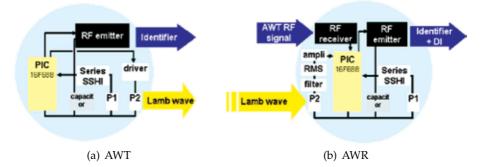

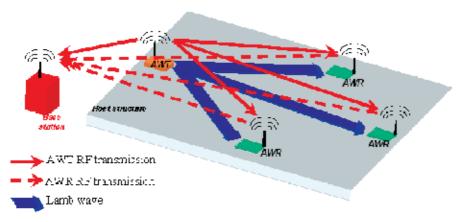

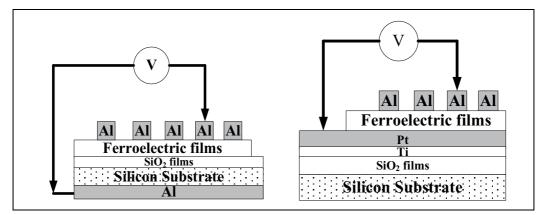

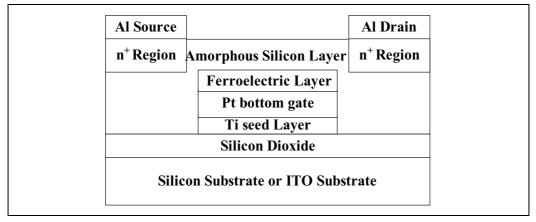

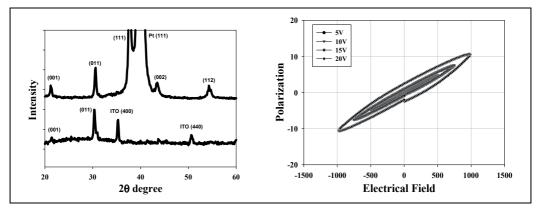

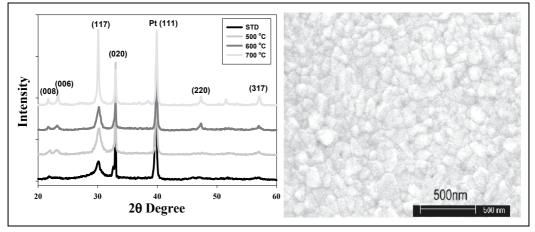

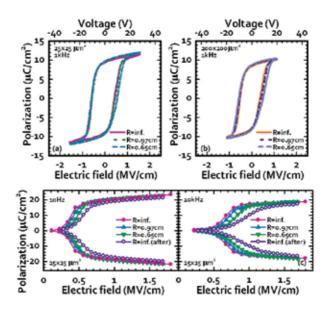

Micro-Electro-Mechanical Systems (MEMS) are devices that display the most intense development in modern microelectronics (Kostsov, 2009).