IntechOpen

# Computer Memory and Data Storage

Edited by Azam Seyedi

# Computer Memory and Data Storage

Edited by Azam Seyedi

Computer Memory and Data Storage http://dx.doi.org/10.5772/intechopen.104072 Edited by Azam Seyedi

#### Contributors

Ramtin Zand, Mohammed Elbtity, Peyton Chandarana, Ronald F. DeMara, Allam Abumwais, Mahmoud Obaid, Siddhartha Raman Sundara Raman, Azam Seyedi, Per Gunnar Kjeldsberg, Roger Birkeland

#### © The Editor(s) and the Author(s) 2024

The rights of the editor(s) and the author(s) have been asserted in accordance with the Copyright, Designs and Patents Act 1988. All rights to the book as a whole are reserved by INTECHOPEN LIMITED. The book as a whole (compilation) cannot be reproduced, distributed or used for commercial or non-commercial purposes without INTECHOPEN LIMITED's written permission. Enquiries concerning the use of the book should be directed to INTECHOPEN LIMITED rights and permissions department (permissions@intechopen.com).

Violations are liable to prosecution under the governing Copyright Law.

Individual chapters of this publication are distributed under the terms of the Creative Commons Attribution 3.0 Unported License which permits commercial use, distribution and reproduction of the individual chapters, provided the original author(s) and source publication are appropriately acknowledged. If so indicated, certain images may not be included under the Creative Commons license. In such cases users will need to obtain permission from the license holder to reproduce the material. More details and guidelines concerning content reuse and adaptation can be found at http://www.intechopen.com/copyright-policy.html.

#### Notice

Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published chapters. The publisher assumes no responsibility for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained in the book.

First published in London, United Kingdom, 2024 by IntechOpen IntechOpen is the global imprint of INTECHOPEN LIMITED, registered in England and Wales, registration number: 11086078, 5 Princes Gate Court, London, SW7 2QJ, United Kingdom

British Library Cataloguing-in-Publication Data A catalogue record for this book is available from the British Library

Additional hard and PDF copies can be obtained from orders@intechopen.com

Computer Memory and Data Storage Edited by Azam Seyedi p. cm. Print ISBN 978-1-80355-588-1 Online ISBN 978-1-80355-589-8 eBook (PDF) ISBN 978-1-80355-590-4

# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,700+

182,000+

195M+

Open access books available

International authors and editors

Downloads

156

Countries delivered to

Top 1%

most cited scientists

Our authors are among the

12.2%

Contributors from top 500 universities

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us?

Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

## Meet the editor

Azam Seyedi holds a master's degree in Electronics Engineering from the University of Tehran, Iran, and a Ph.D. in Computer Architecture from the Universitat Politecnica de Catalunya, Spain. Her research focuses on low-power circuit and system designs, reliability, memory design, and computer architecture. As a dedicated VLSI and computer architecture researcher, she has made significant contributions to the field through

numerous publications, including conference papers, book chapters, abstracts, and journal articles. Notably, she was awarded the ERCIM Alain Bensoussan Fellowship in 2017, the Marie Sklodowska-Curie Individual Fellowship in 2018, and the Best Paper Award at the Great Lakes Symposium on VLSI in 2011. Dr. Seyedi is an active member of the Institute of Electrical and Electronics Engineers (IEEE) and High Performance, Edge, And Cloud Computing (HiPEAC).

## Contents

| Preface                                                                                                                                                                             | ΧI |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Chapter 1</b> Introductory Chapter: Computer Memory and Data Storage by Azam Seyedi                                                                                              | 1  |

| <b>Chapter 2</b> System-Scenario Methodology to Design a Highly Reliable Radiation-Hardened Memory for Space Applications by Azam Seyedi, Per Gunnar Kjeldsberg and Roger Birkeland | 7  |

| <b>Chapter 3</b> A Review on Non-Volatile and Volatile Emerging Memory Technologies by Siddhartha Raman Sundara Raman                                                               | 23 |

| <b>Chapter 4</b><br>MRAM-Based FPGAs: A Survey<br>by Peyton Chandarana, Mohammed Elbtity, Ronald F. DeMara and Ramtin Zand                                                          | 39 |

| Chapter 5 New Content Addressable Memory Architecture for Multi-Core Applications by Allam Abumwais and Mahmoud Ohaid                                                               | 55 |

### Preface

In this book, *Computer Memory and Data Storage*, you will learn about the significant role that memory subsystems play in high-performance processors, the challenges associated with low-power memory designs, and the importance of ensuring data integrity and security in memory design. You will also discover various techniques proposed by researchers to address power consumption concerns and reliability issues. The book is organized into five chapters.

Introductory Chapter: Computer Memory and Data Storage introduces the topic of computer memory and data storage. The author highlights the significant role that memory subsystems play in high-performance processors and the impact they have on the overall energy, area, and performance of modern computing systems. The chapter also discusses the challenges associated with low-power memory designs and the need for techniques that effectively handle reliability issues. The author notes that various solutions have been explored to address power consumption concerns, such as scaling CMOS logic circuits. However, aggressive voltage scaling increases the likelihood of memory failures, making it crucial to implement techniques that effectively handle reliability issues associated with low-power designs.

The chapter also discusses the importance of minimizing power consumption while maintaining high performance and reliability, particularly in mobile devices where battery life is a critical factor. The author notes that Dynamic Voltage and Frequency Scaling (DVFS) is one approach to reducing power consumption, but it can also lead to reliability issues. To address these issues, researchers have proposed various techniques, such as Adaptive Voltage Scaling (AVS) and Dynamic Reliability Management (DRM). The chapter also highlights the importance of ensuring data integrity and security in memory design. Memory errors can lead to data corruption and system crashes, which can have serious consequences in critical applications. To address this issue, researchers have proposed various techniques, such as Error-Correcting Codes (ECC) and memory scrubbing.

Chapter System-Scenario Methodology to Design a Highly Reliable Radiation-Hardened Memory for Space Applications provides valuable information on designing a highly reliable radiation-hardened memory for space applications. The chapter focuses on the Nwise radiation-hardened cell, and the system-scenario methodology used to optimize energy consumption while maintaining reliability in cache memory circuits. The Nwise radiation-hardened cell is a memory cell that provides tolerance against single-event and multi-event upsets in memories.

The system-scenario methodology is used to optimize energy consumption in applications with dynamic system requirements. This methodology involves analyzing the system requirements and identifying the most critical scenarios that require the highest level of reliability. The energy consumption of the system is then optimized by adjusting the system parameters to meet the requirements of these critical scenarios. The study

presented in this chapter focuses on the use case related to satellite systems and solar activity. The methodology was applied to optimize the energy consumption of a cache memory circuit used in a satellite system that is exposed to solar activity. The study showed that the system-scenario methodology can significantly reduce the energy consumption of the cache memory circuit while maintaining the required level of reliability.

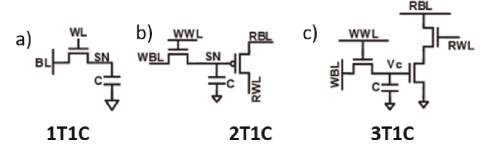

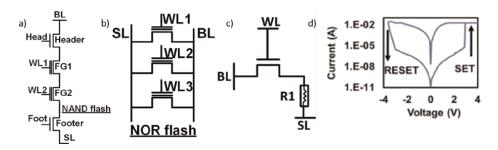

Chapter A Review on Non-Volatile and Volatile Emerging Memory Technologies discusses the need to address the reasons behind today's performance bottleneck in modern-day processors. The reasons include long access latency of memory technologies, scalability of memory designs, energy inefficiency incurred by increased performance, and additional area overhead. The chapter reviews different memory designs starting from volatile memory technologies such as Static Random Access Memory (SRAM), Dynamic Random Access Memory (DRAM), and NAND/NOR flash to emerging non-volatile memory technologies such as Resistive Random Access Memory (RRAM), Magneto-Resistive Random Access Memory (MRAM), and Ferroelectric Field Effect Transistor (FeFET) with specific consideration of tradeoffs involving area, performance, and energy.

The chapter begins with an introduction to the Von-Neumann architecture, which is the foundational architecture for high-performance CPUs. The chapter then elaborates on the existing technologies and the solutions proposed in the literature to understand the tradeoffs made between energy, area, and performance. The technologies described are SRAM, DRAM, NAND/NOR flash, RRAM, MRAM, and FeFET.

It classifies memory technologies into volatile and non-volatile memory technologies depending on whether the data is retained in memory in the absence of power supply. From an architectural perspective, processors use caches made of SRAM that are responsible for fast memory accesses and main memory made of DRAM optimized for density/cost. The secondary storage is made of non-volatile memory technologies like NAND Flash and optimized for higher density/lower cost.

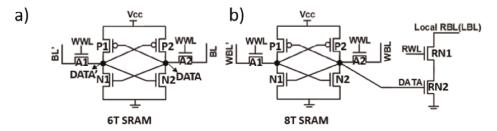

It elaborates on the tradeoffs in both 6T and 8T SRAM designs with respect to performance, area, and energy. The 8T SRAM design is proposed to relax the design constraints for read operation and to amortize the cost of a precharge cycle by performing another useful task simultaneously. The chapter also discusses the tradeoffs in DRAM, NAND/NOR flash, RRAM, MRAM, and FeFET designs.

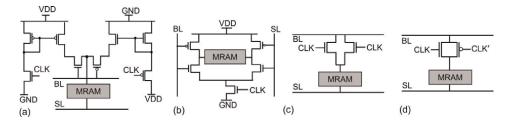

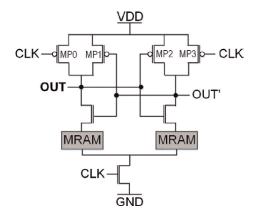

Field Programmable Gate Arrays (FPGAs) have become increasingly important in modern computing systems due to their flexibility and reconfigurability. However, conventional CMOS-based FPGAs have limitations such as high-power consumption and volatility. This is where MRAM technology comes in, providing non-volatility and low standby power. MRAM-based FPGAs have the potential to overcome the limitations of conventional FPGAs and provide a new generation of reconfigurable fabrics.

Chapter *MRAM-Based FPGAs*: A *Survey* provides a comprehensive overview of the recent developments in the field of MRAM-based FPGAs. It begins by introducing the concept of FPGAs and their importance in modern computing systems. It then discusses the limitations of conventional CMOS-based FPGAs, including their high-power consumption and volatility. The chapter then introduces MRAM technology and its potential to overcome these limitations by providing non-volatility and low standby power.

The chapter provides a comprehensive review of the prior research in the field of MRAM-based FPGAs. The chapter includes a table summarizing the design objectives, architecture, fabrication, speed, area, power, reliability, and security of various MRAM-based FPGA designs over the past two decades. The chapter also discusses the advantages and disadvantages of various MRAM technologies, including Spin-Transfer Torque MRAM (STT-MRAM) and Magnetic Tunnel Junction (MTJ) MRAM. It highlights the potential of MRAM technology to provide non-volatility and low standby power, which are essential for low-power applications such as Internet of Things (IoT) devices. MRAM-based FPGAs can also provide high-speed reconfiguration, which is important for applications such as software-defined radio and cognitive radio.

It also discusses the potential of MRAM-based FPGAs to provide high-security applications due to their non-volatile nature. The chapter then discusses the challenges associated with developing MRAM-based FPGAs. These challenges include the need for new design methodologies, the need for new fabrication processes, and the need for new testing and verification techniques. The chapter also discusses the potential future directions for research in this area, including the development of new MRAM technologies, the integration of MRAM with other emerging memory technologies, and the exploration of new design methodologies.

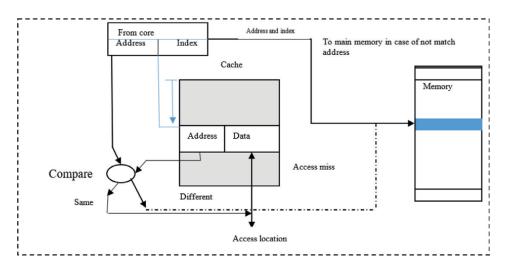

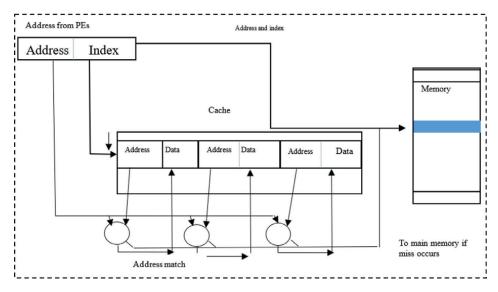

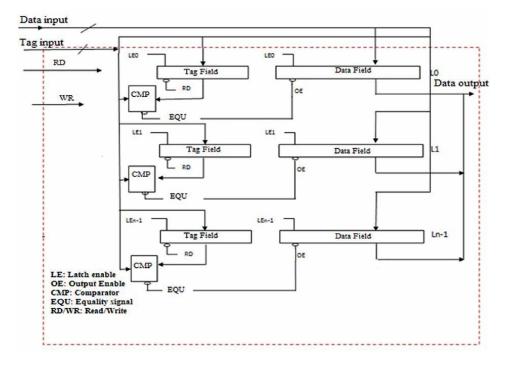

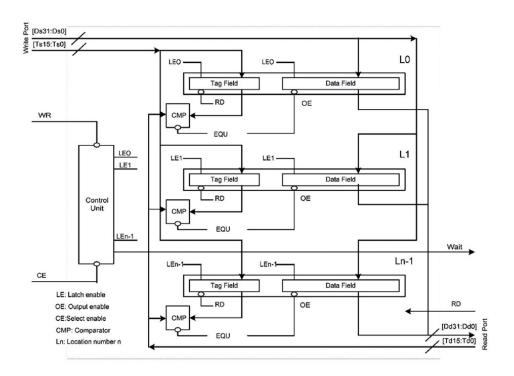

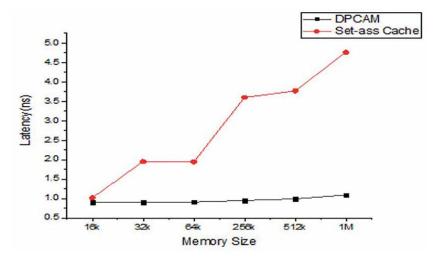

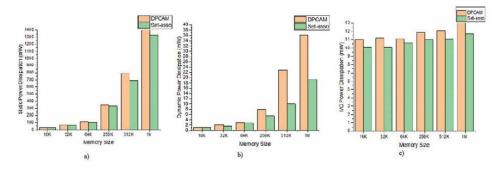

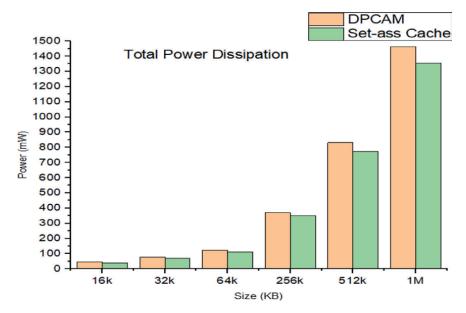

Chapter New Content Addressable Memory Architecture for Multi-Core Applications discusses a new content-addressable memory architecture for multi-core applications. The architecture is designed to address issues that arise when multiple cores try to access the same shared module in the shared cache memory. The near-far access replacement algorithm and the dual-port content addressable memory design are two solutions that are proposed to address these issues. The near-far access replacement algorithm is a new algorithm that is designed to improve the performance of shared cache memory in multi-core processors. The dual-port content-addressable memory design is another solution that is proposed to address issues with shared cache memory in multi-core processors. The chapter also discusses the performance of the new content-addressable memory architecture compared to a set-associative cache memory.

Finally, it discusses potential applications for the new content-addressable memory architecture in the field of massively parallel computation. The architecture is well-suited for applications that require high-speed access to shared memory, such as machine learning and data analytics. The architecture can also be used in other applications that require high-speed access to shared memory, such as video processing and scientific simulations.

Azam Seyedi

Faculty of Information Technology and Electrical Engineering,

Department of Electronic Systems,

Norwegian University of Science and Technology (NTNU),

Trondheim, Norway

#### Chapter 1

# Introductory Chapter: Computer Memory and Data Storage

Azam Seyedi

#### 1. Introduction

Memory subsystems play a significant role in high-performance processors, occupying a considerable portion of the die area. Consequently, they have a profound impact on the overall energy, area, and performance of modern computing systems [1]. This necessitates the development of low-power, reliable, and high-performance memory solutions to cater to the needs of emerging applications.

Various solutions have been explored to address power consumption concerns. For instance, scaling complementary metal-oxide-semiconductor (CMOS) logic circuits offers improvements in power consumption, area utilization, and speed. However, aggressive voltage scaling increases the likelihood of memory failures. Thus, further reducing the supply voltage poses a risk to the accuracy of computations. Consequently, it is crucial to implement techniques that effectively handle reliability issues associated with low-power designs in such systems [2, 3].

Motivated by these challenges, this book focuses on memory designs and explores the techniques to minimize power consumption while enhancing performance and reliability. Readers will gain insights into recent advancements in computer memory and data storage through investigation and analysis. By engaging with this resource, they will stay updated on the latest developments in computer memory and data storage.

# 2. Balancing performance and energy efficiency in cache memory design: Voltage scaling and power management strategies

Cache design plays a critical role in optimizing memory access efficiency in modern processors [1]. One commonly used type of cache is SRAM (Static Random-Access Memory), which offers fast access times and is commonly employed in cache hierarchies. However, in the pursuit of low-power memory design, innovative techniques are being explored to reduce power consumption in SRAM-based caches. These techniques include voltage scaling, where the supply voltage to the SRAM cells is reduced, as well as adaptive power gating, which selectively shuts down portions of the cache when not in use [4]. By incorporating such low-power design methodologies, cache systems can achieve a balance between performance and energy efficiency, contributing to overall system power savings while maintaining satisfactory memory access speeds [5].

Voltage scaling is a popular approach employed to reduce power consumption in memory subsystems. Operating at lower voltages significantly decreases power

1 IntechOpen

dissipation, leading to improved energy efficiency. However, voltage scaling brings challenges such as increased vulnerability to soft errors caused by radiation-induced particle strikes [2, 3]. To counter this, radiation hardening techniques are employed to enhance the resilience of SRAM cells against such errors. These techniques, such as redundant circuitry, error correction codes, and error detection and correction mechanisms, are employed to ensure reliable operation even in radiation-prone environments [6–10].

#### Reliable radiation-hardened memories: Design methodologies and techniques

Radiation hardening is a critical aspect of ensuring the reliability and robustness of electronic systems, particularly in demanding environments such as space applications. In space, electronic systems are exposed to high-energy particles that can cause significant damage and errors [3]. These particles can come from the sun, cosmic rays, and other sources, and they can cause single-event upsets (SEUs) or multiple-event upsets (MEUs) in electronic systems.

If a radiation strike impacts a node of an SRAM cell and modifies its stored data, it results in a phenomenon called Single Event Upset (SEU) [2]. This occurrence takes place when the charge delivered by the particle strike at the affected node exceeds the critical charge, known as Qcrit. Qcrit represents the minimum charge required to alter the data state stored within the SRAM cell [11]. If two or more neighboring nodes collectively receive and contribute to the deposited charge causing a state change, it is referred to as a Multi Event Upset (MEU) [11]. To address these challenges, radiation hardening techniques are employed in SRAM design.

Redundancy is a common approach wherein additional circuitry is incorporated to detect and correct errors. Error correction codes (ECC) are widely used to identify and correct bit errors, ensuring data integrity [7].

Moreover, techniques like triple modular redundancy (TMR) are employed to enhance system reliability [6]. TMR involves triplicating the circuitry and comparing the outputs to identify and correct errors. This redundancy adds an extra level of fault tolerance, ensuring reliable operation in the presence of radiation-induced errors.

Various techniques have been developed to mitigate Single Event Upset (SEU) issues in radiation-hardened memory cell designs [3]. Although conventional solutions such as ECC, DMR [8], and TMR have been used at the architectural level, they suffer from significant area overhead, power consumption, and increased system complexity, making them unsuitable for small memory blocks, particularly at low voltage levels [12]. In contrast, circuit-level techniques offer a more efficient approach by improving SEU immunity without architectural overhead, resulting in reduced area overhead, delay, and power consumption [3, 13–16].

However, previous designs exhibit various trade-offs in terms of SEU tolerance, critical charge, access time, area overhead, and recovery time. For example, some designs offer SEU tolerance but have a low critical charge (Qcrit) [15, 17] or high read access time [18]. Others address SEU tolerance but come with high area overhead [19], while some have limitations in SEU recovery and MEU immunity [14, 15]. Researchers continue to explore new techniques to develop memory cells that can offer improved radiation robustness while minimizing these trade-offs, especially for space applications and other scenarios requiring high reliability and efficiency.

## 4. Emerging non-volatile memory technologies: Overcoming limitations of existing technologies

Moore's law, which has significantly enhanced computing technology through technology scaling, has also brought about unintended consequences such as the heightened impact of radiation on SRAM cells. This is due to the increased susceptibility of transistors to noise at lower supply voltages and smaller feature sizes [2]. As a result, researchers are exploring alternative approaches to sustain continued scaling endeavors, leading to the emergence of non-volatile memory technologies.

These technologies, such as Flash memory, RRAM, and PCM, offer the advantage of data retention even when power is removed and are used in storage systems, solid-state drives, and embedded systems where persistent data storage is essential [20]. While non-volatile memories like Flash memory have been widely used in various applications, emerging non-volatile memory technologies such as MRAM, FeRAM, and STT-RAM are gaining attention due to their unique properties, such as non-volatility, high endurance, fast access times, high density, low power consumption, and fast write speeds [20, 21].

These emerging technologies have the potential to overcome some of the limitations of existing technologies. However, they also face challenges such as high production costs and scalability issues, which researchers are actively working to address and improve the performance and reliability of these technologies. Thus, the emergence of non-volatile memory technologies represents a promising alternative approach to sustain continued scaling endeavors and overcome the limitations of existing technologies [22].

#### 5. Conclusion

In summary, the design of memory systems encompasses several key aspects, such as voltage scaling to reduce power consumption, radiation hardening to enhance resilience against soft errors, variation-aware design to address process variations, low-power cache design for improved energy efficiency, fault-tolerant memory design to ensure reliable operation, and the adoption of emerging technologies that have the potential to overcome limitations of existing technologies. By incorporating these techniques, memory systems can achieve high performance, low power consumption, resilience to radiation-induced errors, and robustness against various fault conditions, effectively meeting the demands of modern computing applications.

#### **Author details**

Azam Seyedi

Faculty of Information Technology and Electrical Engineering, Department of Electronic Systems, Norwegian University of Science and Technology (NTNU), Trondheim, Norway

\*Address all correspondence to: azamseyedi2013@gmail.com

#### IntechOpen

© 2023 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. CO BY

#### References

- [1] Hennessy JL, Patterson DA. Computer Architecture: A Quantitative Approach. 6th ed. Cambridge, MA, United States: Morgan Kaufmann; 2020

- [2] Lin D, Xu Y, Liu X, Zhu W, Dai L, Zhang M, et al. A novel highly reliable and low-power radiation hardened SRAM bit-cell design. IEICE Electronics Express. 2018;15(3):20171129

- [3] Seyedi A, Aunet S, Kjeldsberg PG. Nwise and Pwise: 10T radiation hardened SRAM cells for space applications with high reliability requirements. IEEE Access. 2022;**10**: 30624-30642

- [4] Kaxiras S, Martonosi M. Computer Architecture Techniques for Power-Efficiency. San Rafael, CA, USA: Morgan and Claypool; 2008

- [5] Seyedi A, Armejach A, Cristal A, Unsal OS, Valero M. Novel SRAM bias control circuits for a low power L1 data cache. In: Proceeding of NORCHIP. Copenhagen, Denmark; 2012. pp. 1-6

- [6] Sterpone L, Violante M. Analysis of the robustness of the TMR architecture in SRAM-based FPGAs. IEEE Transactions on Nuclear Science. 2005; 52(5):1545-1549

- [7] Bajura MA, Boulghassoul Y, Naseer R, DasGupta S, Witulski AF, Sondeen J, Stansberry SD, Draper J, Massengill LW, Damoulakis JN. Models and algorithmic limits for an ECC-based approach to hardening sub-100-nm SRAMs. IEEE Transactions on Nuclear Science. 2007; 54(4):935-945

- [8] Teifel J. Self-voting dual-modularredundancy circuits for single eventtransient mitigation. IEEE Transactions on Nuclear Science. 2008;55(6):3435-3439

- [9] Seyedi A, Yalcin G, Unsal O, Cristal A. Circuit design of a novel adaptable and reliable L1 data cache. In: Proceedings of the 23rd ACM International Conference on Great Lakes Symposium on VLSI (GLSVLSI). Paris, France. 2013. pp. 333-334

- [10] Yalcin G, Seyedi A, Unsal O, Cristal A. Flexicache: Highly reliable and low power cache under supply voltage scaling. High Performance Computing. 2014;1:173-190

- [11] Lin S, Kim Y, Lombardi F. Analysis and design of nanoscale CMOS storage elements for single-event hardening with multiple-node upset. IEEE Transaction on Device Materials Reliability. 2012;12(1):68-77

- [12] Giterman R, Atias L, Teman A. Area and energy-efficient complementary dual-modular redundancy dynamic memory for space applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 2017;25(2): 502-509

- [13] Seyedi A, Aunet S, Kjeldsberg PG. Nwise: An area efficient and highly reliable radiation hardened memory cell designed for space applications. In: Proceeding of IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC). Helsinki, Finland; 2019. pp. 1-6

- [14] Jahinuzzaman SM, Rennie DJ, Sachdev M. A soft error tolerant 10T SRAM bit-cell with differential read capability. IEEE Transaction on Nuclear Science. 2009;56(6):3768-3773

- [15] Guo J, Zhu L, Sun Y, Cao H, Huang H, Wang T, et al. Design of areaefficient and highly reliable RHBD 10T

memory cell for aerospace applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 2018;**26**(5): 991-994

- [16] Jung I-S, Kim Y-B, Lombardi F. A novel sort error hardened 10T SRAM cells for low voltage operation. In: Proceeding of IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS). Boise, ID, USA. 2012. pp. 714-717

- [17] Jiang J, Xu Y, Zhu W, Xiao J, Zou S. Quadruple cross-coupled latch-based 10T and 12T SRAM bit-cell designs for highly reliable terrestrial applications. IEEE Transactions on Circuits and Systems I: Regular Papers. 2019;66(3): 967-977

- [18] Calin T, Nicolaidis M, Velazco R. Upset hardened memory design for submicron CMOS technology. IEEE Transactions on Nuclear Science. 1996; 43(6):2874-2878

- [19] Pal S, Mohapatra S, Ki W-H, Islam A. Soft-error-immune read stability-improved SRAM for multi-node upset tolerance in space applications. IEEE Transactions on Circuits and Systems I: Regular Papers. 2021;68(8): 3317-3327

- [20] Chen A. A review of emerging non-volatile memory (NVM) technologies and applications. Solid-State Electronics. 2016;**125**:25-38

- [21] Meena JS, Sze SM, Chand U,

Tseng T-Y. Overview of emerging nonvolatile memory technologies.

Nanoscale Research Letters. Sep 25 2014;

9(1). Article number: 526 (2014)

- [22] Wong HS, Salahuddin S. Memory leads the way to better computing. Nature Nanotechnology. 2015;**10**: 191-194

#### Chapter 2

# System-Scenario Methodology to Design a Highly Reliable Radiation-Hardened Memory for Space Applications

Azam Seyedi, Per Gunnar Kjeldsberg and Roger Birkeland

#### **Abstract**

Cache memory circuits are one of the concerns of computing systems, especially in terms of power consumption, reliability, and high performance. Voltage-scaling techniques can be used to reduce the total power consumption of the caches. However, aggressive voltage scaling significantly increases the probability of memory failure, especially in environments with high radiation levels, such as space. It is, therefore, important to deploy techniques to deal with reliability issues along with voltage scaling. In this chapter, we present a system-scenario methodology for radiationhardened memory design to keep the reliability during voltage scaling. Although any SRAM array can benefit from the design, we frame our study on the recently proposed radiation-hardened cell, Nwise, which provides high level of tolerance against single event and multi event upsets in memories. To reduce the power consumption while upholding reliability, we leverage the system-scenario-based design methodology to optimize the energy consumption in applications, where system requirements vary dynamically at run time. We demonstrate the use of the methodology with a use case related to satellite systems and solar activity. Our simulations show that we achieve up to 49.3% power consumption saving compared to using a cache design with a fixed nominal power supply level.

**Keywords:** space applications, solar activity, radiation hardening, single event upset (SEU), voltage scaling, system scenario, SRAM design, reliability, Nwise cell

#### 1. Introduction

The memory subsystems are among the main contributors to the total energy consumption, area, and performance of today's computing systems; therefore, there is a critical need to provide low-power, reliable, and high-performance memories for emerging applications. One of the concerns of memory designs is cache memories. Caches are designed to keep frequently used data and instructions close to the processing unit to avoid power-hungry and slow access to main memory. Almost all modern CPU cores, from ultra-low power chips, such as the ARM Cortex-A53 [1] to

the highest-end Intel Core i3-1215UL processors [2], use caches. However, caches are known to consume a large portion (up to 30-70%) of the total processor power [3, 4]. On-chip cache size will also continue to grow due to device scaling coupled with increased performance requirements.

Voltage-scaling techniques are well-known techniques to reduce the total power consumption of the caches. Due to the quadratic relationship between dynamic energy consumption and supply voltage, this is worthwhile even if it incurs overhead in other parts of the system. However, aggressive voltage scaling significantly increases the probability of memory failure. Therefore, further reduction of the supply voltage is not possible without the risk of erroneous computations. This problem increases dramatically in environments with high levels of radiation, such as in space, because the systems stay exposed to high doses of radiation strikes for long periods of time and have limited energy budgets [5]. Therefore, adding advanced techniques to deal with the reliability issues during voltage scaling is critical for energy-efficient memory designs, especially for space applications.

A memory fault is typically modeled as a single event upset (SEU) or a multi event upset (MEU), where a single or multiple nodes in a memory cell may change state due to charge deposited by a radiated energetic particle [6]. Design of low-power and fault-tolerant caches has a rich body of work at different design abstraction levels. Circuit-level techniques are used to improve the reliability of each SRAM cell at low-voltage levels. Apart from the standard six transistor (6 T) SRAM cells, 8 and 10 T SRAM cells have been proposed by [7, 8]. These designs have a large area overhead, which again poses a significant limitation in performance and increase in power consumption of the caches. In addition, they do not provide enough tolerance against high radiation strikes in space.

A hardened 10 T SRAM cell called Quatro-10 T is proposed in [9] to provide higher area efficiency and higher reliability in low-voltage applications with larger noise margin and lower leakage current. It uses negative internal feedbacks to improve the immunity of the cell nodes against SEUs. However, it cannot provide full immunity to all SEUs, and some internal nodes may flip during  $0 \rightarrow 1$  SEU [10]. The RHBD-10 T cell is proposed with a low area overhead compared to previous radiation-hardened memory cells [10]. However, the proposed 10 T cell suffered from high read access time that may affect its application, wherever high speed is necessary [10, 11]. Furthermore, even if providing SEU tolerance regardless of the upset polarity, the tolerance capability, that is. the radiation-induced charge it can resist, is not high compared to previously proposed cells [11]. Two quadruple cross-coupled storage cells, the so-called QUCCE 10 T and QUCCE 12 T, are proposed in [12]. QUCCE 10 T is a proper cell design for high-speed applications, while the QUCCE 12 T cell is a promising candidate for low-voltage and high reliability. Their SEU tolerance is lower than several previous designs such as [11], though QUCCE 12 T tolerates higher deposited charge at the expense of larger area. Therefore, the proposed cells may be less suitable for space applications that need high cell robustness and low area.

Nwise and Pwise have recently been proposed as two highly reliable radiation-hardened SRAMs cells [11, 13]. Simulation results show that they are competitive cells for radiation-hardened SRAMs to use in various memory blocks for space applications compared to the state of art. Both have the highest level of SEU tolerance capability for the temperature range deployed in space applications. In addition, both have the highest level of the tolerance to MEU. However, all the simulations are done at nominal voltage levels, and voltage scaling has not been addressed in those papers.

Circuit designs proposed in [14, 15] combine data duplication/triplication with error correction schemes to increase reliability while reducing supply voltage. The design can save energy through voltage scaling and ensure reliable behavior in harsh environments, however, with the cost of high area overhead of additional memory cells.

At the architecture level, several schemes have been proposed to save the energy by reducing the voltage while improving the reliability using sophisticated fault tolerance mechanisms, such as block/set pairing [16], address remapping [17], and block/set-level replication [18]. In another set of schemes, various complex error correcting codes (ECC) have been used to protect against both permanent and transient errors while reducing the voltage [19–21].

Some software-level approaches have been proposed that use language extensions to give the programmer the ability to perform relaxations [22]. For instance, a framework is developed to expose hardware errors to software in specified code regions. This allows programmers to mark certain regions of the code relaxed and decrease the processor's voltage and frequency below the critical threshold when executing such regions.

For other parts of the embedded systems domain, the so-called system-scenario-based design methodology has been developed to optimize energy consumption. System-scenario-based techniques [23, 24] enable exploitation of application dynamism through fine-grained run-time system tuning. At design time, profiling is used to determine the behavior of different run-time situations. Run-time situations are then clustered into system scenarios based on similarity in a multidimensional cost perspective, such as execution time, energy consumption, and memory footprint [25]. Optimal platform configurations, such as dynamic voltage, frequency settings, memory configuration, and task mapping, are then determined for each scenario. Furthermore, efficient scenario prediction and switching mechanisms are developed. At run time, according to the current run-time situation and the scenario knowledge, the application and platform are switched to the optimal configuration.

However, little work has been attempted to leverage a combination of hardware-and software-level techniques to simultaneously manage unreliability and reduce power consumption, especially in the electronics space industry. To this end, our work adopts an approach where the circuit and run-time levels of the system cooperate to improve energy and reliability issues. Our main goal is to design a low-power and fault-tolerant cache memory accompanied with a system-scenario-based design methodology, which makes it possible to minimize power consumption by adapting voltage and frequency levels according to a dynamically changing exposure to different doses of particle strikes. The contributions of this chapter are as follows:

- 1. We present a radiation-hardened memory circuit design, which keeps the reliability during voltage scaling. This design allows us to operate at nominal voltage levels down to low-voltage levels for space applications.

- 2. We leverage the system-scenario-based design methodology to optimize the energy consumption at run time.

The rest of the chapter is organized as follows: In Section 2, we first briefly review the Nwise cell design details [11, 13]. Then, we move on to the adapted version of the Nwise cell, which can operate reliably during voltage scaling. We describe the schematic details, operational behavior, and address the SEU robustness analysis.

Furthermore, the circuit simulations results, including read and write delay times, read and write power consumption, and robustness simulations during voltage scaling, are presented in this section. In Section 3, we briefly describe the system-scenario-based design methodology and explain how we deploy this methodology in our design. Then, a case study is presented to confirm the applicability of our design in space. In this section, we show how the system-scenario methodology can optimize the power consumption when the system is operating in space. To confirm the usefulness of our proposed method, our memory energy consumption is compared in two cases: when it is equipped with the system-scenario method and when it operates without considering any scenario decision at run time. Finally, Section 4 concludes this chapter.

#### 2. Memory design details

#### 2.1 Cell schematics

The Nwise and Pwise cells have been recently proposed as area-efficient and highly reliable radiation-hardened SRAM cells [11, 13]. However, we will go with Nwise cell in this chapter since it is a proper choice for cache designs.

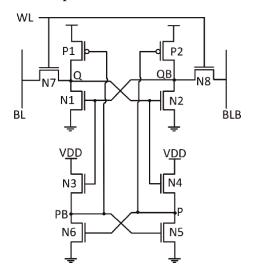

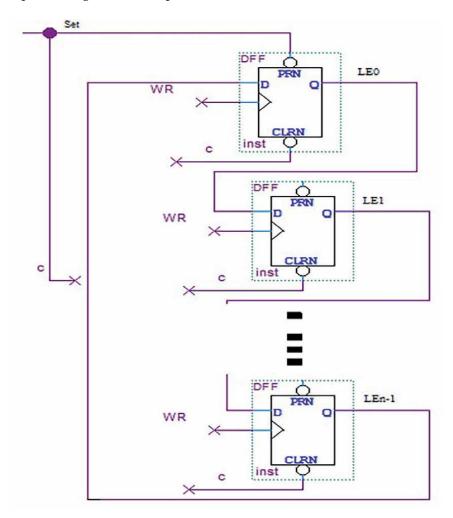

**Figure 1** shows the details of the Nwise cell circuit. The main storage part of the cell is a cross-coupled pair, consisting of transistors N1 and N2. The backup part is another cross-coupled pair consisting of transistors N5 and N6. The Nwise cell, thus, has four storage nodes Q, QB, P, and PB. Transistors N7 and N8 connect BL and BLB to Q and QB, respectively. N7 and N8 are controlled by the word line (WL): when WL is High, N7 and N8 are ON, and read/write operations are done. Two feedback paths (P1-N4 and P2-N3) help the storage nodes recover to their initial value after particle strikes and secure robustness under high radiation conditions.

Although Nwise improves fault tolerance, it can suffer from poor cell stability under voltage scaling [8]. This is a common problem also for the other radiation-hardened cells presented in the previous section. To overcome the stability problem, a

Figure 1.

Circuit details of the Nwise cell.

single-ended read port SRAM cell is proposed in [26], which can separate the read bit line from the storage node with the help of two added NMOS transistors. In this way, the stability of the SRAM cell is improved during read operation, which allows further scaling toward threshold levels [8]. Inspired by this technique, our Adapted Nwise cell is chosen for our simulation in this chapter.

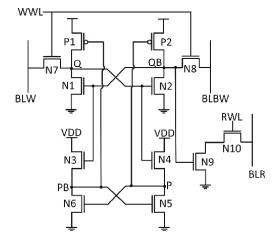

We show the structure of the Adapted Nwise cell in **Figure 2**. The main storage part is still the same as the Nwise cell. However, the access paths are separated: N7 and N8 are write access transistors that connect the main storage nodes to the write bit lines (BLW and BLBW). When the write word line (WWL) is high, N7 and N8 are ON, and a write operation is performed. N9 and N10 connect the storage node QB to the read bit line (BLR). During a read operation, read word line (RWL) is high and turns on N10.

#### 2.2 Operation analysis

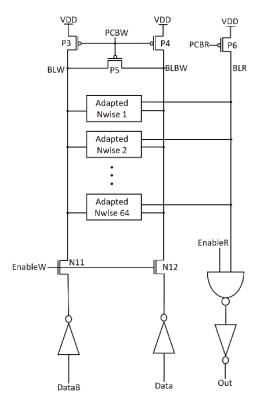

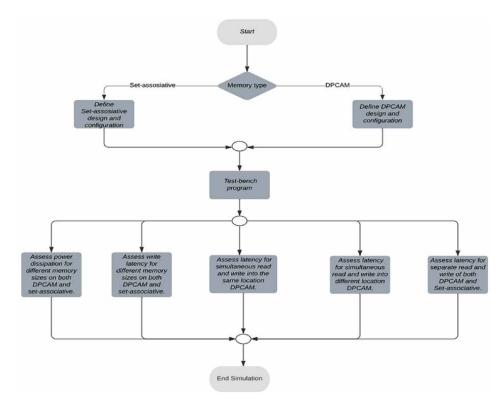

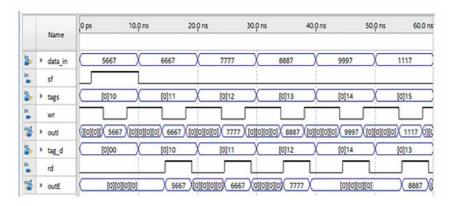

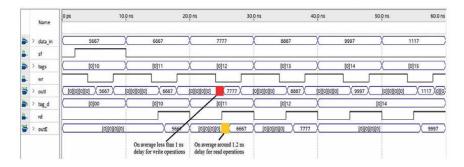

**Figure 3** shows the test bench circuit used in our simulations, which consists of a one-column set containing 64 Adapted Nwise cells and associated peripheral circuitry (read and write precharge circuits and appropriate circuits for read [7] and write operations [27, 28]).

Transistors P3, P4, and P5 keep BLW and BLBW precharged to VDD before the write operation begins. Signals EnableW is set to VDD, hence Data and DataB can be transferred to BLW and BLBW. Signal WWL is set to VDD, the write operation starts, and data can be written to the storage nodes. Before starting the read operation, transistor P6 keeps BLR precharged to VDD. The read operation begins when RWL becomes high, hence BLR is connected to the internal storage node through N9 and N10. When the read data is on BLR, EnableR becomes high, and the NAND gate routes the data to out.

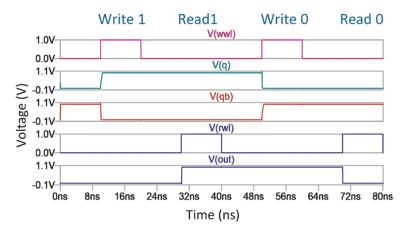

We use 45 nm technology to design the Adapted Nwise cell. The simulations are done with LTspice [29] at different voltage levels (1 to 0.5 V). **Figure 4** shows the transient simulation results of an Adapted Nwise cell located in the test bench column set for a sequence of "Write 1, Read 1, Write 0, and Read 0" operations. It confirms that the write and read operations are completed successfully.

Figure 2.

Circuit details of the adapted Nwise cell.

Figure 3.

The test bench circuit consists of a one-column set containing 64 adapted Nwise cells and appropriate circuits for read and write operations [7, 27, 28].

**Figure 4.**The simulation waveform of the adapted Nwise cell for a sequential set of operations, write 1, read 1, write 0, and read 0.

#### 2.3 SEU recovery analysis

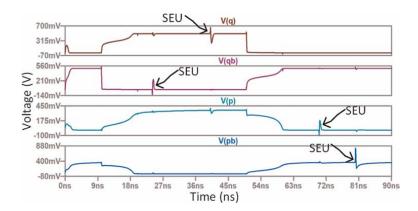

The SEU robustness of the proposed cell for VDD = 0.5 V is depicted in **Figure 5**. When an energetic particle passes through a semiconductor device, electron-hole

System-Scenario Methodology to Design a Highly Reliable Radiation-Hardened Memory... DOI: http://dx.doi.org/10.5772/intechopen.113327

Figure 5. SEU tolerance simulation of the adapted Nwise cell for VDD = 0.5 V.

pairs are created in its path because it loses its energy [30, 31]. If such an energetic particle strikes a reverse-biased junction depletion region, the injected charge is transported by drift current, leading to an accumulation of extra charge at the node [31]. It produces a transient current pulse that changes the value of the node when the injected charge exceeds the critical charge collected in the node ( $Q_{crit}$ ) [30, 31]. Hence, sensitive cell nodes are the nodes surrounded by the reverse-biased drain junction of transistor(s) biased in the OFF state [32]. Thus, when a radiation particle strikes a PMOS transistor, only a positive transient pulse ( $1 \rightarrow 1$  or  $0 \rightarrow 1$ ) is generated, whereas when a radiation particle strikes an NMOS transistor, only a negative transient pulse ( $0 \rightarrow 0$  or  $1 \rightarrow 0$ ) is induced [32]. Let us assume that the Adapted Nwise cell is in state 1 (Q = 1, QB = 0, PB = 0, and PB = 0. Therefore, transistors N2, N4, N6, and P1 are ON, and the rest are OFF. Hence, Q, QB, and P are sensitive nodes, while PB is not sensitive to the particle strike.

As shown in **Figure 5**, fault injections that may result in SEUs occur at 25, 40, 70, and 80 ns, respectively. At 25 ns, QB is affected by a particle strike (QB:  $0 \rightarrow 1$ ). We observe that QB returns to its initial state, and followed by it, other nodes return to their initial state. At 40 ns, node Q is affected by a particle strike (Q:  $1 \rightarrow 0$ ). Again, the internal nodes of the Adapted Nwise cell recover their initial state after the injected fault. At 70 ns, P is affected by a particle strike (P:  $0 \rightarrow 1$ ). As can be seen, node P comes back to its initial state, and followed by it, other internal nodes recover their initial state after the injected faults. Finally, PB is affected by a particle strike at 80 ns (PB:  $1 \rightarrow 0$ ). PB also returns to its initial state, and followed by it, other nodes return to their initial state. Hence, the cell is robust against SEUs on all nodes.

The core cell is the same as the Nwise cell. Since the SEU robustness simulations are done in the hold mode, the description of the SEU robustness of the Adapted Nwise cell is the same as that of the Nwise cell [11, 13]. Due to lack of space, we briefly mention the relevant explanations in this article and refer the readers to [11, 13]. In our simulations, we inject charges at cell nodes using the model outlined in Section 2.4. A charge just below the  $Q_{crit}$  of the given node is injected to show how this affects the node voltage, and how the SRAM cell recovers its original state. If a charge equal to or greater than  $Q_{crit}$  is injected, the SRAM cell would not be able to recover, and a actual SEU would occur.

#### 2.4 Design methodology and simulation results

As mentioned, we design and simulate a one-column set consisting of 64 Adapted Nwise cells and associated peripheral circuitry. The high-level structure is a column in a cache memory as described in [33, 34]. Necessary wire capacitances are added to the bitlines (BLW, BLBW, and BLR) and the wordlines (WWL and RWL) based on the sizes reported in [12, 31, 35].

Transistor sizes of the memory cells, as well as the peripheral circuitry, are optimized to get the maximum robustness, as well as minimum read/write power consumption, minimum read/write access times, and minimum area. However, when the optimization goals are conflicting, more weight is given to robustness. Transistor sizes are chosen for the worst case (VDD = 0.5 V):  $W_{P1} = W_{P2} = 60nm$ ,  $W_{N1} = W_{N2} = 240nm$ ,  $W_{N3} = W_{N4} = 240nm$ ,  $W_{N5} = W_{N6} = 60nm$ ,  $W_{N7} = W_{N8} = 180nm$ ,  $W_{N9} = W_{N10} = 180nm$ .

We use standard manual optimization, tuning transistor sizes to find a global optimized solution. The simulations are performed with LTspice at different voltage levels (1 to 0.5 V) and at a temperature of 27°C. The circuits are designed with a 45 nm predictive technology model. From the simulations, we find the read and write power consumption, read and write access times, and  $Q_{crit}$  for different voltage levels.

To simulate the effects of a particle strike injection in a cell node, we use the same model as used in [13]. It is a double exponential current model presented in Eq. (1) that has been widely used by researchers [12, 36, 37].  $Q_{dep}$  is the total charge deposited at the node hit by the particle strike.  $\tau_r$  is the collection time constant of the junction and  $\tau_f$  is the ion-track establishing time constant. Both are material-dependent time constants [36]. According to Yassin et al. [38], we set  $\tau_r = 164$ ps and  $\tau_f = 50$ ps. We gradually increase  $Q_{dep}$  in Eq. (1) in the simulations until the data value stored in the SRAM cell changes and cannot be recovered. This is the critical charge of a given node in an SRAM cell. The cell  $Q_{crit}$  is the minimum  $Q_{crit}$  among all sensitive nodes of the cell.

$$I(t) = \frac{Q_{dep}}{\tau_f - \tau_r} \left( e^{\frac{-t}{\tau_f}} - e^{\frac{-t}{\tau_r}} \right) \tag{1}$$

**Table 1** shows simulation results with the full performance comparison of the Adapted Nwise cell during voltage scaling. The comparisons include power consumption during read and write operations, read access times, write access times, and  $Q_{crit}$ .

| Supply Voltage<br>Level | Write Power<br>(uW) | Read Power<br>(uW) | Write Access<br>Time (ps) | Read Access Time<br>(ps) | Q <sub>crit</sub><br>(fF) |

|-------------------------|---------------------|--------------------|---------------------------|--------------------------|---------------------------|

| 1 V                     | 19.19               | 8.49               | 53.16                     | 29.51                    | 101.5                     |

| 0.9 V                   | 16.61               | 4.93               | 63.48                     | 35.31                    | 86.6                      |

| 0.8 V                   | 15.85               | 3.06               | 78.67                     | 43.39                    | 70.7                      |

| 0.7 V                   | 16.26               | 2.02               | 111.48                    | 59.49                    | 51.3                      |

| 0.6 V                   | 14.67               | 1.58               | 176.72                    | 95.74                    | 31.9                      |

| 0.5 V                   | 9.93                | 1.10               | 400.95                    | 196.48                   | 15.9                      |

Table 1.

Cost comparison for the adapted Nwise cell for different supply voltage levels.

#### 3. System-scenario-based design methodology

As we mentioned in Section 1, the system-scenario-based design methodology is a combined design-time and run-time methodology [39] to exploit the application's dynamic behavior at run time, leading to significant optimization potential. According to our simulations, the energy consumption is reduced by combining voltage scaling techniques applied to SRAM cells with the system-scenario-based design method in our framework. A two-phase design-time/run-time system scenario design methodology is detailed in [24]. Here, we describe the methodology according to our use case:

#### 3.1 Case study: space weather forecast

The main idea is to adapt the supply voltage according to the probability of SEUs. When the probability is high, we increase the supply voltage to make the memory more robust against radiation. On the other hand, we reduce the supply voltage to save power when the probability for SEUs is low.

In space, a satellite is exposed to different doses of radiation, depending on, for example, the solar activity. Various agencies provide forecasts for the space weather, that is. the electron or proton flux, based on solar activity. As a case study, we choose the available online information for historic solar weather from [40]. We extract proton flux numbers from November 2004 to May 2022 from the graph. The graph shows samples of the average solar flux units per month, and we choose this parameter as a knob to select the appropriate scenario. In this case, the granularity is relatively coarse, and the power supply voltage can only be adjusted once a month. This is historically coarse-grained statistics. An operational system would have to be based on space weather predictions that typically are valid for a 3 day period, with a forecasted granularity of down to three-hour windows, in which the VDD can be adjusted to the predicted case for each window. **Table 2** shows the number of samples in each range of solar flux.

A correlation between the solar flux level and the probability of SEU has been reported in [41]. We also assume that the energy of the particles reaching the chip surface is sufficiently moderated by passing through metallic shielding [42]. Under these realistic assumptions, we observe flux levels between 5 and 160 MeV. At design time, we identify run-time situations (RTSs) and cluster them into six scenarios:

| Range of flux level | Number of one-month samples in each range |

|---------------------|-------------------------------------------|

| 0–45 MeV            | 0                                         |

| 45 MeV – 60 MeV     | 0                                         |

| 60 MeV – 85 MeV     | 115                                       |

| 85 MeV – 110 MeV    | 47                                        |

| 110 MeV – 130 MeV   | 32                                        |

| 130 MeV – 160 MeV   | 17                                        |

**Table 2.**Number of samples at each range of solar flux [40].

- 1. The first scenario is defined for flux levels below 45 MeV. For this situation, we choose VDD = 0.5 V. The system is in low-power consumption mode, but at the cost of lowest fault tolerance.

- 2. The second scenario is defined for flux levels between 45 and 60 MeV (45 MeV < flux  $\le$  60MeV). For this situation, we choose VDD = 0.6 V.

- 3. The third scenario is defined for flux levels between 60 and 85 MeV (60 MeV < flux  $\leq$  85MeV). For this situation, we choose VDD = 0.7 V.

- 4. The fourth scenario is defined for flux levels between 85 and 110 MeV (85 MeV < flux  $\le$  110MeV). For this situation, we choose VDD = 0.8 V.

- 5. The fifth scenario is defined for flux levels between 110 and 130 MeV (110 MeV < flux  $\le$  130MeV). For this situation, we choose VDD = 0.9 V.

- 6. The sixth scenario is defined for flux levels between 130 and 160 MeV (130 MeV < flux ≤160MeV). For this situation, we choose VDD = 1 V. The system has the highest level of fault tolerance but at the cost of high power consumption.

At run time, the satellite is informed from Earth when the solar activity changes, and scenarios are dynamically selected accordingly. We now calculate the total power consumption in two cases: (a) when the system scenario method is applied and the system can run at different voltage levels, and (b) when the system runs only at a fixed nominal voltage level.

To calculate power consumption, we need the following information: **Table 1**, which shows cost comparison for the Adapted Nwise cell for different supply voltage levels. **Table 2**, which shows the number of samples in each solar flux range. Furthermore, the number of each level-one cache operation, which is available for a tested benchmark [43]. According to Petersen [43], the number of read and write operations for a tested application of the STAMP benchmark suite, Genome, are as follows: 400449 and 25,028.

We calculate the total power consumption of the first case as follows: (1) The total power consumption for each voltage level is calculated according to the information obtained from **Table 1**, and the number of each operation reported in [43]. (2) The number of samples for each scenario is multiplied by the number of corresponding total power calculated in 1. (3) The results of all scenarios are added together.

For example, we examine the sixth scenario: the number of samples in this range is 17. We choose VDD = 1 V for this scenario. The power consumption for each sample is calculated as follows:

$$Power_{sample} = [(400449 * 8.49uW) + (25028 * 19.19uW)]/(400449 + 25028)$$

(2)

Therefore, the total power consumption is obtained by multiplying this number by the number of samples in this range (17), which is equal to 155.03 uW. Similarly, we calculate the total power consumption for each scenario. Then, we add them all together, which results in 842.47 uW.

For the second case: (1) The total power consumption is calculated only for VDD = 1 V according to the information obtained from **Table 1** and the number of each operation reported in [43]. The power consumption for each sample is the same

| Cache Designs                                                                                               | Power<br>Consumption<br>(uW) |

|-------------------------------------------------------------------------------------------------------------|------------------------------|

| Original Nwise cache design with a fixed nominal power supply level                                         | 1662.93                      |

| Adapted Nwise cache design with a fixed nominal power supply level                                          | 1924.11                      |

| Adapted Nwise cache design with adapted power supply levels according to system scenario design methodology | 842.47                       |

Table 3.

The total power consumption of each cache design.

as Eq. (2). (2) The total number of samples (211) is multiplied by the number of power consumption calculated in 1), which is equal to 1924.11 uW.

In this way, we have demonstrated a 56.2% power saving compared to using Adapted Nwise with fixed nominal power supply level. We repeat our simulation for a cache consisting of the original Nwise cell depicted in **Figure 1**. The total power consumption of this cache is calculated as follows:

$$Power_{total} = 211 * (400449 * 7.49uW + 25028 * 14.14uW)/(400449 + 25028)$$

(3)

which is equal to 1662.93 uW, 13.6% lower than that of a cache containing of Adapted Nwise cells (at VDD = 1 V). Using the Adapted Nwise cell in combination with system scenario-controlled voltage scaling reduces the power consumption by 49.3% compared to using the original Nwise cell. **Table 3** summarizes the results.

It should be mentioned that we do not consider the loss induced by the circuitry generating the different voltage levels. We assume that this memory will be used in systems, where dynamic voltage and frequency scaling are anyway used for the regular logic.

#### 4. Conclusions and future work

In this chapter, we present a radiation-hardened memory design, which keeps the reliability during voltage scaling. Inspired by the Nwise cell, a recently proposed highly reliable radiation-hardened SRAM cell, we present the design of the Adapted Nwise cell, including calculations of its  $Q_{crit}$ , energy consumption, and access time for each operation during voltage scaling. Simulations show that this design can operate at nominal voltage levels down to low-voltage levels for space applications.

In addition, we leverage the scenario-based design methodology to optimize energy consumption at run time and according to our use case: solar activity. Our simulations show that we save up to 49.3% in power consumption compared to using a cache design with a fixed nominal power supply level.

As a future work, an operational system will be made practical by leveraging information from space weather forecasts, thus adjusting the VDD value based on the expected solar flux. Space weather forecasts are given as a three-day prediction and a methodology to extract relevant prediction parameters and distribute them in time to a space system using the Adapted Nwise cell memory must be developed. In addition, process, voltage, and temperature (PVT) variations will be investigated in our future work.

#### Acknowledgements

This work was funded by the European Union's Horizon 2020 research and innovation program under the Marie Sklodowska-Curie Grant Agreement No. 799481.

The authors thank Gunnar Maehlum and Dirk Meier from the company Integrated Detector Electronics AS (ideas) for their help and fruitful comments that greatly improved the design and experiments.

#### **Author details**

Azam Seyedi\*, Per Gunnar Kjeldsberg and Roger Birkeland Faculty of Information Technology and Electrical Engineering, Department of Electronic Systems, Norwegian University of Science and Technology (NTNU), Trondheim, Norway

\*Address all correspondence to: azamseyedi2013@gmail.com

#### IntechOpen

© 2023 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. CO BY

#### References

- [1] ARM Developer [Internet]. 2012. Available from: https://developer.arm. com/Processors/Cortex-A53.php [Accessed: October 21, 2022]

- [2] Intel Core i3-1215UL Processors [Internet]. Available from: https://www.intel.com/content/www/us/en/products/sku/230902/intel-core-i31215ul-processor-10m-cache-up-to-4-40-ghz/specifications. html [Accessed: October 21, 2022]

- [3] Wong W, Koh C, Chen Y, Li H. VOSCH: Voltage scaled cache hierarchies. In: Proceeding of 25th International Conference on Computer Design (ICCD). Lake Tahoe, California, USA: IEEE; 2007. pp. 496-503

- [4] Zhang C, Vahid F, Najjar W. A highly configurable cache for low energy embedded systems. ACM Transactions on Embedded Computing Systems. 2005;4:363-387

- [5] Lin D, Xu Y, Liu X, Zhu W, Dai L, Zhang M, et al. A novel highly reliable and low-power radiation hardened SRAM bit-cell design. IEICE Electronics Express. 2018;15(3):20171129

- [6] Lin S, Kim Y, Lombardi F. Analysis and design of nanoscale CMOS storage elements for single-event hardening with multiple-node upset. IEEE Transaction on Device Materials Reliability. 2012;12(1):68-77

- [7] Calhoun BH, Chandrakasan A. A 256kb sub-threshold SRAM in 65 nm CMOS. In: Proceeding of IEEE International Solid State Circuits Conference - Digest of Technical Papers. San Francisco, California, USA: IEEE; 2006. pp. 2592-2601

- [8] Verma N, Chandrakasan A. A 256 kb 65 nm 8T subthreshold SRAM employing sense-amplifier redundancy. IEEE

- Journal of Solid-State Circuits. 2008; **43**(1):141-149

- [9] Jahinuzzaman SM, Rennie DJ, Sachdev M. A soft error tolerant 10T SRAM bit-cell with differential read capability. IEEE Transaction on Nuclear Science. 2009;56(6):3768-3773

- [10] Guo J, Zhu L, Sun Y, Cao H, Huang H, Wang T, et al. Design of areaefficient and highly reliable RHBD 10T memory cell for aerospace applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 2018;**26**(5): 991-994

- [11] Seyedi A, Aunet S, Kjeldsberg PG. Nwise and Pwise: 10T radiation hardened SRAM cells for space applications with high reliability requirements. IEEE Access. 2022;**10**: 30624-30642

- [12] Jiang J, Xu Y, Zhu W, Xiao J, Zou S. Quadruple cross-coupled latch-based 10T and 12T SRAM bit-cell designs for highly reliable terrestrial applications. IEEE Transactions on Circuits and Systems I: Regular Papers. 2019;66(3):967-977

- [13] Seyedi A, Aunet S, Kjeldsberg PG. Nwise: An area efficient and highly reliable radiation hardened memory cell designed for space applications. In: Proceeding of IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC). Helsinki, Finland: IEEE; 2019. pp. 1-6

- [14] Seyedi A, Yalcin G, Unsal O, Cristal A. Circuit design of a novel adaptable and reliable L1 data cache. In: Proceedings of the 23rd ACM International Conference on Great Lakes Symposium on VLSI (GLSVLSI). Paris,

- France: Association for Computing Machinery; 2013. pp. 333-334

- [15] Yalcin G, Seyedi A, Unsal O, Cristal A. Flexicache: Highly reliable and low- power cache under supply voltage scaling. High Performance Computing. 2014;1:173-190

- [16] Wilkerson C, Gao H, Alameldeen AR, Chishti Z, Khellah M, Lu S-L. Trading off cache capacity for reliability to enable low voltage operation. In: Proceeding of International Symposium on Computer Architecture (ISCA). Beijing, China: IEEE; 2008. pp. 203-214

- [17] Ansari A, Feng S, Gupta S, Mahlke S. Archipelago: A polymorphic cache design for enabling robust near-threshold operation. In: Proceeding of EEE 17th International Symposium on High Performance Computer Architecture. San Antonio, Texas; USA: IEEE; 2011. pp. 539-550

- [18] Banaiyan MA, Homayoun H, Dutt N. FFT-cache: A flexible fault-tolerant cache architecture for ultra-low voltage operation. In: Proceeding of 14th International Conference on Compilers, Architectures and Synthesis for Embedded Systems (CASES). Taipei, Taiwan: IEEE; 2011. pp. 95-104

- [19] Alameldeen AR, Wagner I, Chishti Z, Wu W, Wilkerson C, Lu S-L. Energy-efficient cache design using variable-strength error-correcting codes. In: Proceeding of 38th Annual International Symposium on Computer Architecture (ISCA). San Jose, CA, USA: IEEE; 2011. pp. 461-471

- [20] Chishti Z, Alameldeen AR, Wilkerson C, Wu W, Lu S-L. Improving cache lifetime reliability at ultra-low voltages. In: Proceeding of 42nd Annual IEEE/ACM International Symposium on

- Microarchitecture (MICRO). New York, NY, USA: IEEE; 2009. pp. 89-99

- [21] Qureshi MK, Chishti Z. Operating SECDED-based caches at ultra-low voltage with FLAIR. In: Proceeding of 43rd Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN). Budapest, Hungary: IEEE; 2013. pp. 1-11

- [22] Carbin M, Misailovic S, Martin C. Verifying quantitative reliability of programs that execute on unreliable hardware. ACM SIGPLAN Notices. 2013; **48**(10):33-52

- [23] Filippopoulos I, Catthoor F, Kjeldsberg PG. Exploration of energy efficient memory organisations for dynamic multimedia applications using system scenarios. Design Automation for Embedded Systems. 2013;17:669-692

- [24] Gheorghita S, Palkovic M, Hamers J, Vandecappelle A, Mamagkakis S, Basten T, et al. System-scenario-based design of dynamic embedded systems. ACM Transactions on Design Automation of Electronic Systems. 2009;14(1):1-45

- [25] Oleynik Y, Gerndt M, Schuchart J, Kjeldsberg PG, Nagel WE. Run-time exploitation of application dynamism for energy-efficient exascale computing (READEX). In: Proceeding of 18th International Conference on Computational Science and Engineering. Porto, Portugal: IEEE Computer Society; 2015. pp. 347-350

- [26] Chang L, Fried DM, Hergenrother J, Sleight JW, Dennard RH, Montoye RK, et al. Stable SRAM cell design for the 32 nm node and beyond. In: Digest of Technical Papers Symposium on VLSI Technology. Kyoto, Japan: IEEE; 2005. pp. 128-129

- [27] Maroof N, Kong BS. Charge sharing write driver and half-vdd pre-charge 8t

- SRAM with virtual ground for low-power write and read operation. IET Circuits, Devices Systems. 2018;**12**(1):94-98

- [28] Jaeyoung K, Pinaki M. A robust 12T SRAM cell with improved write margin for ultra-low power applications in 40nm CMOS. Integration. 2017;57: 1-10

- [29] [Internet]. Available from: https://www.analog.com/en/design-center/design-tools-and-calculators/ltspice-simulator.html [Accessed: October 21, 2022]

- [30] Atias L, Teman A, Giterman R, Meinerzhagen P, Fish A. A low-voltage radiation-hardened 13T SRAM bitcell for ultra-low power space applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 2016;24(8): 2622-2633

- [31] Guo J, Xiao L, Mao Z. Novel low-power and highly reliable radiation hardened memory cell for 65 nm CMOS technology. IEEE Transactions on Circuits and Systems I: Regular Papers. 2014;**61**(7):1994-2001

- [32] Kelin LH, Klas L, Mounaim B, Prasanthi R, Linscott IR, Inan US, et al. LEAP: Layout design through erroraware transistor positioning for softerror resilient sequential cell design. In: Proceeding of IEEE International Reliability Physics Symposium. Anaheim, CA, USA: IEEE; 2010. pp. 203-212

- [33] Seyedi A, Armejach A, Cristal A, Unsal O, Hur I, Valero M. Circuit design of a dual-versioning L1 data cache for optimistic concurrency. In: Proceedings of the 21st Edition of the Great Lakes Symposium on Great Lakes Symposium on VLSI (GLSVLSI). Lausanne, Switzerland: Association for Computing Machinery; 2011. pp. 325-330

- [34] Armejach A, Seyedi A, Titos-Gil R, Hur I, Cristal A, Unsal OS, et al. Using a

- reconfigurable L1 data cache for efficient version management in hardware transactional memory. In: Proceeding of International Conference on Parallel Architectures and Compilation Techniques. Galveston, Texas, USA: IEEE; 2011. pp. 361-371

- [35] Guo J, Xiao L, Wang T, Liu S, Wang X, Mao Z. Soft error hardened memory design for nanoscale complementary metal oxide semiconductor technology. IEEE Transactions on Reliability. 2015;**64**(2): 596-602

- [36] Messenger GC. Collection of charge on junction nodes from ion tracks. IEEE Transactions on Nuclear Science. 1982; **29**(6):2024-2031

- [37] Lin S, Kim Y, Lombardi F. A 11-transistor nanoscale CMOS memory cell for hardening to soft errors. IEEE Transaction on VLSI Systems. 2011; **19**(5):900-904

- [38] Qi C, Xiao L, Wang T, Li J, Li L. A highly reliable memory cell design combined with layout-level approach to tolerant single-event upsets. IEEE Transactions on Device and Materials Reliability. 2016;16(3):388-395

- [39] Yassin Y, Catthoor F, Kjeldsberg PG, Perkis A. Techniques for dynamic hardware management of streaming media applications using a framework for system scenarios.

Microprocessors and Microsystems. 2018;56:157-168

- [40] Space Weather Prediction Center [Internet]. Available from: https://www.swpc.noaa.gov/communities/space-weather-enthusiasts-dashboard [Accessed: 2022-10-21]

- [41] The Space Environment Information System [Internet]. Available from: https://www.spenvis.oma.be/help/backg

round/flare/flare.html [Accessed: October 21, 2022]

[42] Petersen E. Single Event Effects in Aerospace. Wiley-IEEE Press; 2011 Online ISBN: 9781118084328. DOI: 10.1002/9781118084328

[43] Seyedi A, Armejach A, Cristal A, Unsal OS, Valero M. Novel SRAM bias control circuits for a low power L1 data cache. In: Proceeding of NORCHIP. Copenhagen, Denmark: IEEE; 2012. pp. 1-6

## Chapter 3

# A Review on Non-Volatile and Volatile Emerging Memory Technologies

Siddhartha Raman Sundara Raman

## **Abstract**

As technology scaling is approaching a stand-still with architectural advancements on modern day processors struggling to improve performance, coupled with the rise in machine learning topologies demanding better performing processors, there is a pressing need to address the reasons behind today's performance bottleneck. These reasons include long access latency of memory technologies, scalability of memory designs, energy inefficiency incurred by increased performance, and additional area overhead. To explore these issues, a holistic understanding of existing memory technologies is essential. In this chapter, a review of different memory designs starting from volatile memory technologies such as Static Random Access Memory (SRAM), Dynamic Random Access Memory (DRAM), NAND/NOR flash to emerging non-volatile memory technologies such as Resistive Random Access Memory (RRAM), Magneto-resistive random access memory (MRAM), Ferroelectric Field effect transistor (FeFET) is presented, with specific consideration of tradeoffs involving area, performance, energy.

**Keywords:** memory, SRAM, DRAM, non-volatile memory, NAND/NOR, RRAM, FeFET, MRAM

### 1. Introduction

Modern day systems typically consist of a central processing unit responsible for performing arithmetic and logical operations on the data stored in memory. This architecture is called the Von-Neumann architecture, wherein there are dedicated logic and arithmetic units inside the CPU and the data is read/written from/into memory, and has been the foundational architecture for high performance CPUs till date. A brief background of these CPUs suggest that these processors have undergone tremendous improvements beginning from in-order CPUs that execute the instructions in program order, to modern-day out-of-order CPUs that execute instructions as soon as they are ready to execute and still give an impression to the software that the instructions were executed in-order. This has resulted in an increased performance, with frequencies ranging as high as GHz. However, the major bottleneck from improving the performance further has been the tremendously low memory performance [1, 2], often referred to as the memory-wall bottleneck. To alleviate this, an indepth analysis of existing/emerging memory technologies is required to understand

23 IntechOpen

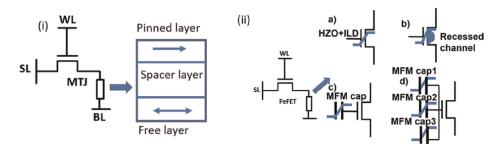

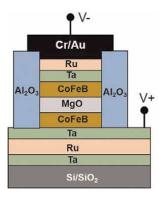

the problems in each of the technologies and further propose solutions. Therefore, in this chapter, we give a brief overview on the existing technologies and the solutions proposed in the literature to understand the tradeoffs made between energy, area and performance. The technologies described are (i) Static Random Access Memory (SRAM), (ii) Dynamic Random Access Memory (DRAM), (iii) NAND/NOR flash (iv) Resistive Random Access Memory (RRAM), (v) Magneto-resistive Random Access Memory (MRAM), (vi) Ferroelectric Field effect Transistor (FeFET). The major reason behind choosing these devices as the case study for non-volatile memories is that there has been a tremendous growth in the recent times about potential of replacing the existing memory topologies with these devices, as they offer bitcell density advantage.

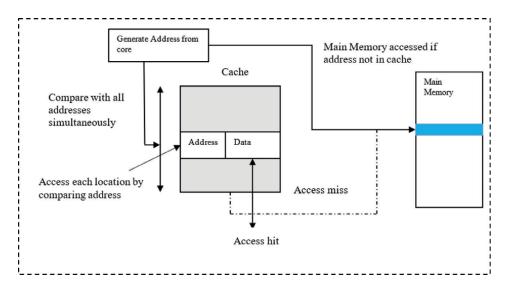

## 2. Memory technologies

The memory technologies can be classified into volatile and non-volatile memory technologies depending on whether the data is retained in memory in the absence of power supply. From an architectural perspective, processors use caches made of SRAM that are responsible for fast memory accesses and main-memory made of DRAM optimized for density/cost. The hard disk/secondary storage are made of non-volatile memory technologies like NAND Flash and are further optimized for higher density/lower cost.

## 2.1 Volatile memory technology

The major memory technologies that are present in the modern-day computers are made of SRAM, DRAM and embedded DRAM (eDRAM). SRAMs have been the workhorse of high performance caches, as they have low access latencies as compared to other memory technologies. Commodity DRAMs have been used in main memory storage, as they have the advantages of high density and a simple bitcell structure. Embedded DRAMs have started to gain traction for caches as they offer higher performance (than commodity DRAM) and high density with a simple bitcell structure, which will be discussed in detail in this section.

### 2.1.1 Static random access memory (SRAM)

SRAMs are classified into 6 T, 7 T, 8 T,9 T and 10 T structures [3]. The most commonly used SRAM bitcells are the 6 T and 8 T bitcells. Both these bitcells make use of a cross-coupled inverter as the storage element. The 6 T structure is used when overall SRAM area is constrained with high-performance requirements. However, the 8 T structure is used in high-performance cache designs, wherein there are no density constraints, because they have the advantage of performing read after write in back-to-back cycles [4]. This section elaborates the tradeoffs in both these designs with respect to performance, area and energy.

### 2.1.1.1 6 T SRAM

This design makes use of a shared read-write port, thereby ensuring that either read/write can be performed in a cycle, therefore making it a 1R(read)W(write) port design. 6 T SRAMs shown in **Figure 1** consists of a cross-coupled inverter with pull-up

**Figure 1.** *a)* 6 T SRAM, with a shared read/write port, b) 8 T SRAM with decoupled read and write ports.

PMOS transistors named P1, P2 and pull-down NMOS transistors named N1, N2 and the NMOS access transistors named A1, A2. In the case of a write operation, data is written onto the bitcell by conditioning the bit lines (BL) to the data value that needs to be stored in the bitcell [5]. For instance, for writing '1' onto the bitcell, BL is driven high with a voltage of Vcc and BL' is driven low with a voltage of 0. WWL voltage is driven high so that the DATA node holds a value of '1' and DATA' node holds a '0'. This operation can be split further into 2 phases, namely the initiation and completion phase. The initiation of writing '1' onto the DATA node begins by writing '0' onto the DATA' node, as the NMOS access transistor A1 can pass a good '0', as opposed to NMOS access transistor A2 passing a good '1'. Thus, DATA' going low would imply that the PMOS P2 is slowly being turned ON, thus helping A2 to further write a good '1' onto the bitcell, even though A2 does not pass a good '1' during the completion phase. In order to accomplish a good initiation, the access transistor marked A1 should have a high drive strength as compared to PMOS P1 so that BL' is written successfully onto the DATA' node. In the case of writing a '0' onto DATA node, A2 initiates the process and is completed by the PMOS P1 driving DATA node to Vcc [6]. In this case, the design constraint is that the drive strength of A2 must be greater than the drive strength of P2 to accomplish a successful completion. Generalizing this, the initiation is brought about by the node storing '1' and completed by the node storing '0' in the case of a write operation.

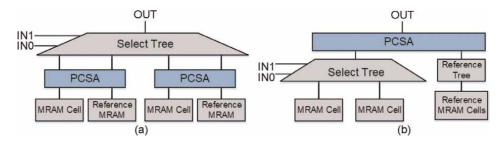

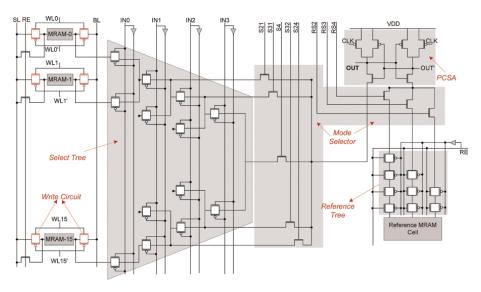

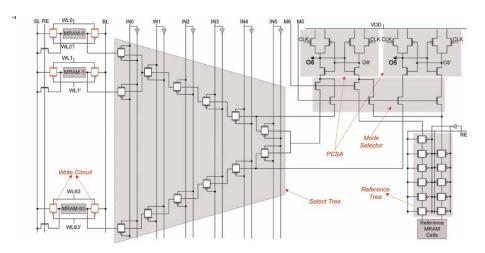

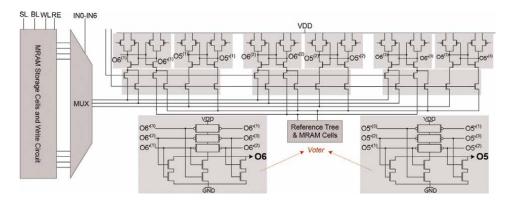

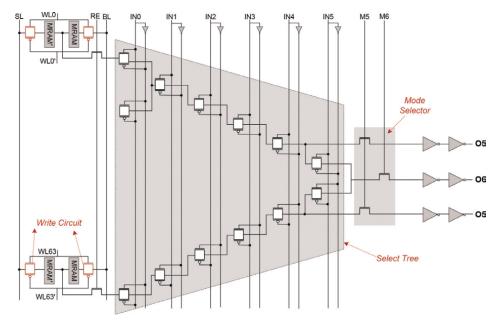

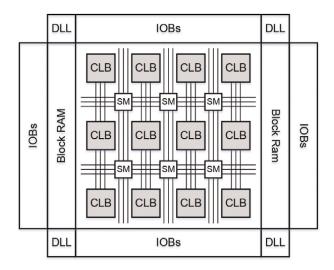

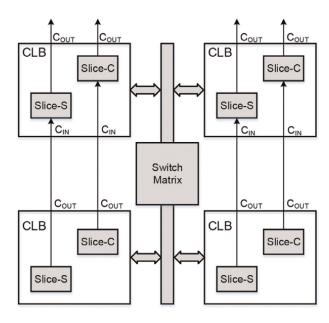

The read is preceded by a precharge operation, wherein the BL is precharged to Vcc. During the read operation, with '0' being stored in the bitcell, the BL discharges through A2, with the WWL turned ON and the difference in voltage between BL and BL' is measured using a sense amplifier, that is sensitive to voltage differences as low as 100 mV [7, 8] in the modern-day SRAM design. The sense amplifier is typically realized by another cross-coupled inverter design, that is designed to offer precise outputs even in the presence of process variations, often leading to design complexity/ overhead. The design constraint during the read operation is that the NMOS transistor should be strong enough to hold the DATA node at '0' even though BL attempts to write a '1' through the access transistor A2.